Low-on-resistance SGT preparation method, semiconductor device and equipment

A low on-resistance, conductive plug technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc. Difficult to eliminate, main on-resistance reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

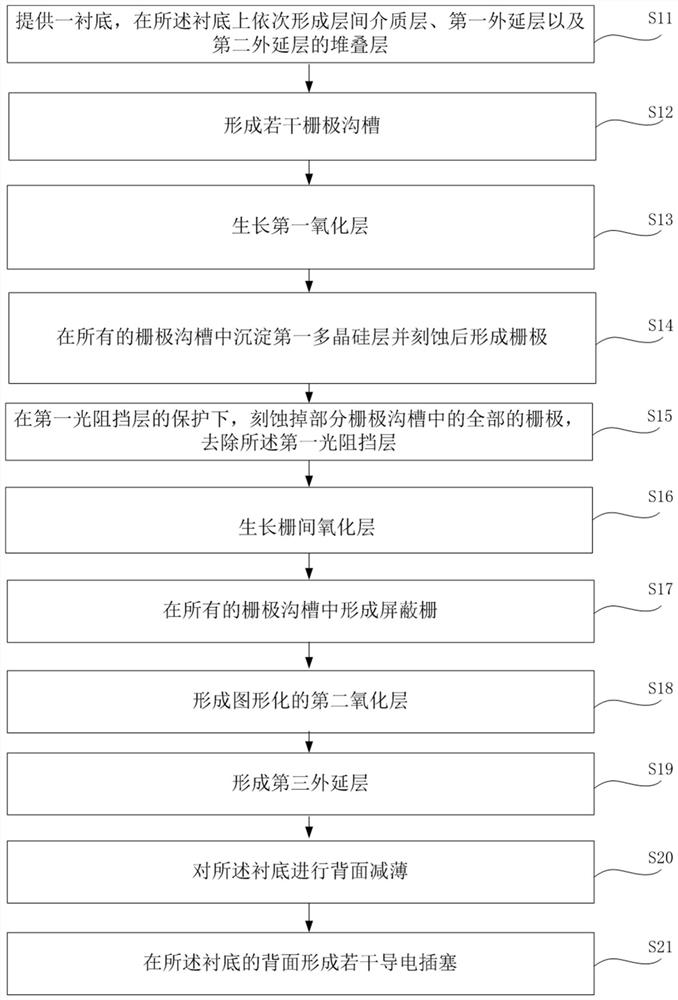

[0064] The preparation technology of prior art SGT product is:

[0065] growing an epitaxial layer on a substrate;

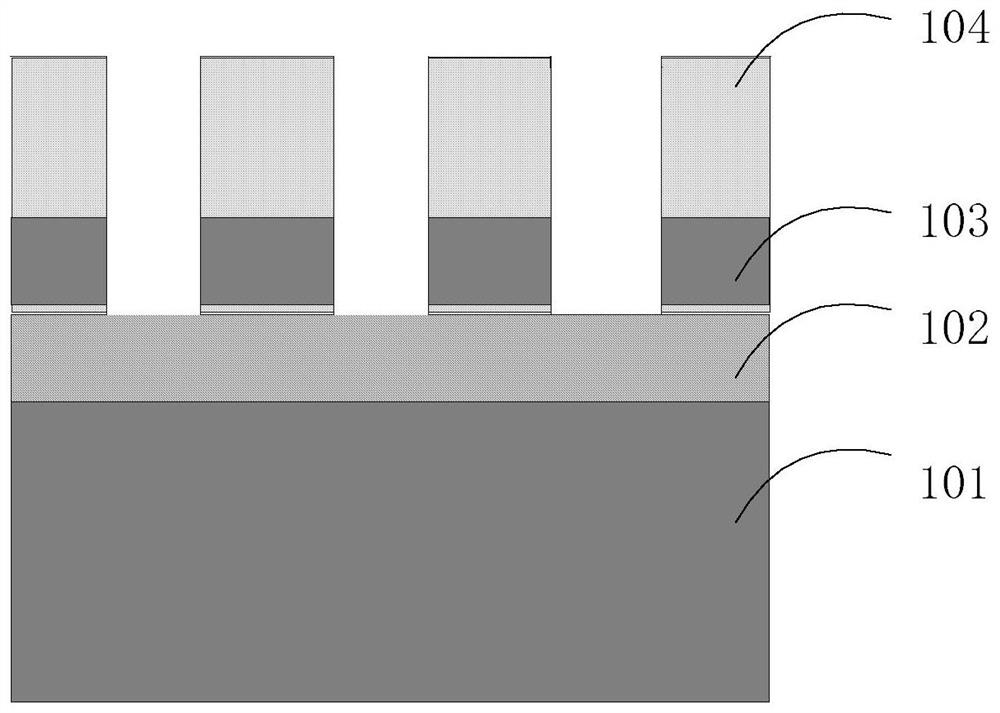

[0066] A hard mask layer and a photoresist are sequentially deposited on the substrate, the photoresist is patterned, and the hard mask layer is etched using the patterned photoresist as a mask to form a patterned hard mask layer for patterning The hard mask layer is a mask to etch the epitaxial layer, remove the photoresist, and form a gate trench;

[0067] growing an oxide layer on the surface of the substrate and in the gate trench, and then forming a shielding gate, an oxide layer between gates and a gate in the gate trench in sequence;

[0068] Implanting P-type ions and N-type ions in the epitaxial layer around the gate to form source and well regions;

[0069] Deposit an interlayer dielectric layer on the surface of the epitaxial layer and the top of the gate, coat photoresist on the surface of the interlayer dielectric layer, pattern the photoresist, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com