Wiring structure and method for wafer substrate standard integration area suitable for on-chip integration

A technology of wiring structure and integration area, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of non-guarantee and high yield, and achieve the effect of improving compatibility and improving production yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The specific embodiments of the present invention will be described in detail below with reference to the accompanying drawings. It should be understood that the specific embodiments described herein are only used to illustrate and explain the present invention, but not to limit the present invention.

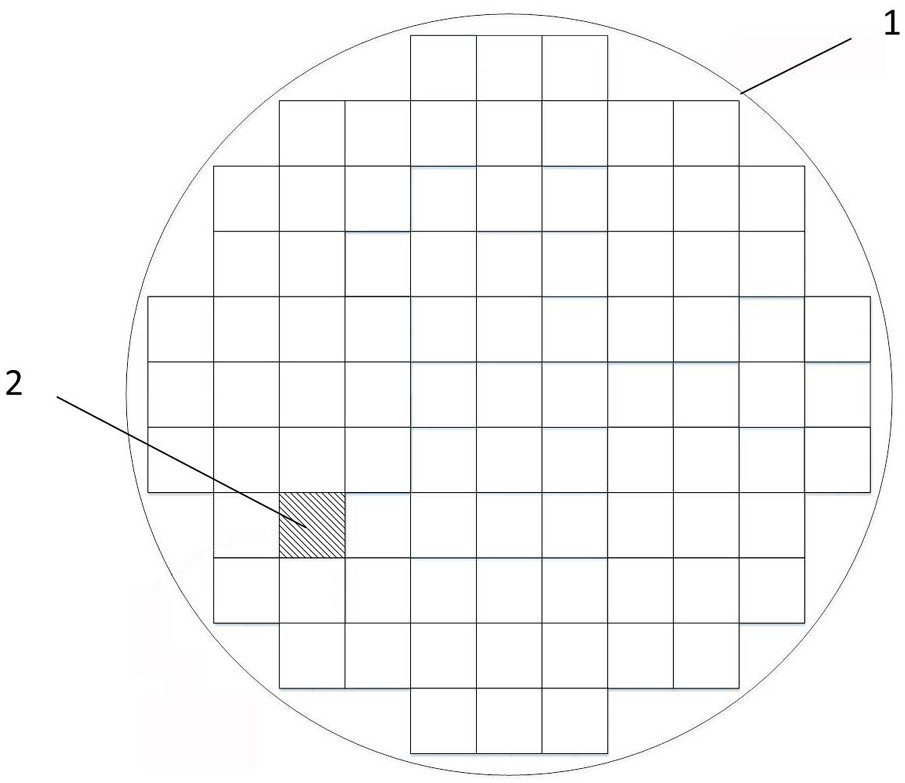

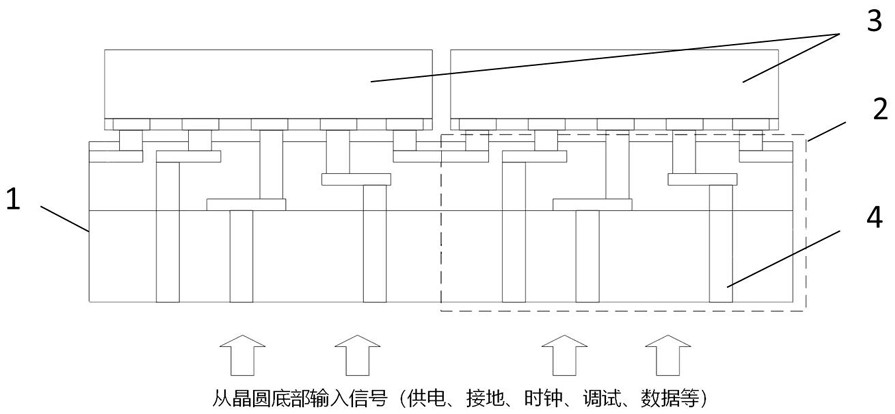

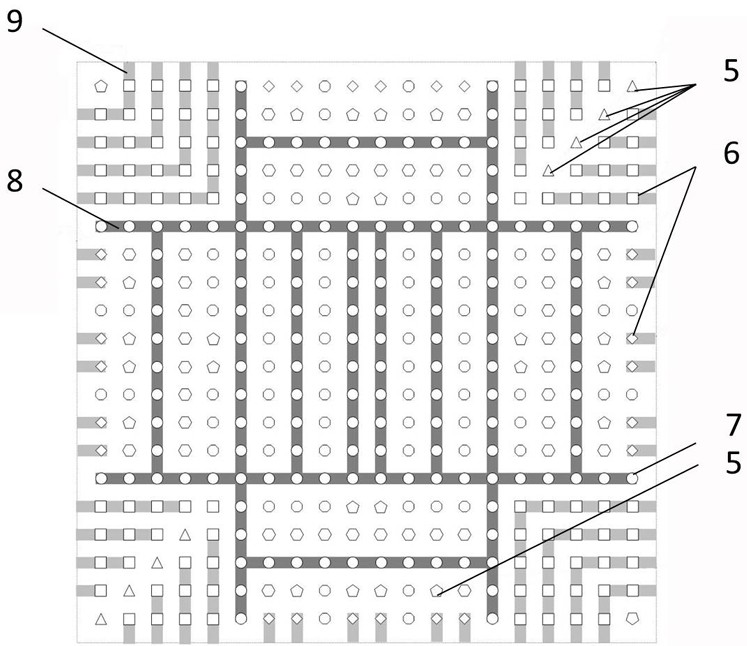

[0047]Wafer substrate standard integrated area wiring structure suitable for on-chip integration, such as figure 1 , figure 2 As shown, an area is divided on the wafer substrate 1 as a standard integrated area 2. The standard integrated area 2 is provided with pins upward, and an on-chip wiring network is constructed by connecting the pins. Each standard integrated area includes three metal layers, such as Figure 3 to Figure 5 As shown, the top metal layer includes core voltage pins 7, interconnection signal pins 6 and complex function pins 5, the middle metal layer includes clock signal pins 10, and the bottom metal layer includes ground pins 12;

[0048] Connect th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More