Structure and circuit of logarithmic skip adder

A circuit structure, adder technology, applied in circuits, instruments, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0080] A further description will be given below in conjunction with embodiments.

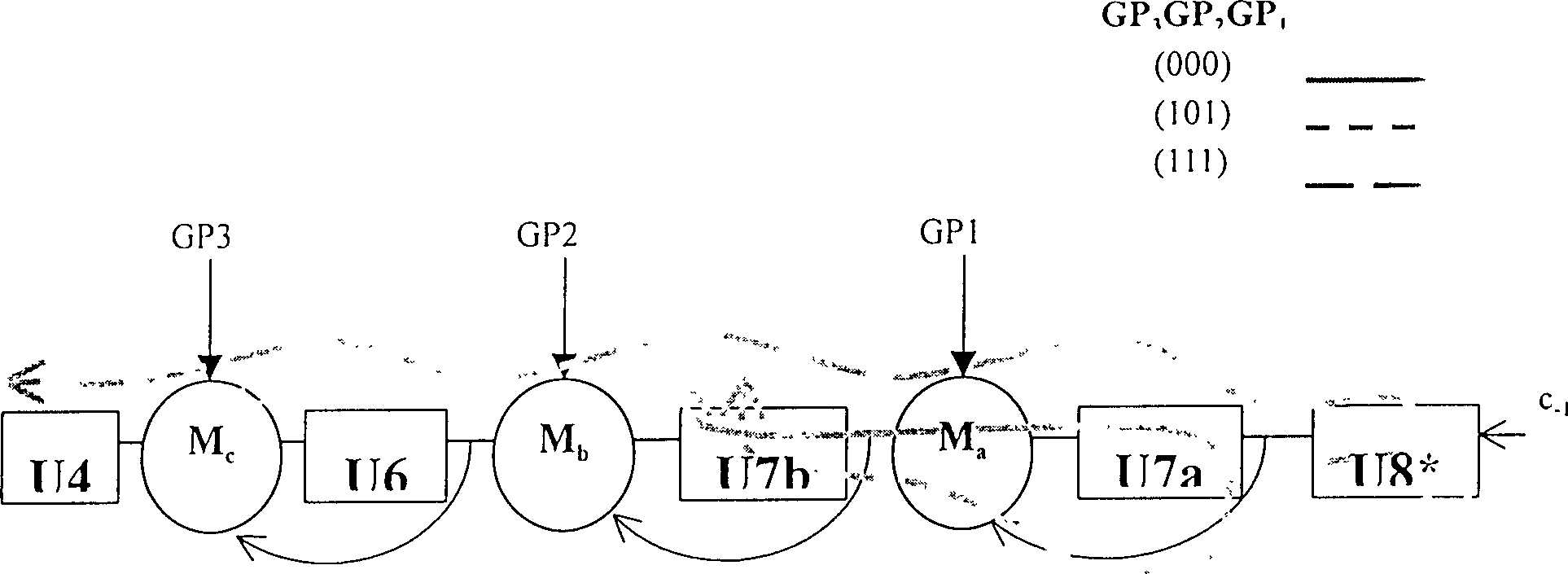

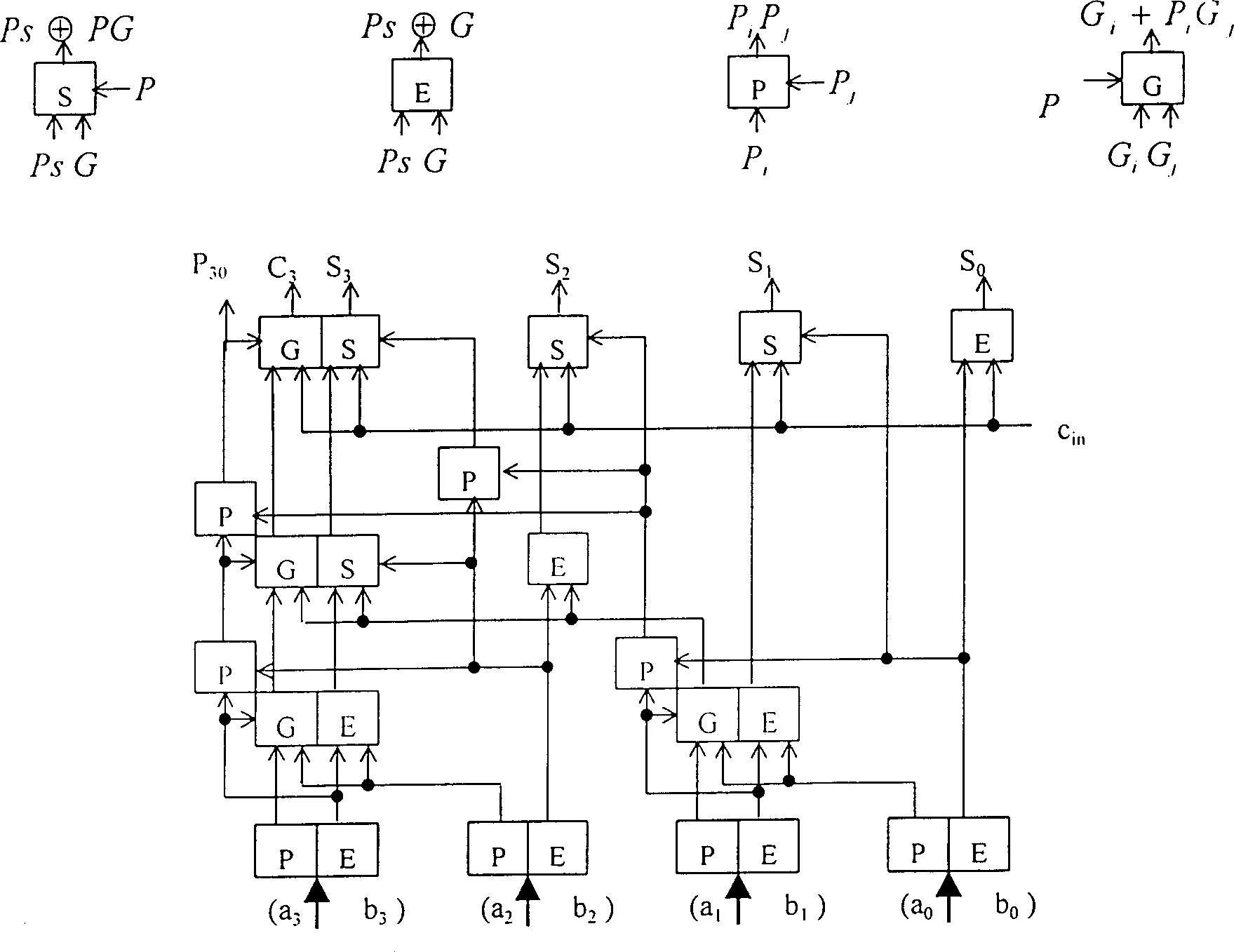

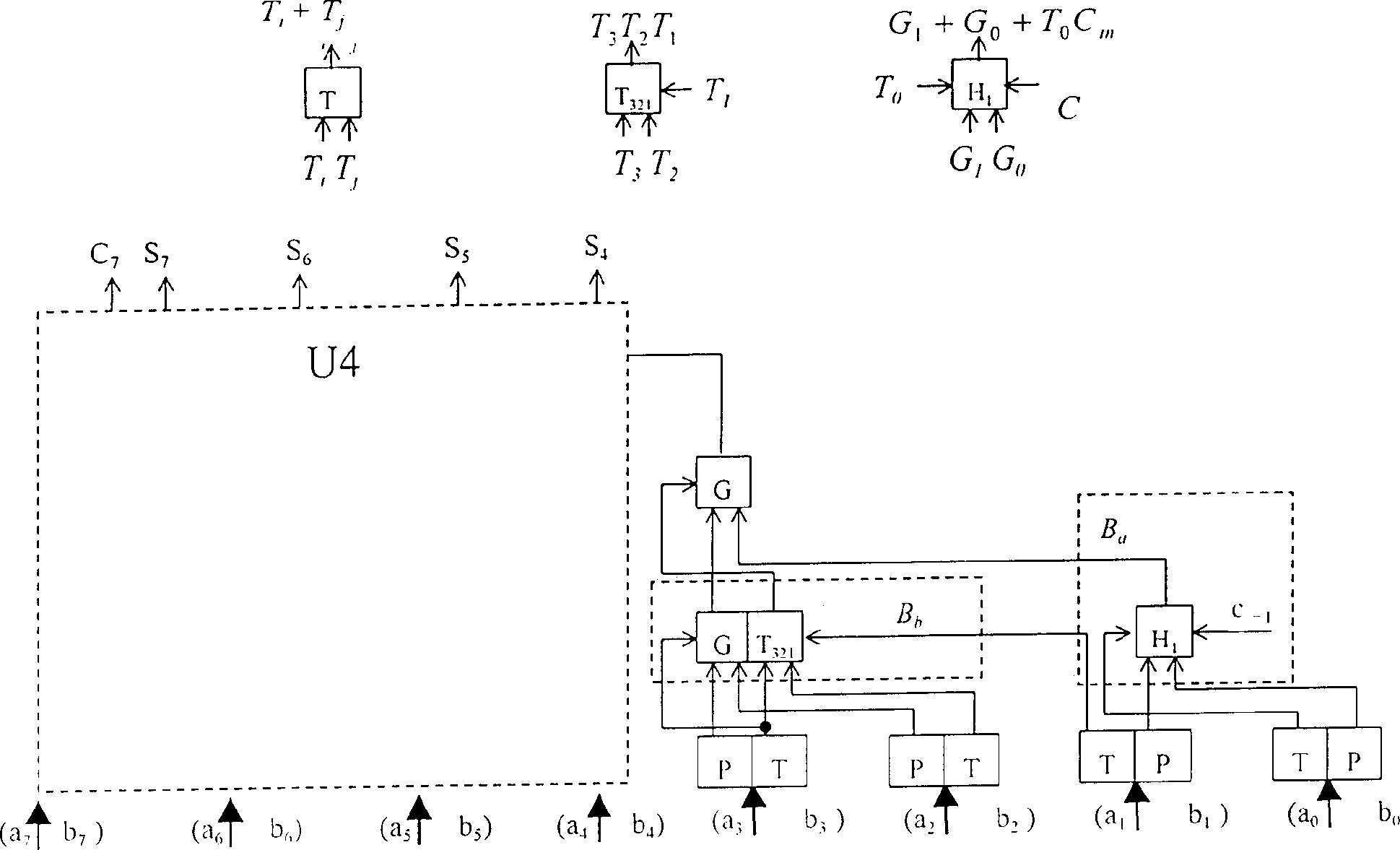

[0081] figure 1 It is a 32-bit adder structure. This structure divides the 32 bits into 5 groups. The carry jump algorithm is used between the groups, and the ELM tree addition structure is used in the group to make the carry transfer within the group parallel. The logic level of the critical path and the number of bits in the group are logarithmic relationship. This overcomes the speed limitation caused by the serial carry in the traditional carry skip adder group. The ELM structure of each group is as figure 2 , image 3 , Figure 4 , Figure 5 Shown.

[0082] Compared with other tree structures, the ELM adder embeds the summation logic into the tree structure, so that after getting the previous stage carry, only one logic gate delay is required to obtain the sum of each bit and the next stage carry. For other tree structures, the local carry must be obtained first, and then the local sum is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More