High density semiconductor memory having diagonal bit lines and dual word lines

A memory and semiconductor technology, applied in semiconductor devices, digital memory information, semiconductor/solid-state device manufacturing, etc., can solve the problem of wasting chip area and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

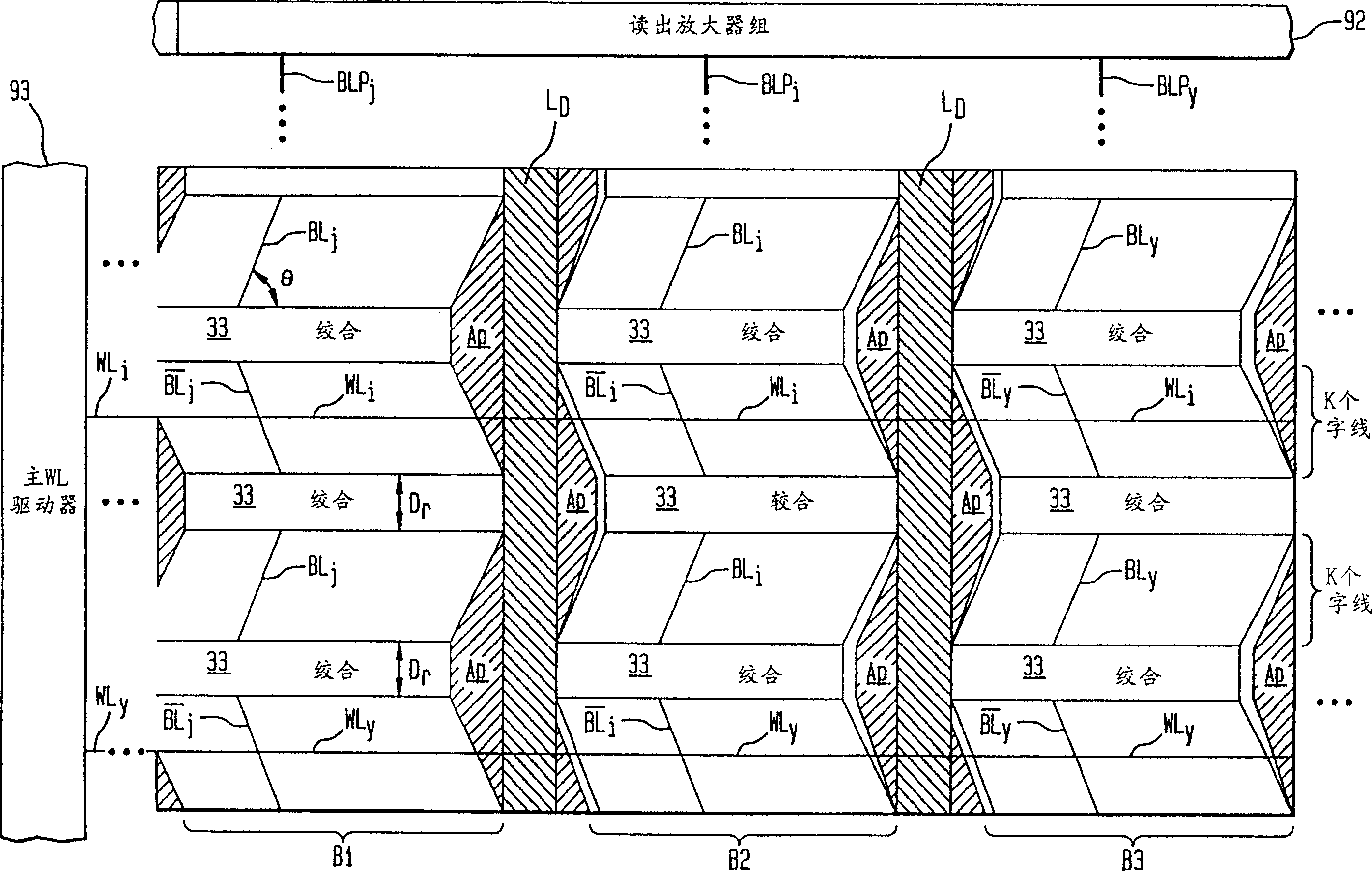

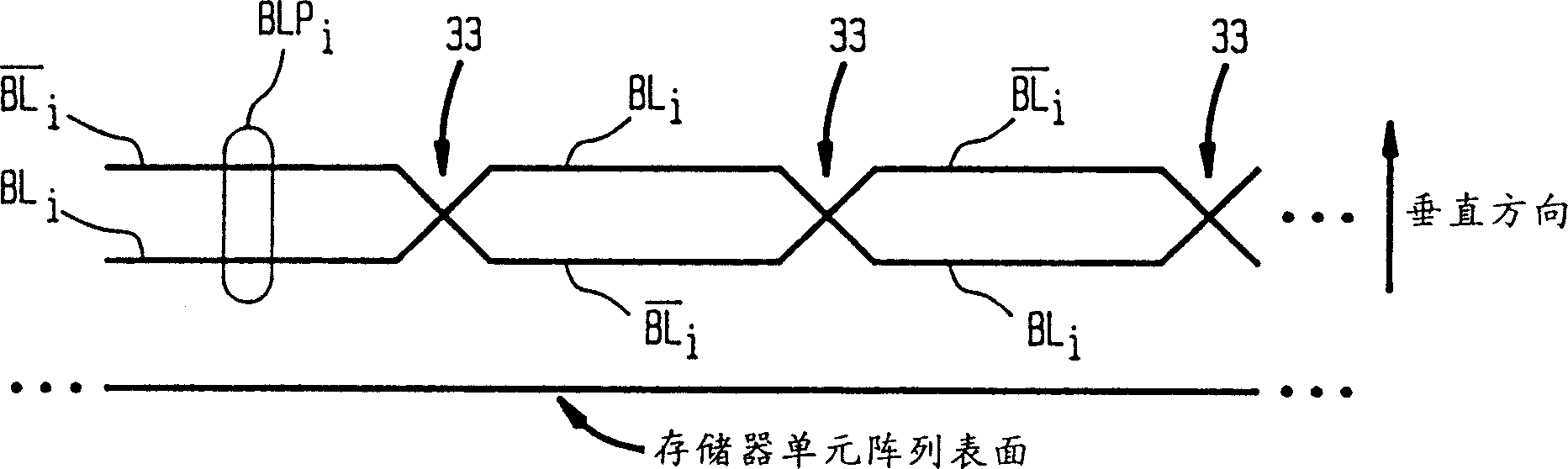

[0025] The present invention relates to a space efficient high density semiconductor memory using diagonal bit lines and double word lines having a space efficient structure. The present invention provides a method to substantially eliminate the area penalty associated with diagonal bitline memory. For purposes of discussion, exemplary embodiments of the present invention are described herein in the context of a DRAM chip. However, the invention has wider application. The invention is applicable to other memories such as EDO-DRAM, SDRAM, RAMBUS-DRAM, MDRAM, SRAM, Flash-RAM, EPROM, EEPROM or mask ROM or merged DRAM-logic (embedded DRAM), to name a few. Such devices may be used, for example, in consumer products such as computer systems, cellular telephones, personal digital assistants (PDAs), and other electronic products.

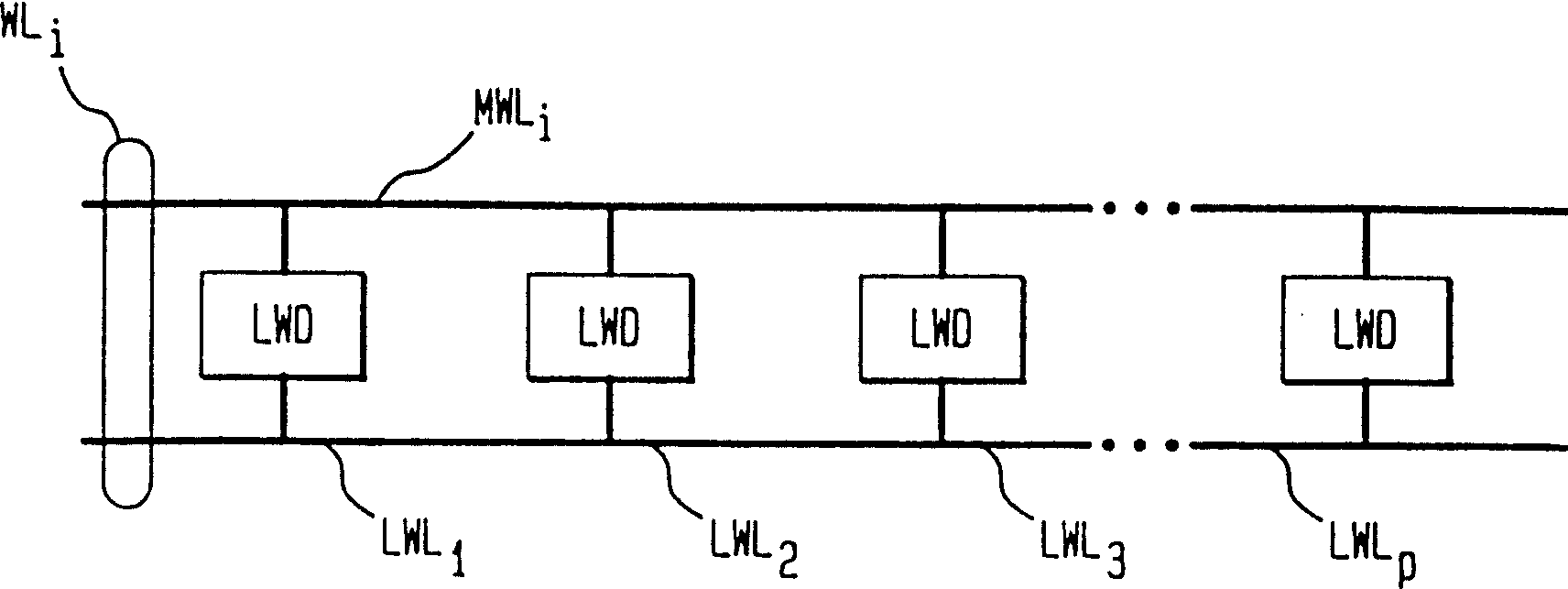

[0026] now for reference image 3, a simplified schematic block diagram of an embodiment of the present invention designated as DRAM 10 is shown here. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com