Method for defining parallel dual butterfly computation fast Fourier transform processor structure

A Fourier transform and parallel processing technology, applied in the information field, can solve problems such as high clock frequency, increased addressing complexity, and complex multiplier consumption and occupation, so as to improve computing speed, solve computing speed and hardware consumption volume effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

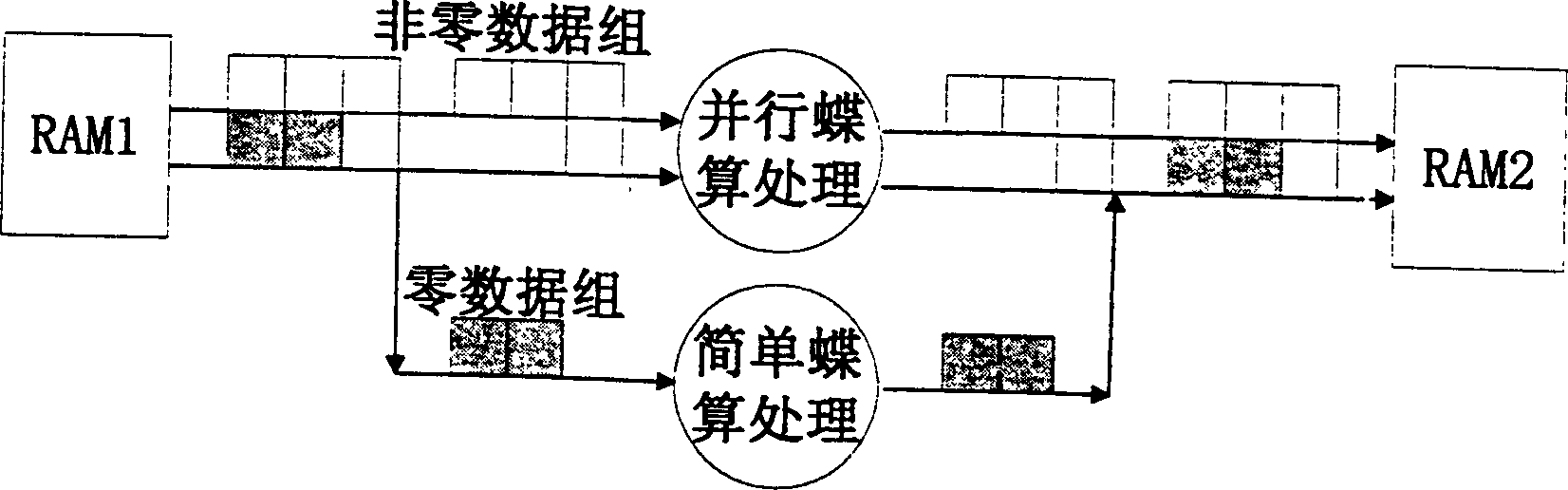

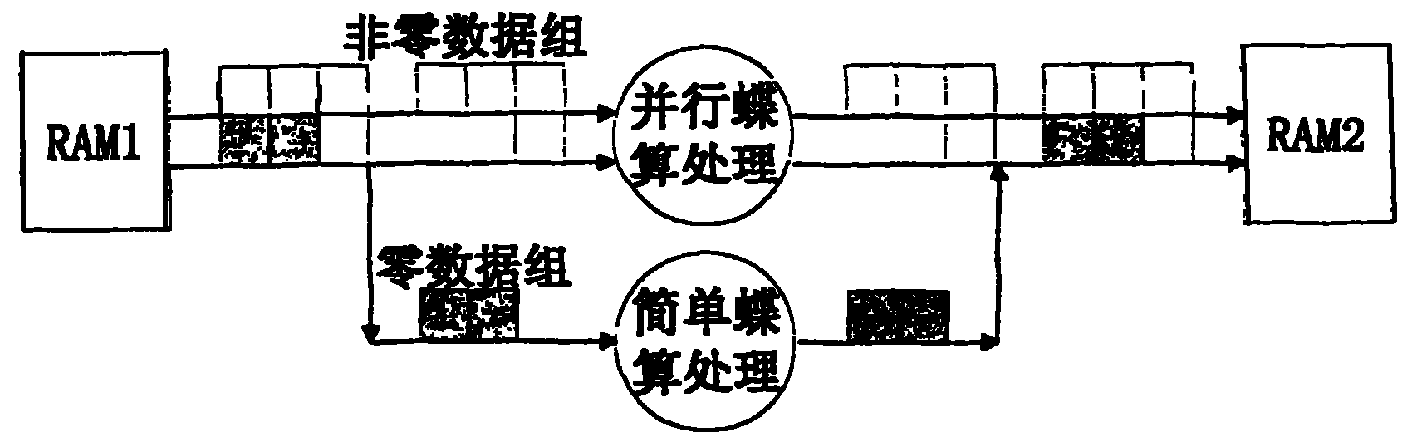

[0026] Such as figure 1 Shown, provide following embodiment in conjunction with content of the present invention:

[0027] The method of the present invention is used for the design of 64 FFT processors in the wireless local area network standard IEEE 802.11a, and with the time parameter (t in IEEE 802.11a FFT =3.2μs) as standard.

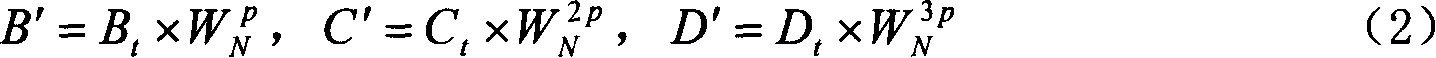

[0028] The first step is to perform parallel butterfly calculation processing. The 64-point radix-four frequency extraction FFT processor is divided into 3 stages, each stage processes 64 data, and each butterfly operation processes 3 clocks to read 4 data, and the number of clocks consumed by each stage is n one_stge =64 / 4×3+12=60 clocks, the total number of clocks consumed by a 64-point FFT process is n FFT =n one_stage ×3=60×3=180 clocks. If a 60MHz system clock is used, it takes 180 / 60MHz=3μs<3.2μs for a 64-point FFT processor to complete a process. By adopting parallel butterfly calculation processing, the obtained FFT processor has been...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More