Method for lowering resistance value of cobalt disilicide layer of semiconductor devices

A technology of cobalt disilicide layer and cobalt silicide layer, which is applied in the manufacture of semiconductor/solid-state devices, circuits, electrical components, etc., and can solve the problems of component performance impact, increasing the resistance value of cobalt disilicide layer 23, leakage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

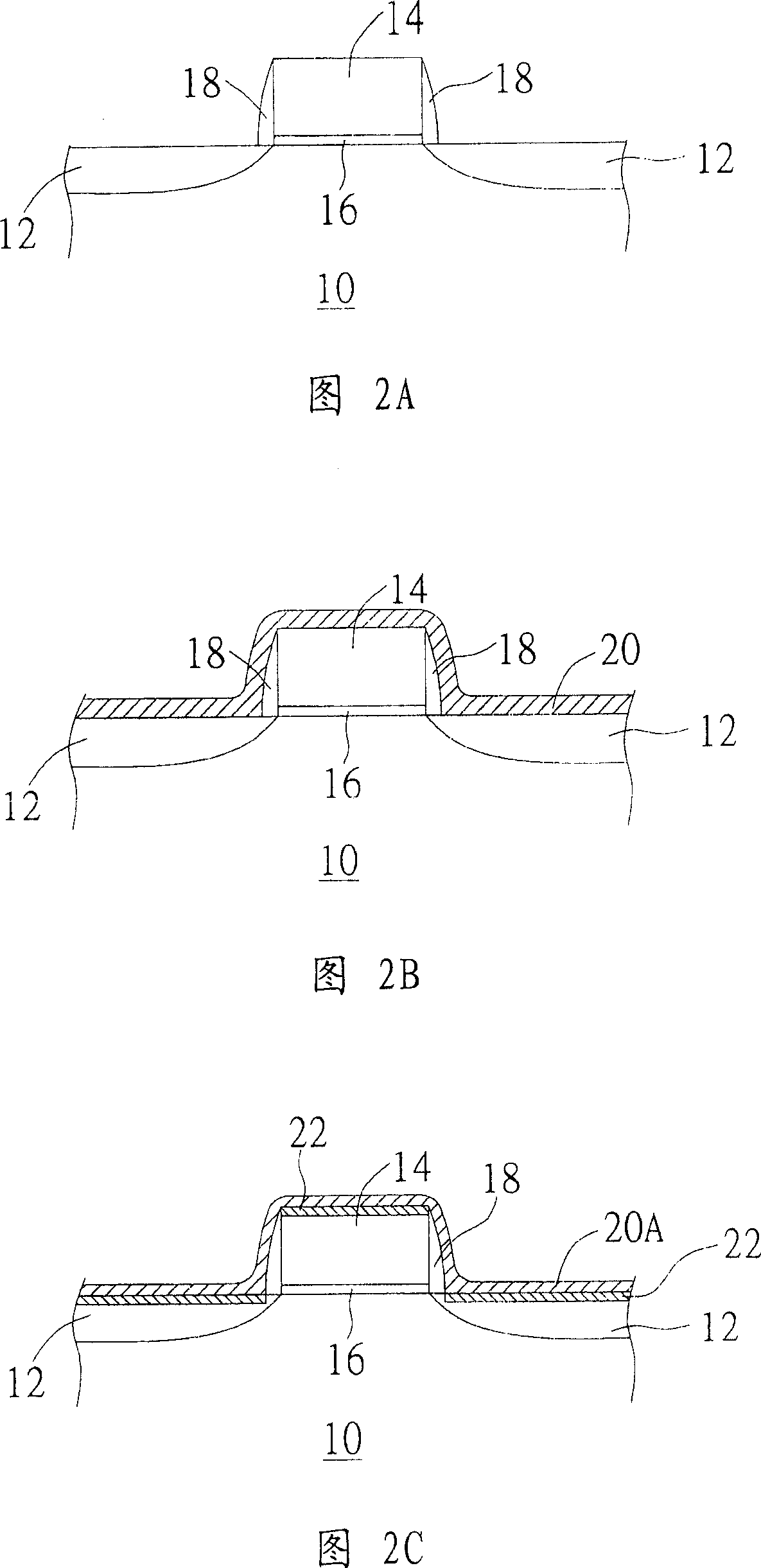

[0026] Referring to FIGS. 2A to 2E , which illustrate a manufacturing method for reducing the resistance value of a cobalt disilicide layer in a semiconductor device according to a preferred embodiment of the present invention. As shown in FIG. 2A, a silicon substrate 10 is provided first. Source / drain regions 12 are conventionally formed on the silicon substrate 10 to define a channel region. The gate 14 is mainly made of polysilicon, and is formed in the channel region and located above a gate oxide layer 16 . The sidewall buffer layer 18 is made of silicon oxide, for example, and can be formed on both sidewalls of the gate 14 .

[0027] Next, as shown in FIG. 2B , a metal cobalt layer 20 is formed on the silicon substrate 10 , and the metal cobalt layer 20 covers the gate 14 . The metal cobalt layer can be formed by sputtering. Thereafter, a layer of titanium or titanium nitride may be deposited on top of the metallic cobalt layer 20 (not shown) to protect the metallic c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More