Method for forming metal-insulator-metal capacitance

A technology of metal capacitors and insulators, used in circuits, electrical components, semiconductor/solid-state device manufacturing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

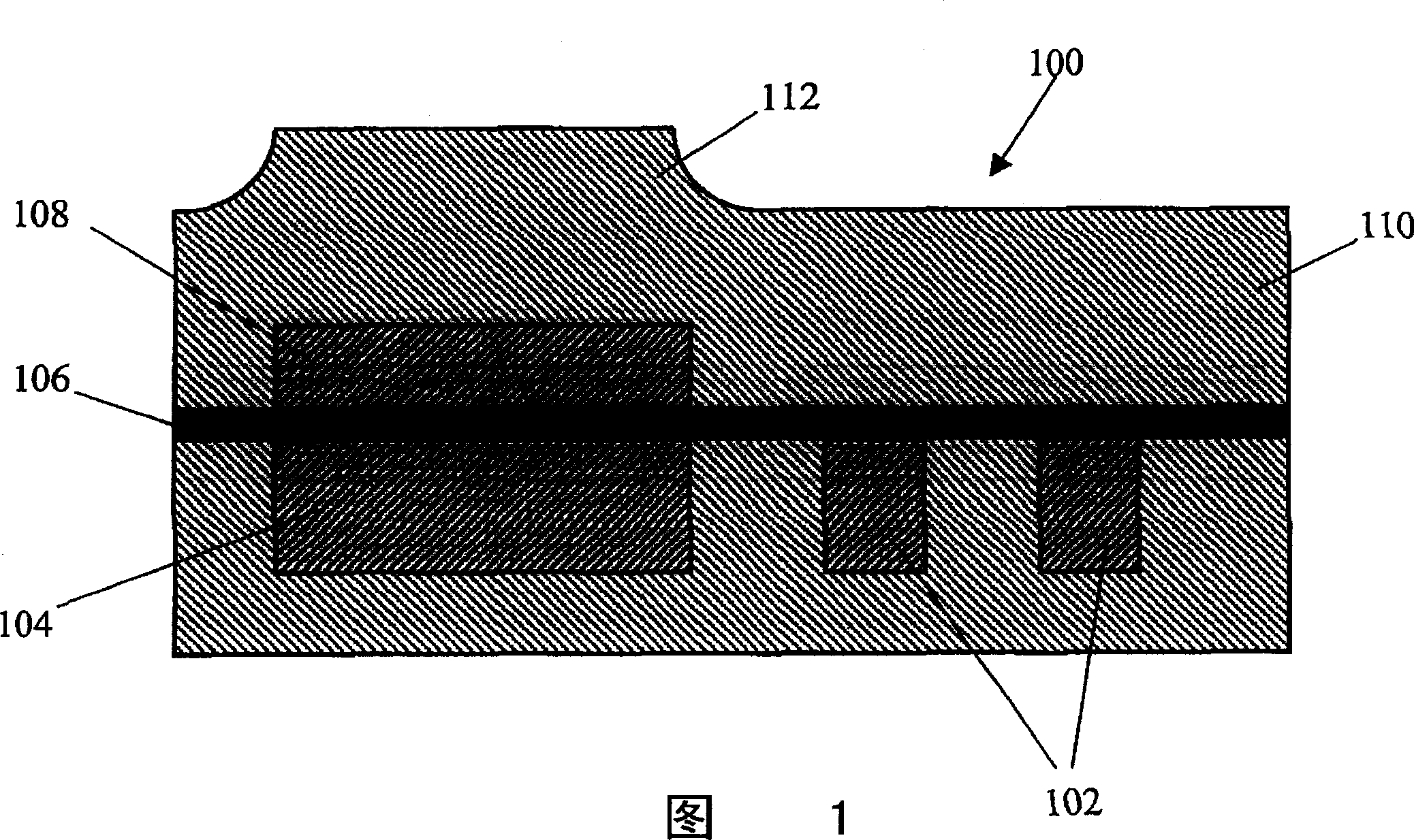

[0011] FIG. 1 shows a common parallel plate metal-insulator-metal capacitor structure 100 in the known art, wherein 102 represents the general copper wiring, 104 represents the copper bottom plate used as the lower plate of the capacitor, 106 represents the dielectric layer, and 108 represents The aluminum top plate, which acts as the upper plate of the capacitor, and 110 represent the interlayer dielectric. The process of this known technology requires cumbersome steps of barrier deposition, aluminum deposition, and aluminum patterning. In addition, due to the process of using the known technology, a surface topography (topography) 112 is inevitably created, which will make the damascene process of the next wiring layer more difficult to perform, and requires adding a chemical mechanical process before the patterning step. A polishing (CMP) step to planarize the surface of the dielectric layer.

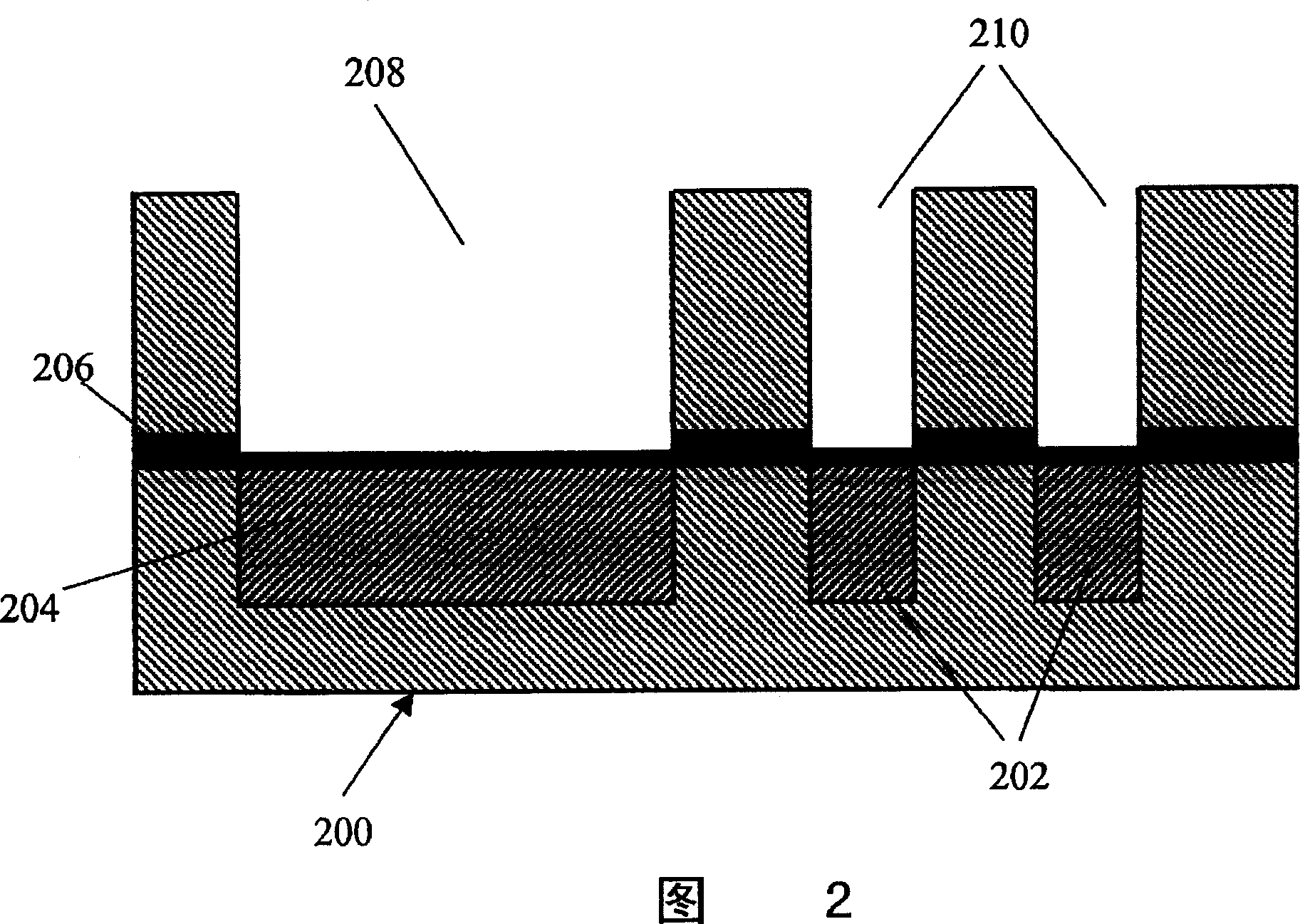

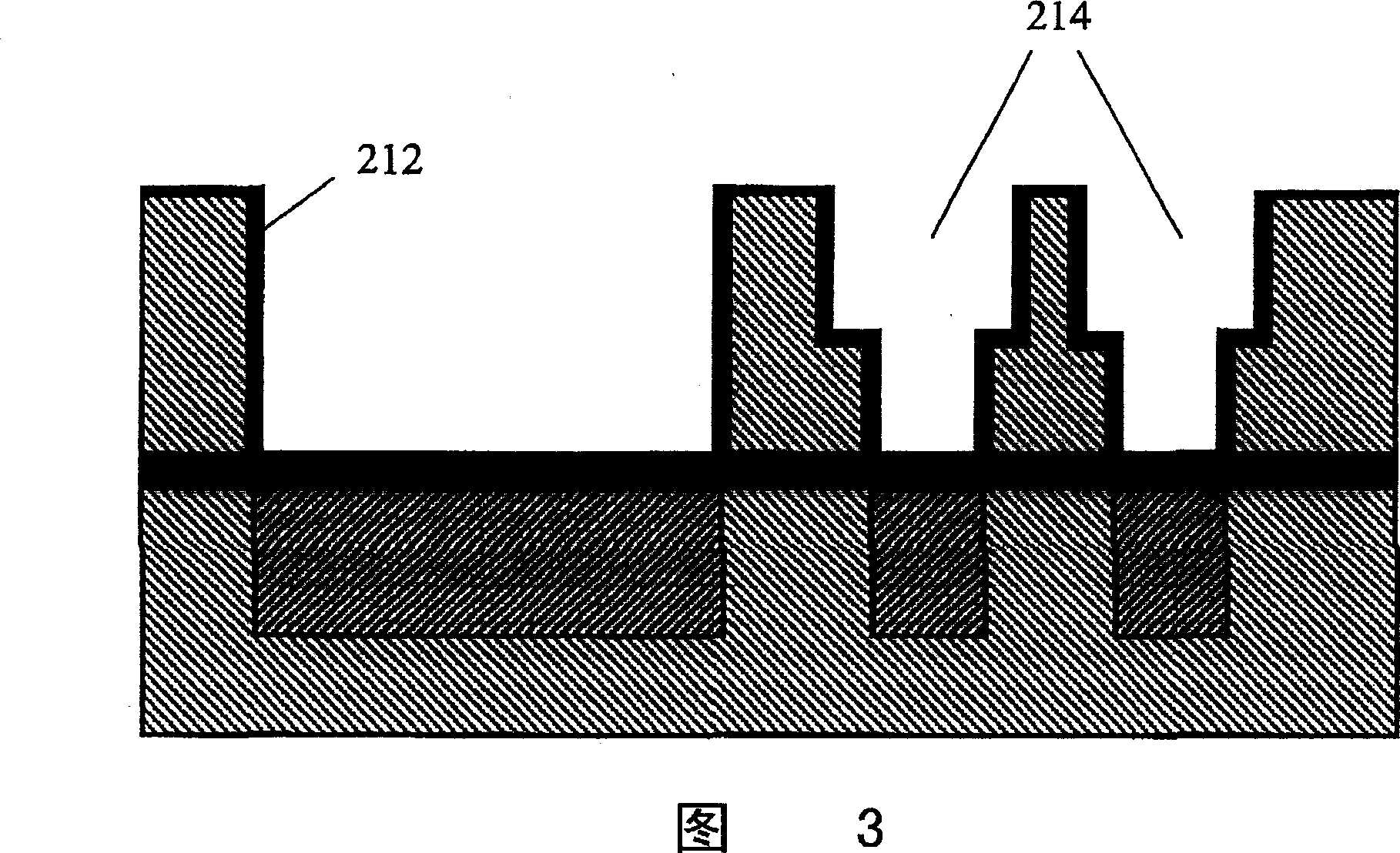

[0012] The method for forming a metal-insulator-metal capacitor of the present ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More