Interconnection structure containing stress regulating covering and its mfg. method

A technology of interconnect structure and stress adjustment, which can be used in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., and can solve problems such as poor adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

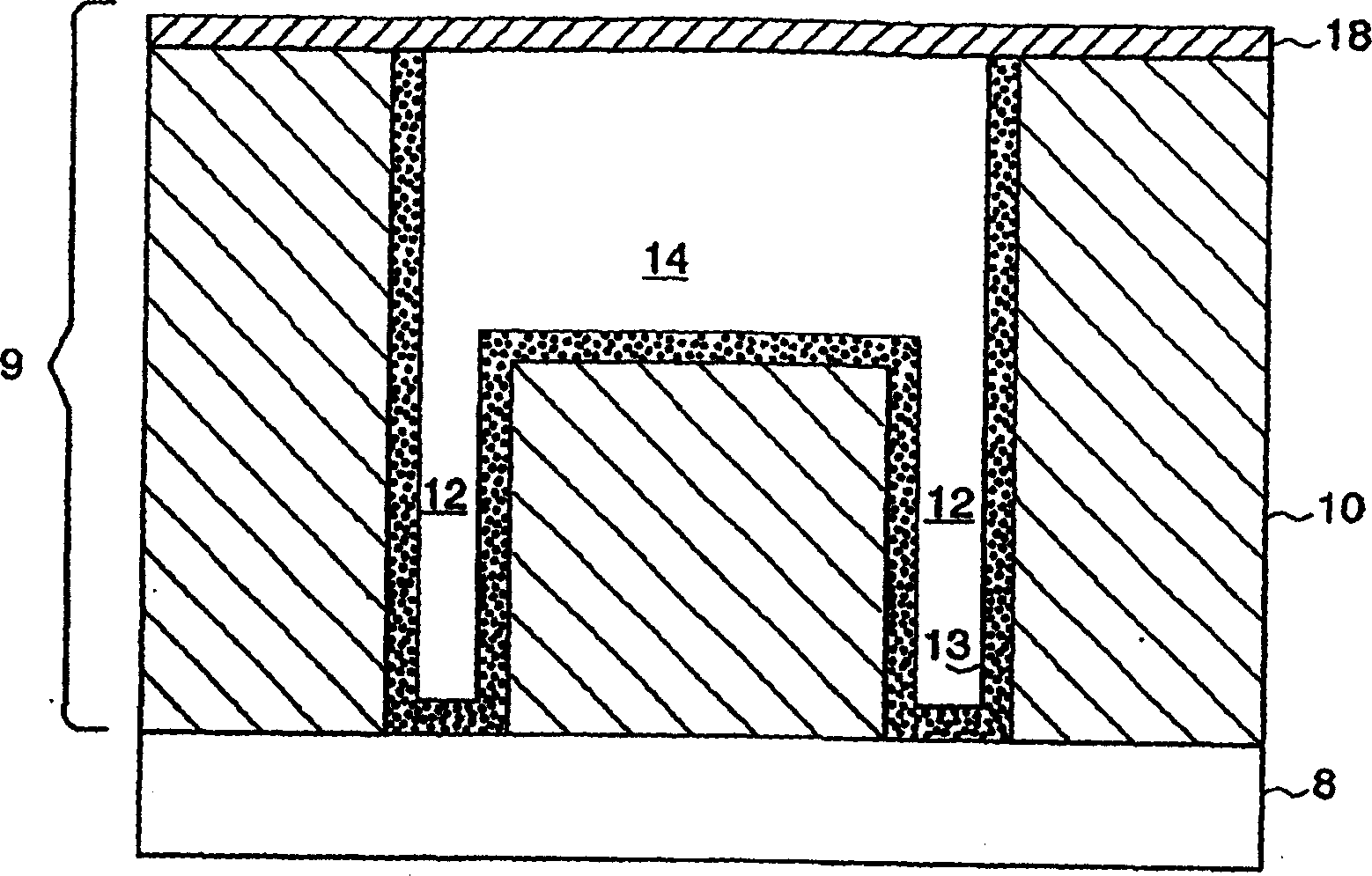

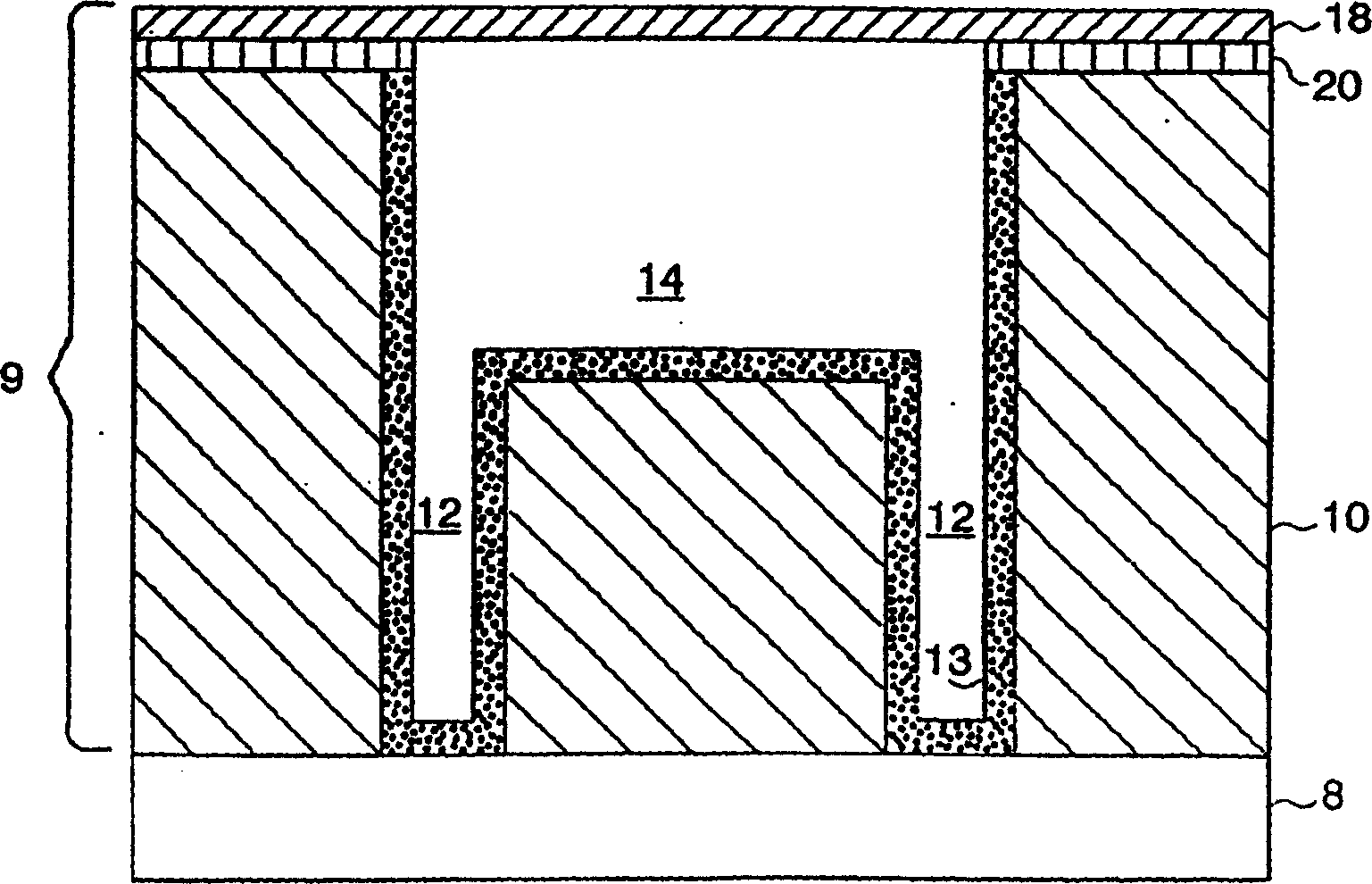

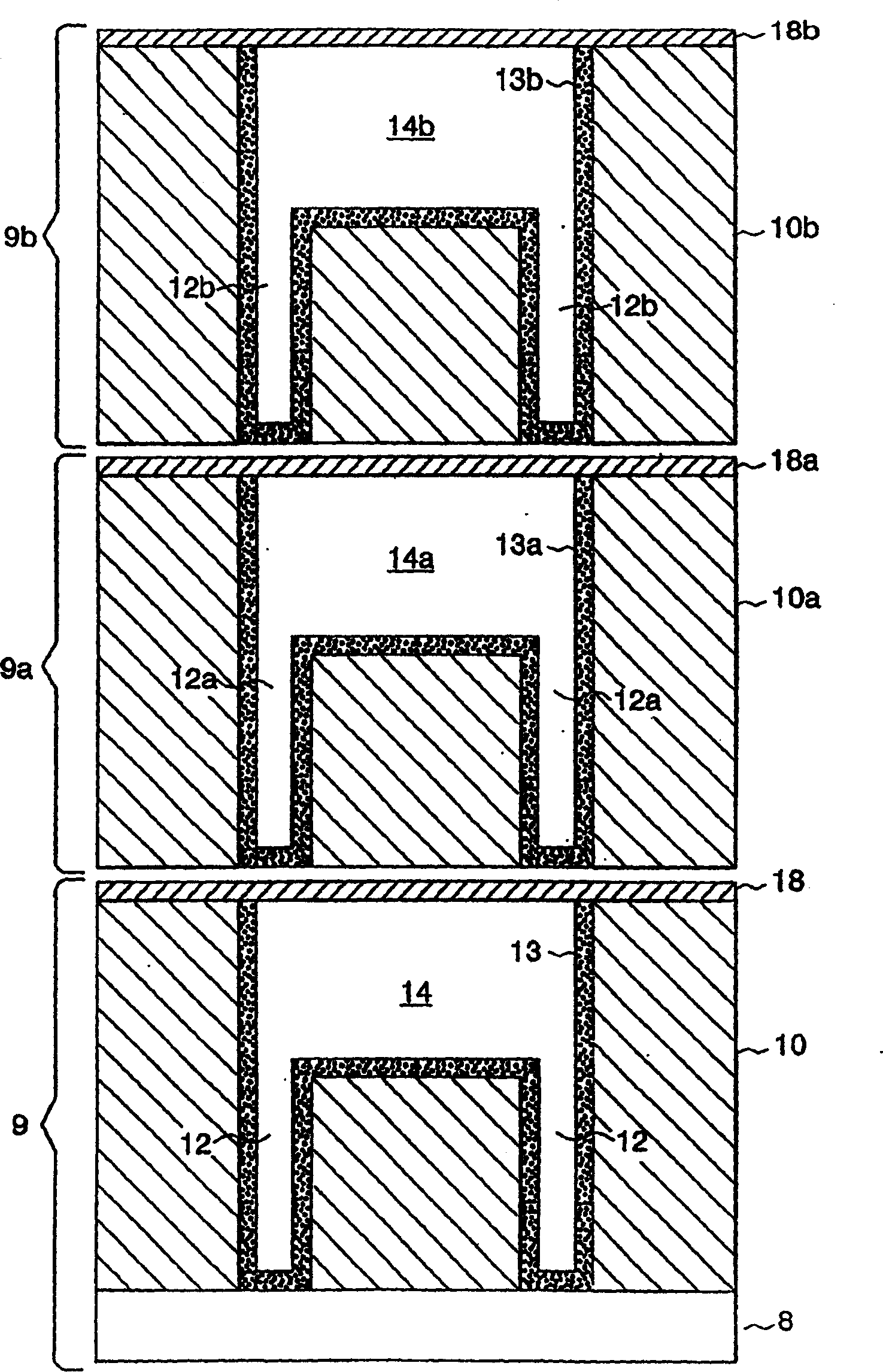

[0024] The present invention is directed to an interconnection structure for forming a semiconductor device, by employing a stress-regulating capping layer between a first layer having an associated first internal stress and a second layer having an associated second internal stress, the The interconnect structure has greatly reduced internal stress. Typically, the first internal stress associated with the first layer is a tensile stress, and the second internal stress associated with the second layer is either tensile or compressive, depending on the particular material selected for the second layer. The interconnection structure of the present invention is based on the surprising discovery that when specific materials are chosen for the first and second levels, the stresses of the respective materials enable stress modulation with an associated specific stress (i.e., tensile or compressive stress). Covering materials can be chosen to substantially reduce the overall internal...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thermal expansion coefficient | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More