Flash memory cells and fabrication process thereof

A technology of flash memory unit and control gate, which is applied in semiconductor/solid-state device manufacturing, electrical components, information storage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

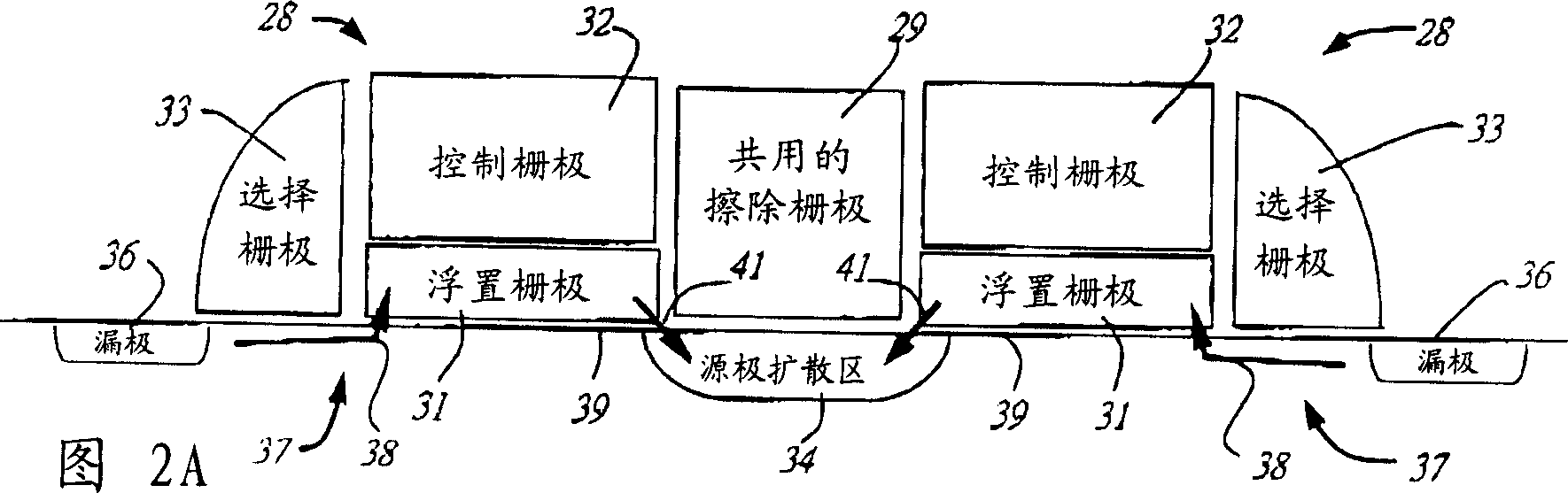

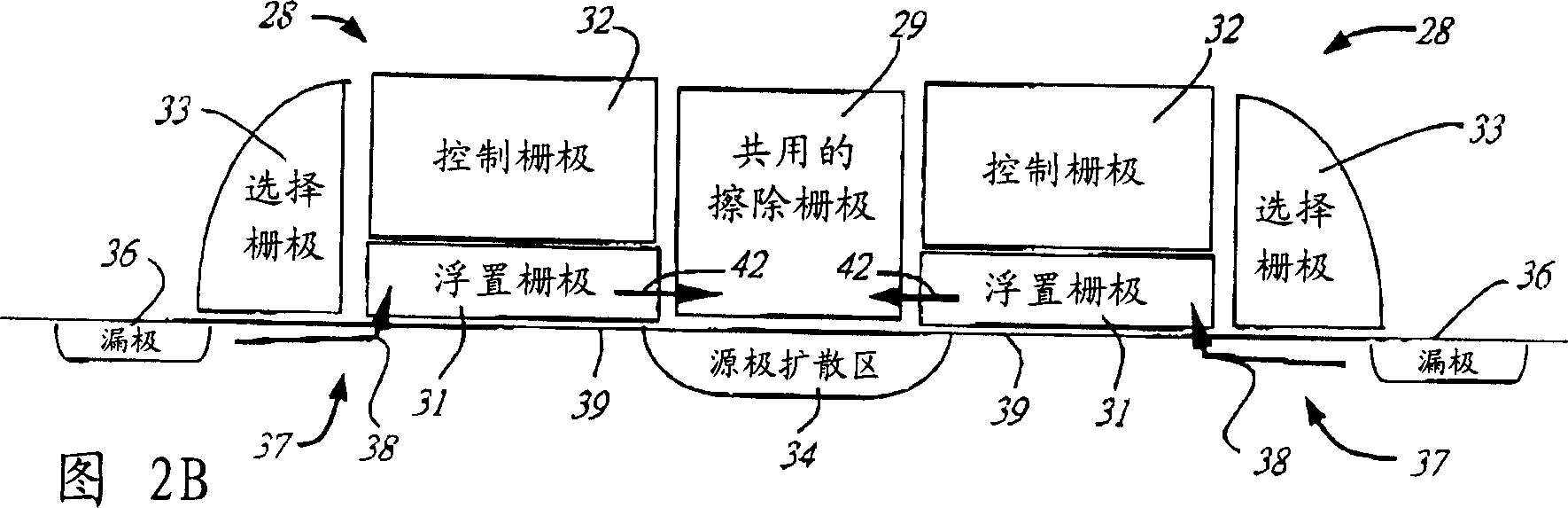

[0021] In the embodiment of FIGS. 2A and 2B , two memory cells 28 share a common erase gate 29 . Each cell has a vertically stacked self-aligned floating gate 31 and a control gate 32, the floating gate 31 is relatively thin (eg, 100 Å to 700 Å) and the control gate 32 is located above the floating gate . Each cell also has a select gate 33 on one side of the stacked floating and control gates. The select and erase gates are formed simultaneously from a polysilicon layer deposited across the entire wafer and then etched anisotropically in a dry etching process.

[0022] Source and drain diffusion regions 34 and 36 are formed in the substrate, the source regions extending under edge portions of the erase gate and the floating gate. The drain region extends under an edge portion of the select gate opposite the stacked gate and is shared with a select gate in an adjacent cell (not shown).

[0023] In these embodiments, programming occurs in the central channel region 37 betwee...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More