Semiconductor memory device

A semiconductor and device technology, applied in the field of semiconductor memory devices, can solve problems such as increased power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Preferred embodiments of the present invention, examples of which are illustrated in the accompanying drawings, will now be described in detail.

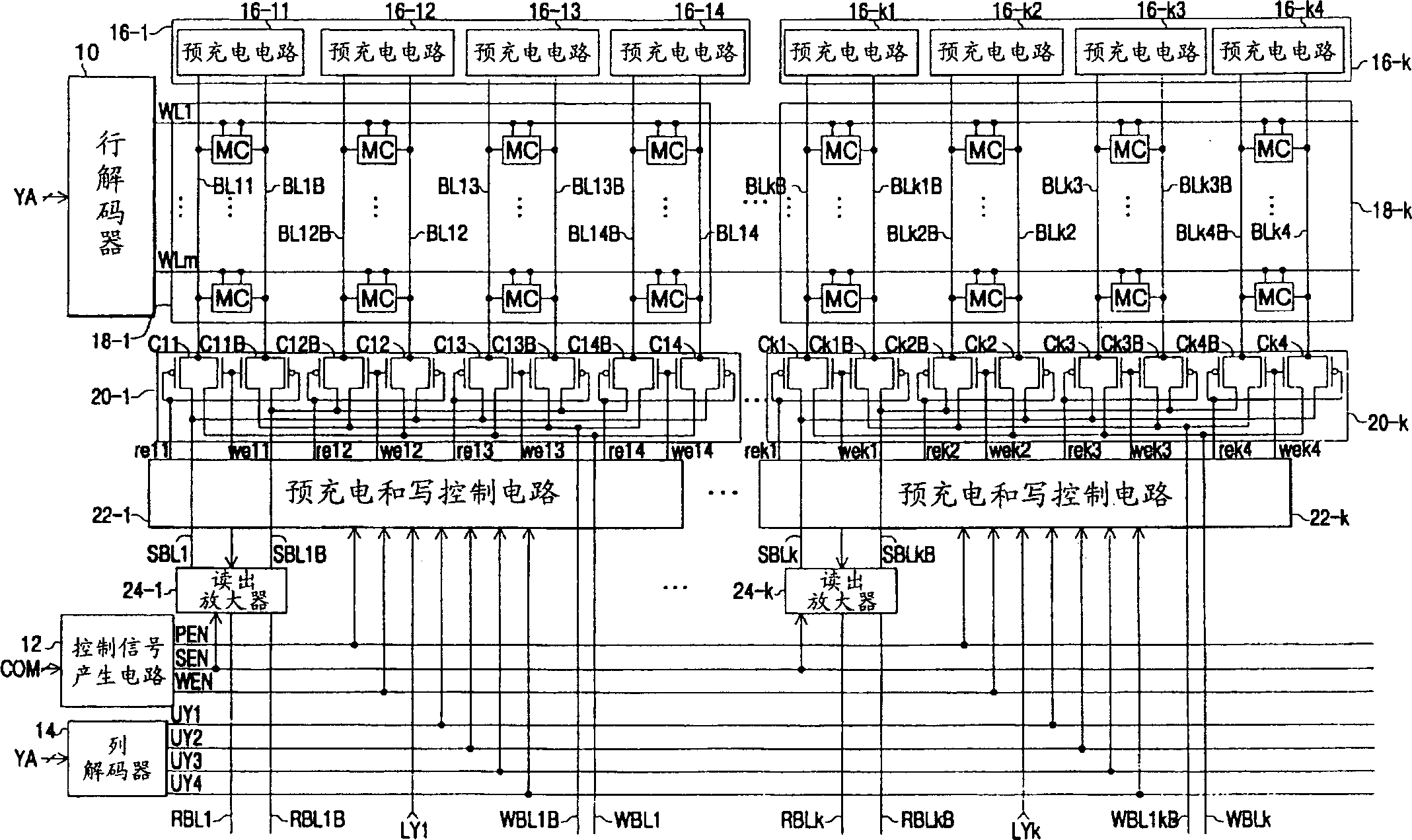

[0020] figure 1 is a block diagram of an example conventional semiconductor memory device. figure 1 The semiconductor memory device includes a row decoder 10, a control signal generation circuit 12, a column decoder 14, precharge circuits 16-1 to 16-k, memory cell array blocks 18-1 to 18-k, a column selection circuit 20-1 to 20-k, precharge and write control circuits 22-1 to 22-k, and sense amplifiers 24-1 to 24-k.

[0021] exist figure 1 Among them, each of the precharge circuits 16-1 to 16-k includes a precharge circuit for precharging the bit line pairs (BL11, BL11B) to (BL14, BL14B) to (BLk1, BLk1B) to (BLk4, BLk4B). Circuits (16-11~16-14) to (16-k1~16-k4). Each of the memory cell array blocks 18-1 to 18-k includes word lines WL1 to WLm and bit line pairs (BL11, BL11B) to (BL14, BL14B) to (BLk1, BLk1B) to (BLk4, BLk4B...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com