Non-volatile memory location and producing method thereof

A technology of non-volatile storage and manufacturing method, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., to achieve the effects of increasing component integration, increasing effective channel length, and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

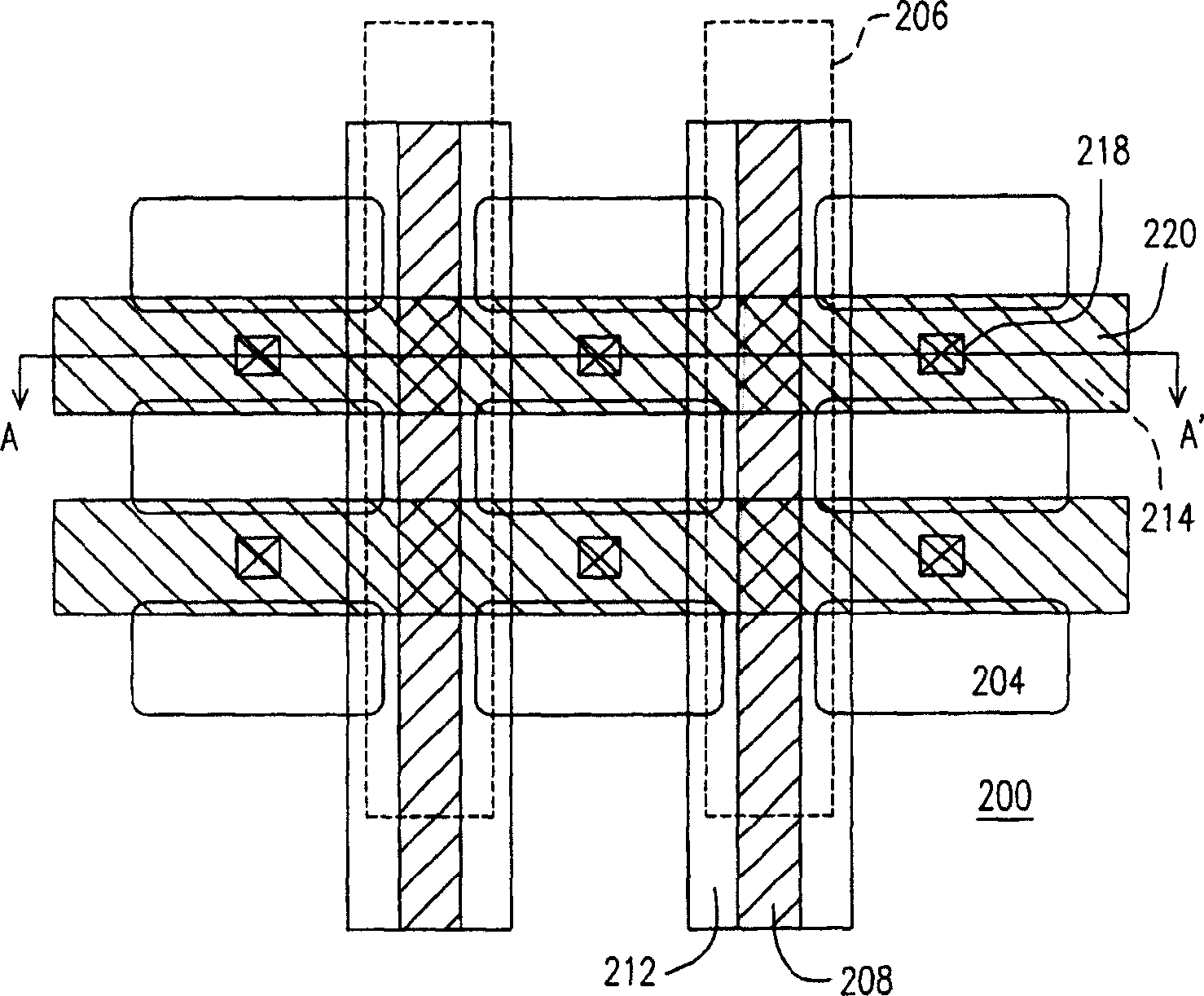

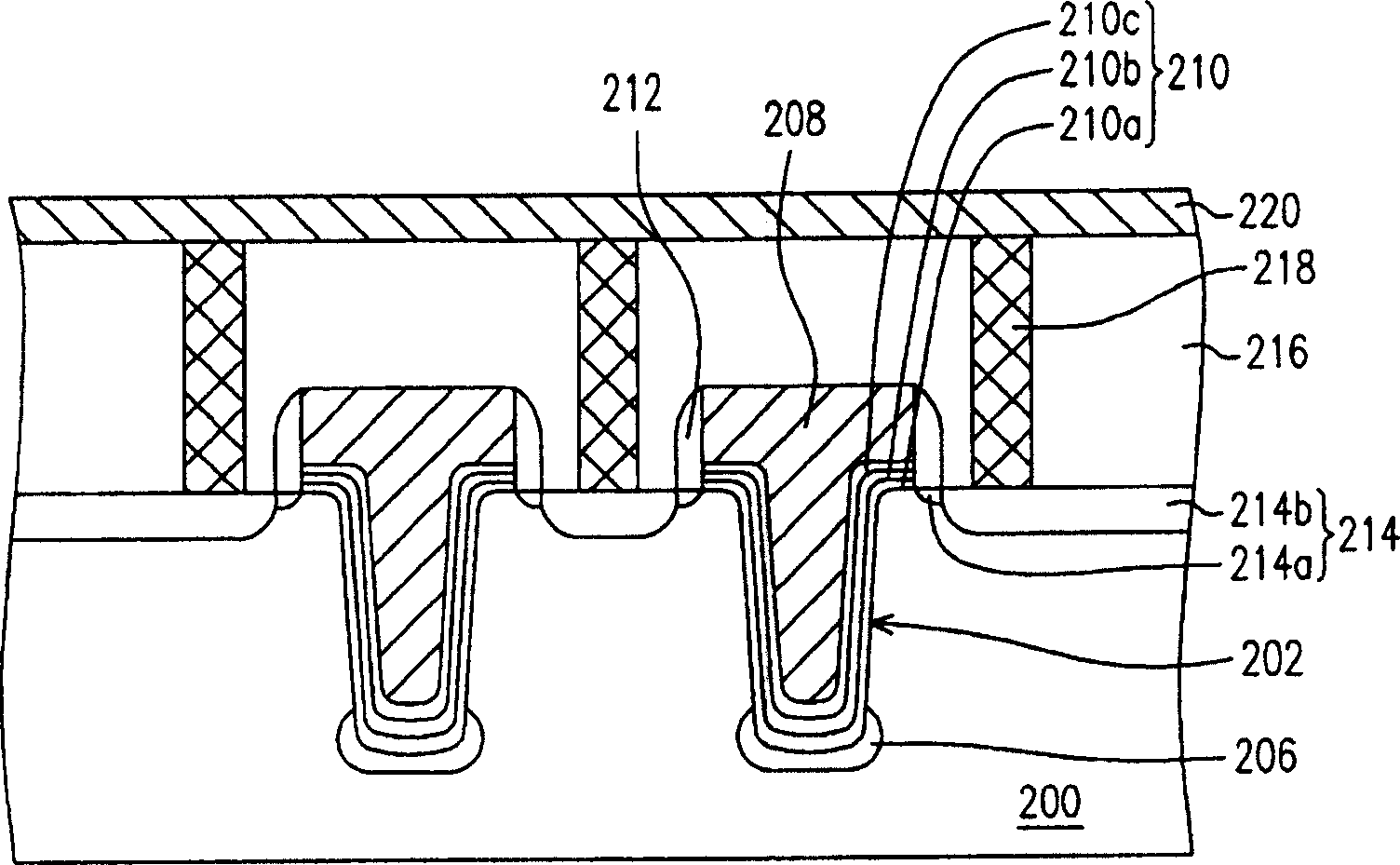

[0036] Figure 2A What is shown is a top view of a non-volatile memory unit according to a preferred embodiment of the present invention. Figure 2B Shown is a schematic cross-sectional view of a non-volatile storage unit in a preferred embodiment of the present invention, and it is Figure 2A Schematic cross-section along A-A'.

[0037] Please also refer to Figure 2A and Figure 2B, the non-volatile memory cell includes a substrate 200, an element isolation structure 204, a source / drain region 206, a gate 208, a composite dielectric layer 210, a spacer 212, a source / drain region 214, an interlayer dielectric Electrical layer 216 , plug 218 , wire 220 .

[0038] The substrate 200 is, for example, a silicon substrate, and a trench 202 is disposed in the substrate 200 . The device isolation structure 204 is disposed in the substrate 200 to define an active region. The element isolation structure 204 is, for example, a field oxide isolation structure or a shallow trench is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More