Improved method for reading a non-volatile memory cell adjacent to an inactive region of a non-volatile memory cell array

A non-volatile storage and storage cell technology, applied in the field of flash memory cell devices, can solve the problems of lowering the threshold voltage of the storage cell, depletion of the charge storage area, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

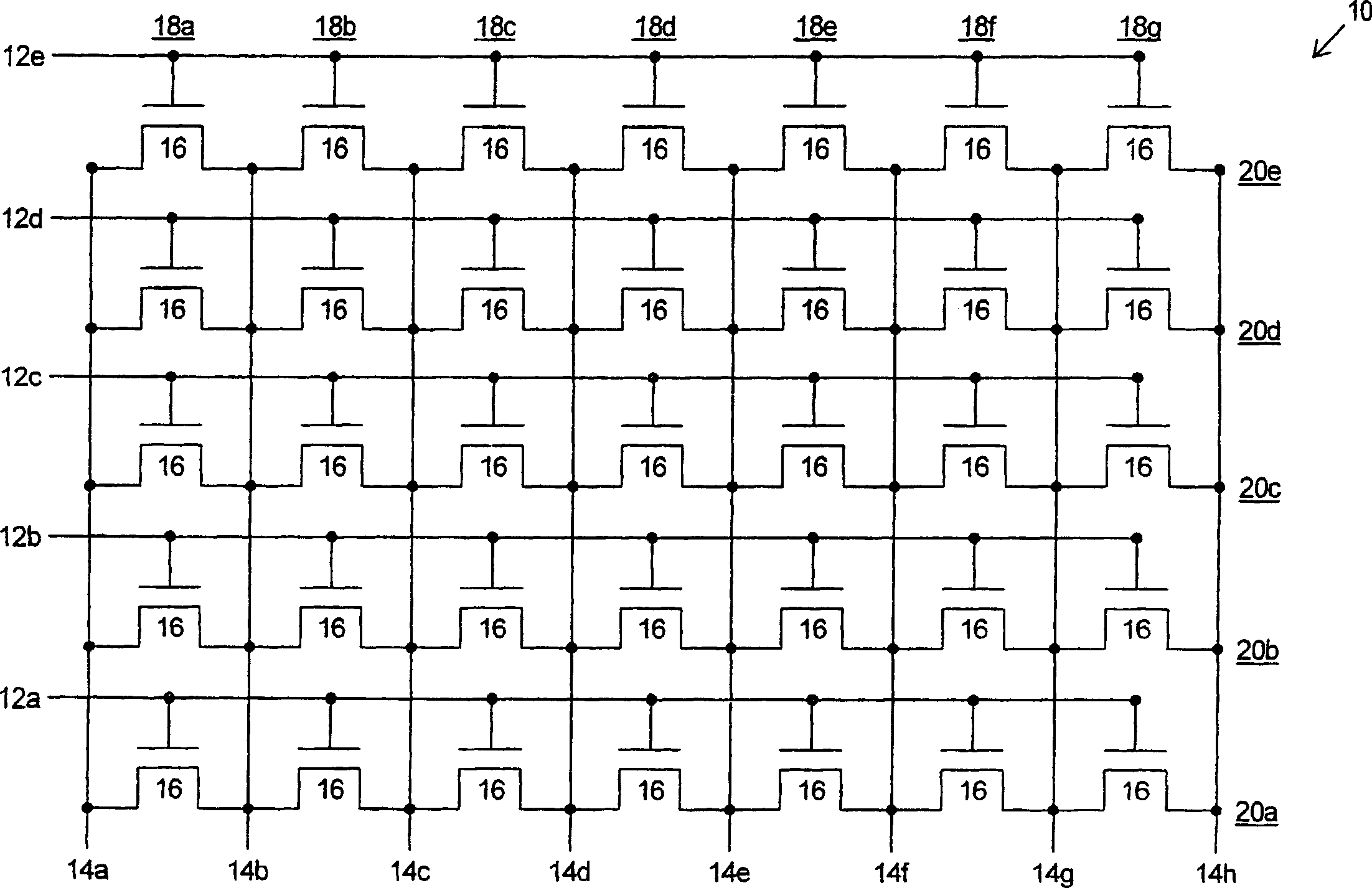

[0039] The present invention will now be described in detail with reference to the accompanying drawings. In the drawings, the same reference numerals are used to designate the same components. Moreover, the drawings are not drawn to scale, and the dimensions of some features are intentionally drawn larger for clarity.

[0040] figure 2 An example embodiment of a non-volatile charge trapping dielectric flash memory cell system 30 is shown in block diagram form. System 30 includes array 40 of non-volatile charge trapping memory cells 48 fabricated on a crystalline semiconductor substrate and array control circuitry 62 .

[0041] The array 40 of non-volatile charge trapping dielectric flash memory cells 48 is arranged in a matrix format, the memory cells 48 being arranged in vertical columns 45a to 45h and orthogonal horizontal rows 43a to 43h. Each memory cell 48 in a column 45 shares the same channel region and two bit line diffusion regions 49 with another memory cell 48 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com