Transistor and strained channel element formation method

A technology of strained channels and transistors, which is applied in the manufacture of electrical components, semiconductor devices, semiconductor/solid-state devices, etc., to achieve the effect of reducing damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The manufacturing method and using method of the preferred embodiment of the present invention will be disclosed below. The present invention provides an implementation concept, which can be applied in a wide range of implementation examples. The following disclosures are only methods for making and using certain embodiments of the present invention, and are not intended to limit the present invention.

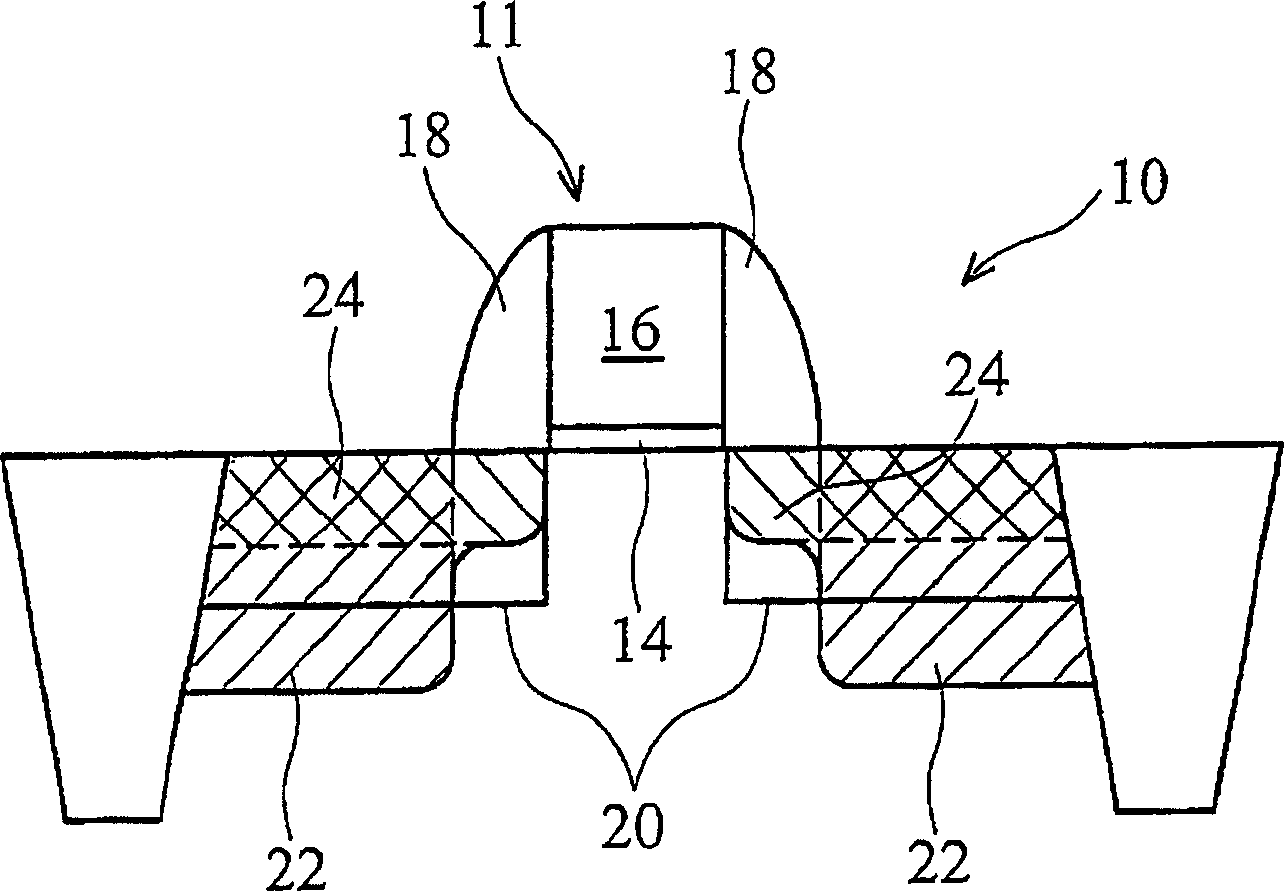

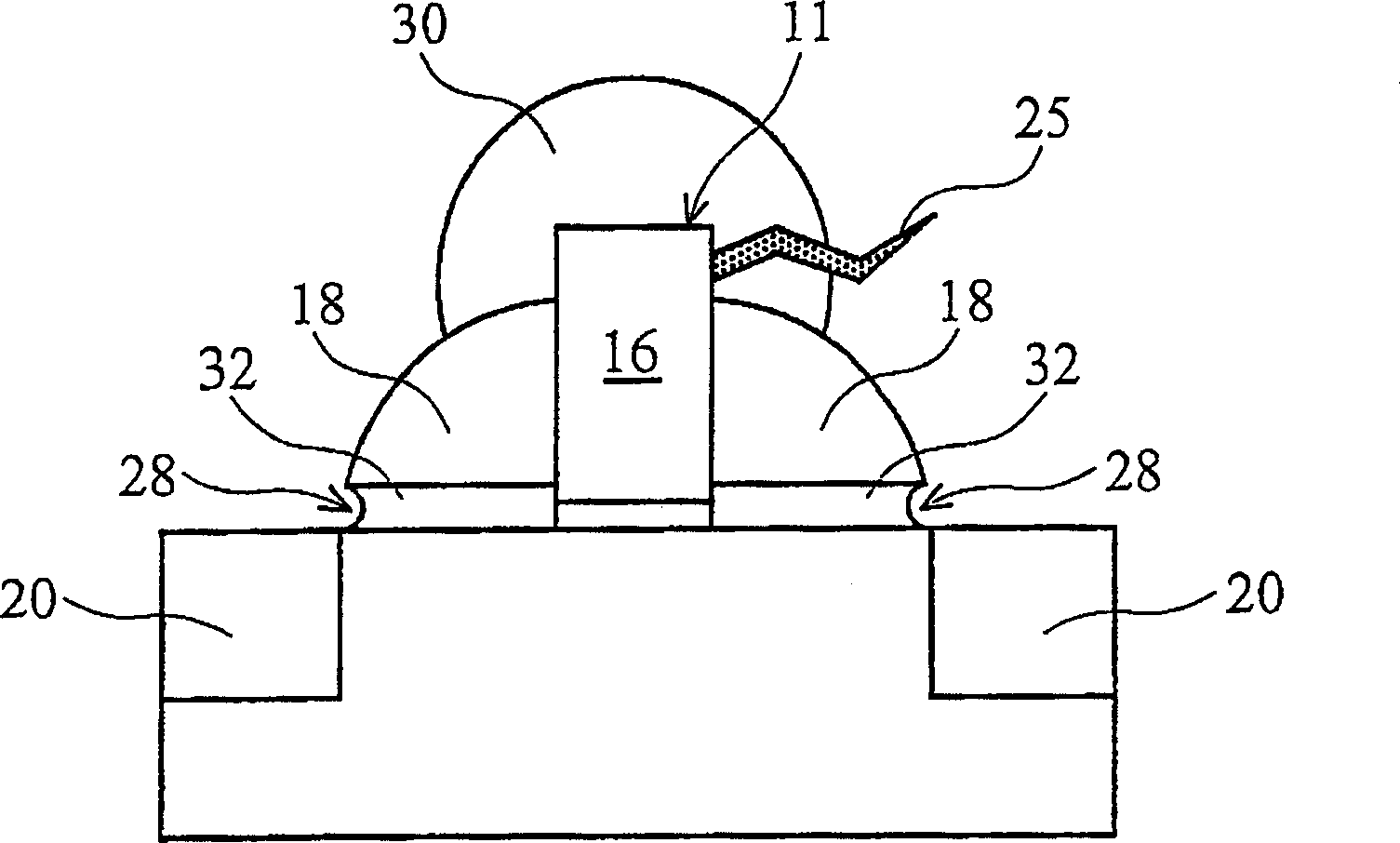

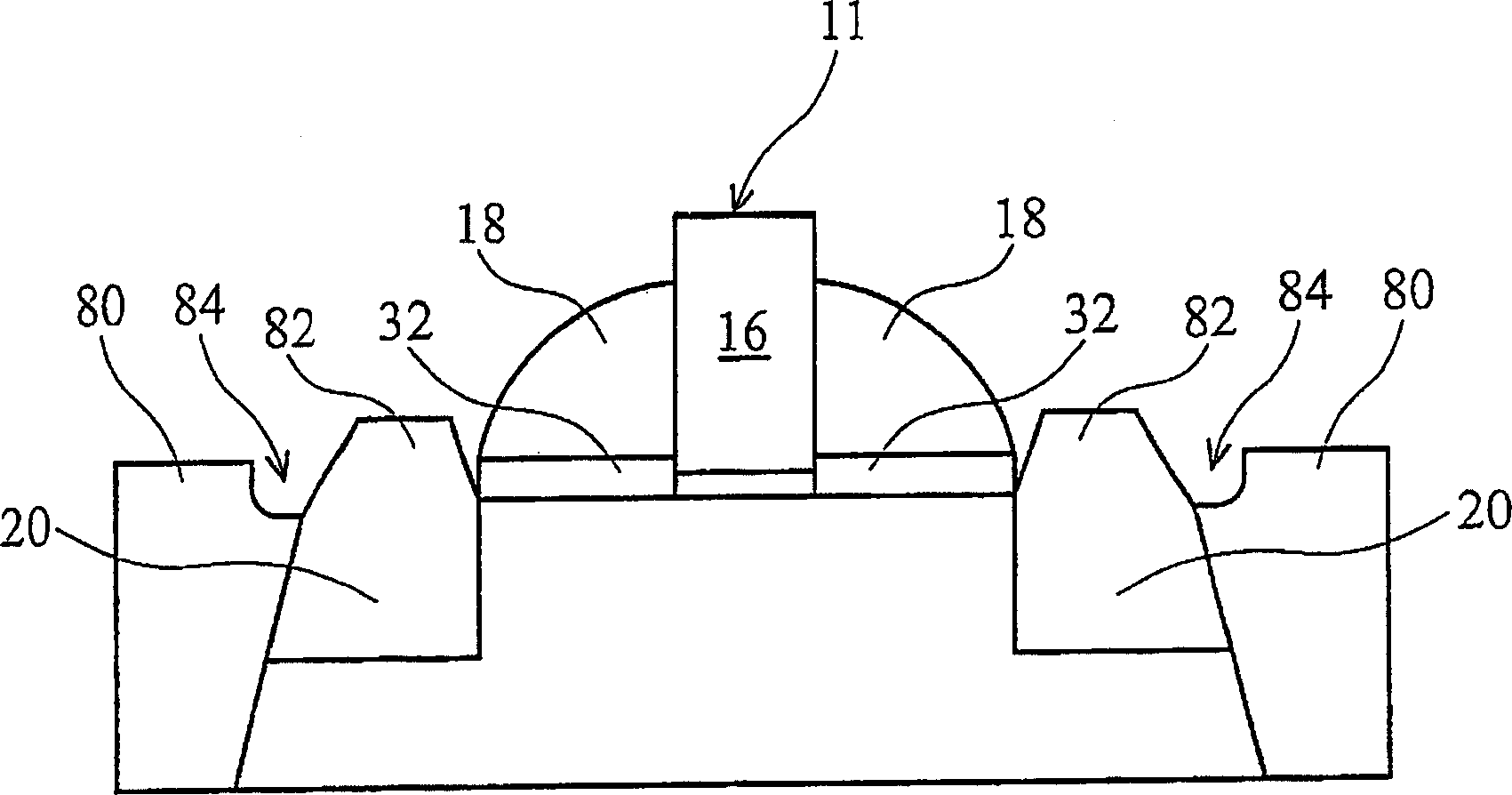

[0035] The present invention relates to the field of semiconductor elements, in particular to a method for manufacturing stress channel field effect transistors with uncoordinated lattice regions. The manufacturing method of the first embodiment of the present invention will be disclosed below.

[0036] Figure 2a A substrate 100 is disclosed, having an active region 102 defined by a shallow trench isolation structure 101 . In addition, other types of isolation structures (such as LOCOS and mesa isolation structures) can be used to isolate the active region 102 . Su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More