Parallel interchanging switching designing method

A technology for exchanging switches and design methods, which is applied in the direction of switching stations and data exchange details, etc., which can solve problems such as bandwidth overhead, increasing the demand for input port buffer bandwidth, and out-of-order cells, so as to ensure load balance, reduce implementation difficulty, Good scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

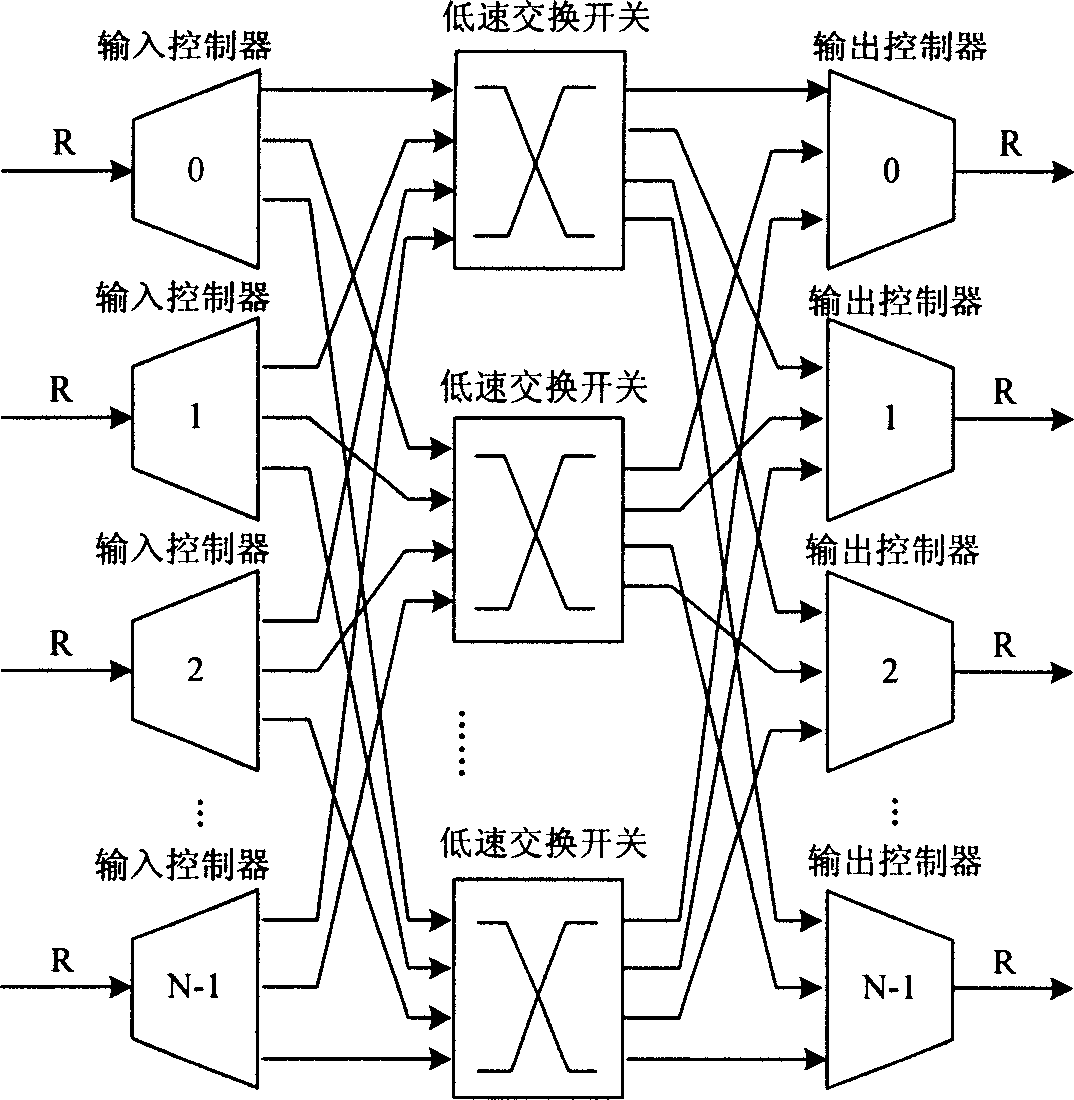

[0049] figure 1 It is a general structure diagram of a parallel switching switch, which consists of N input controllers, m low-speed switching switches and N output controllers. The input controller distributes the input cells to the low-speed switching switches for load balancing. The low-speed switching switches work in parallel and process the assigned data independently. The output controller completes the cell reassembly, and outputs the reassembled cells to the external line.

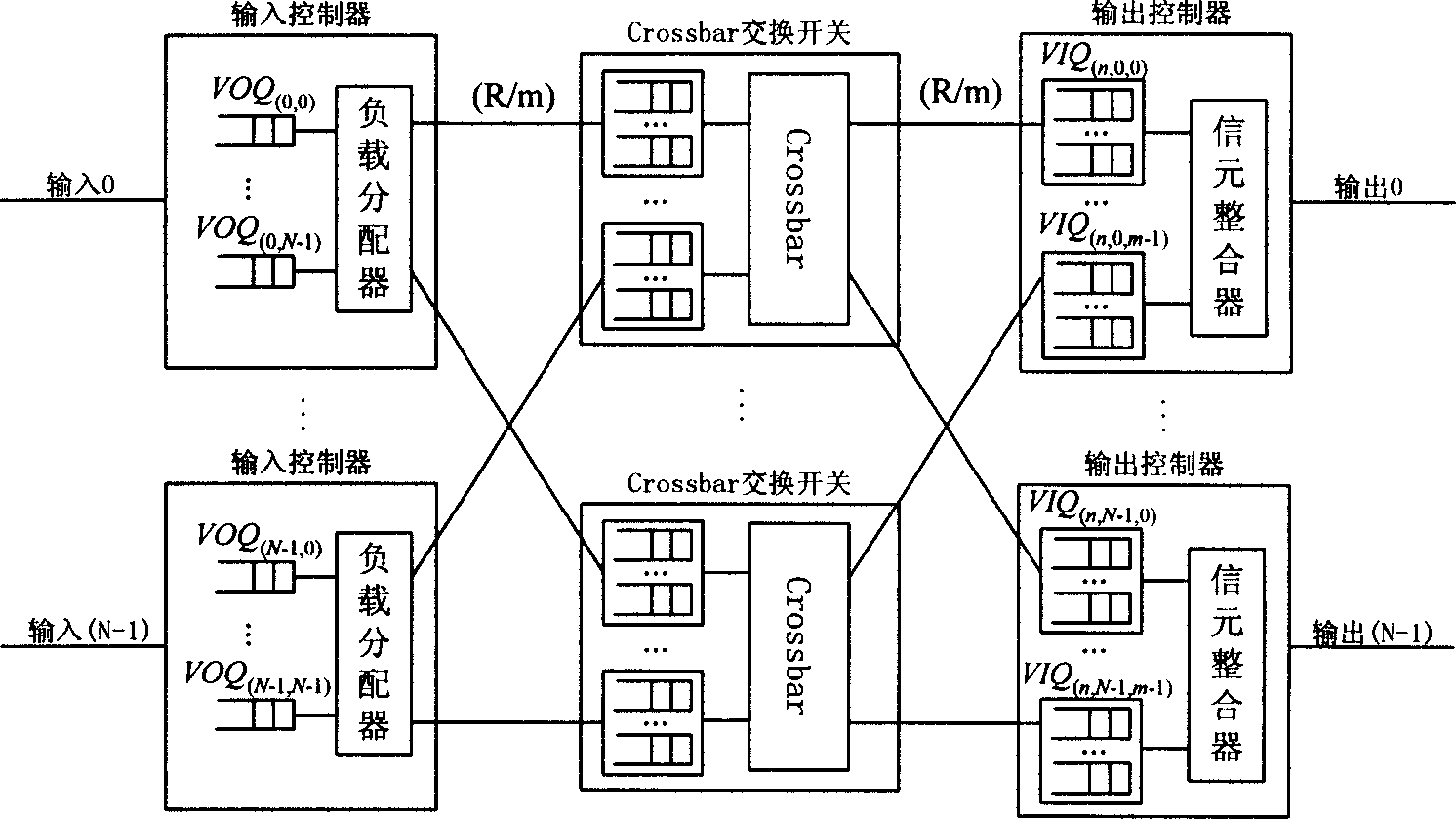

[0050] figure 2 It is a structural diagram of a parallel switching switch PSC of the present invention. The PSC parallel switching switch consists of N input controllers, m input buffering Crossbar switching switches with a speedup ratio of 1 (that is, the port rate is R / m), and N output controllers. The input controller is responsible for receiving cells, and evenly distributes cells to the Crossbar switch in a polling manner to ensure load balancing. Each input controller includes N virtual...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More