Manufacturing method of in-connection and manufacturing method of composite dielectric barrier-layer

A technology of dielectric barrier and manufacturing method, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems affecting process reliability and yield, improve process reliability and prevent outward diffusion , The effect of improving reliability and yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

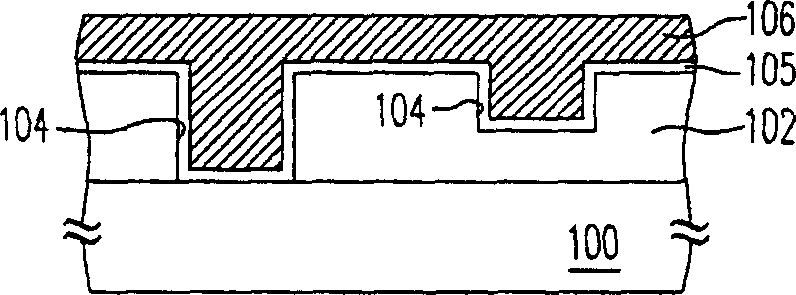

[0031] Figure 1A to Figure 1G What is shown is a schematic cross-sectional flow diagram of the manufacturing method of the interconnection line according to the preferred embodiment of the present invention.

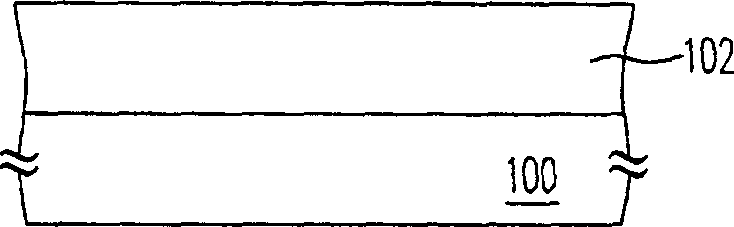

[0032] First, please refer to Figure 1A , providing a substrate 100 in which elements (not shown) have been formed. Next, a dielectric layer 102 is formed on the substrate 100. The material of the dielectric layer 102 is, for example, silicon oxide, and the formation method is, for example, chemical vapor deposition. In addition, the above-mentioned dielectric layer 102 can be formed of one layer or multiple layers of dielectric material, which can be adjusted according to the circuit design requirements in the process.

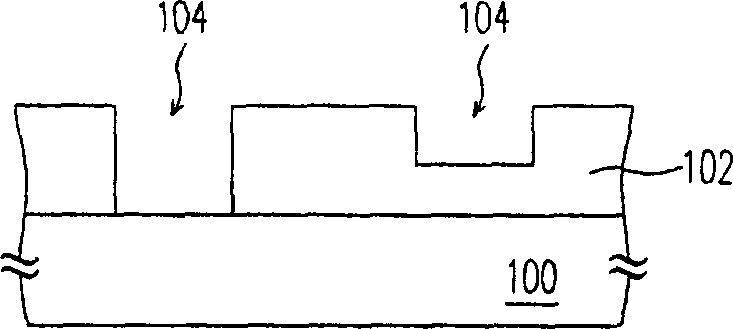

[0033] Then, please refer to Figure 1B , forming a plurality of openings 104 in the dielectric layer 102, and these openings 104 can be filled with conductive material in subsequent processes to be used as interconnection lines. Wherein, the formi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More