Processor, multiprocessor system, processor system, information processing device, and temperature control method

A multi-processor system and processor technology, applied in multi-programming devices, machine execution devices, program control design, etc., can solve the problems of reducing the operating frequency of the chip, sacrificing the processing performance of the processor, and poor time responsiveness.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

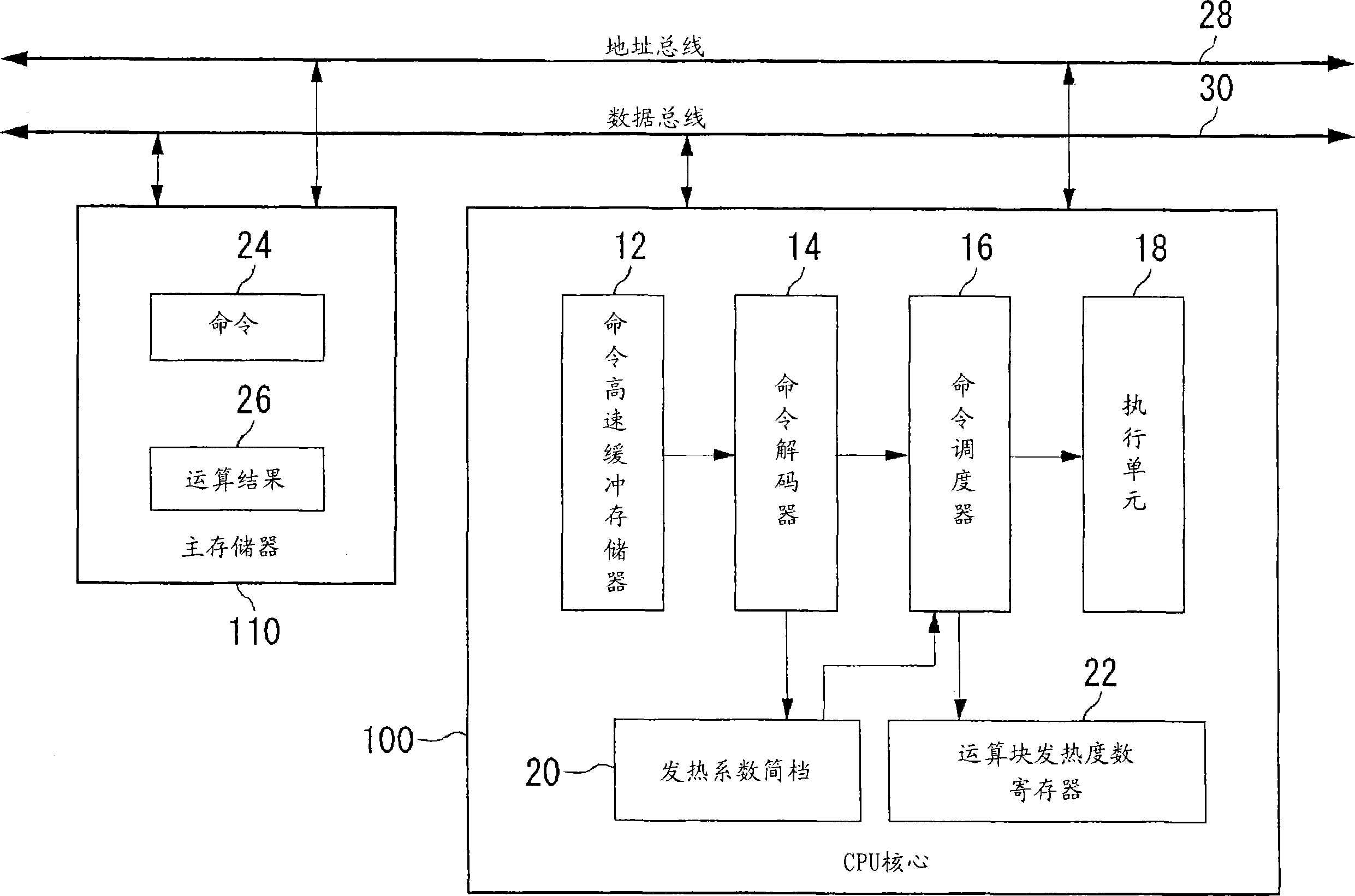

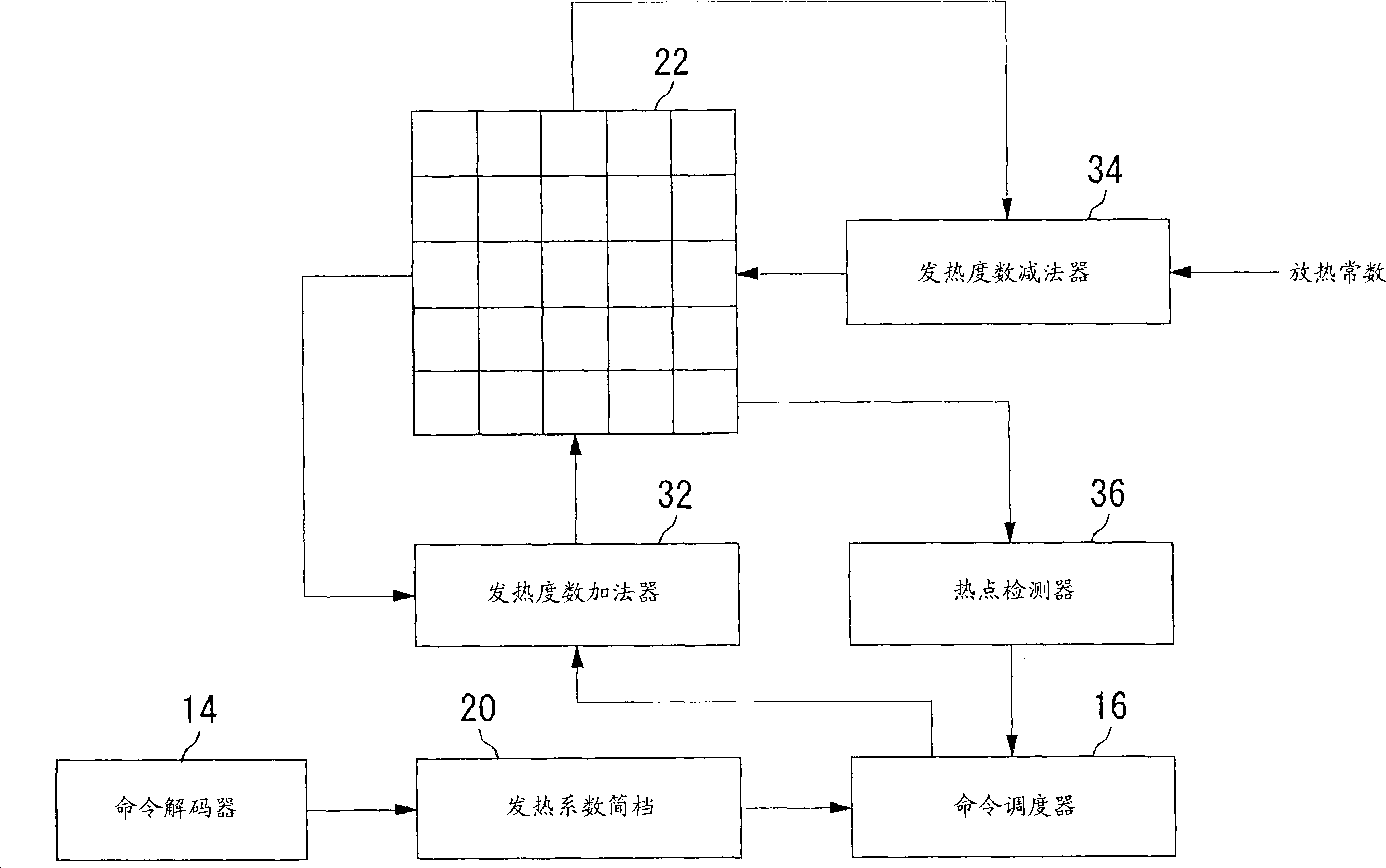

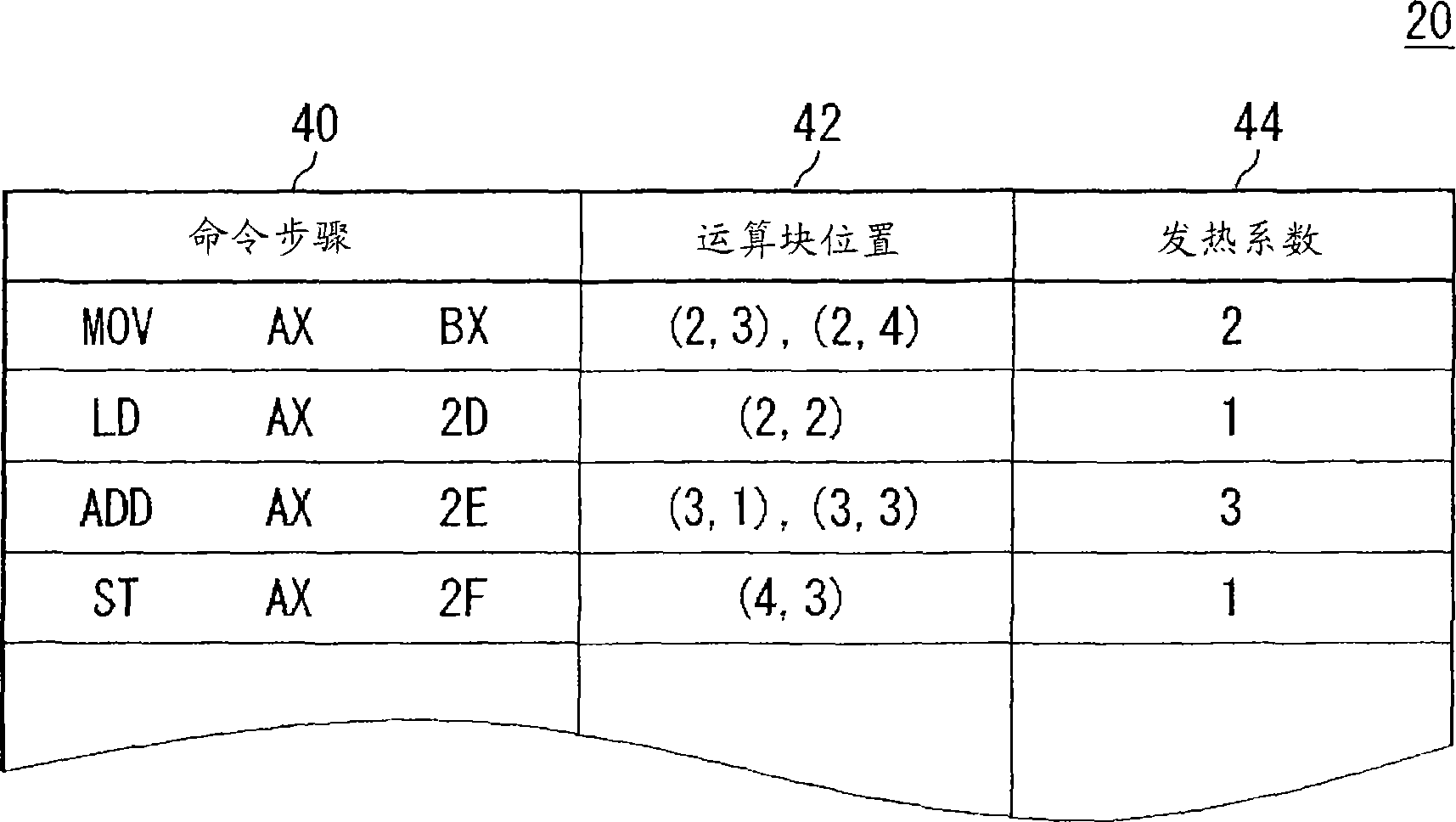

[0029] figure 1 It is a block diagram of the processor system of Embodiment 1. The processor system includes a CPU core 100 , a main memory 110 , which are connected to an address bus 28 and a data bus 30 . The CPU core 100 specifies an address to the main memory 110 to read and write data. The CPU core 100 includes a command cache memory 12 , a command decoder 14 , a command scheduler 16 , an execution unit 18 , a thermal coefficient profile 20 , and a calculation block thermal degree register 22 . Instructions 24 and calculation results 26 are stored in main memory 110 .

[0030] The command 24 read out from the main memory 110 by the CPU core 100 is temporarily cached in the command cache memory 12 . The command decoder 14 sequentially decodes the commands 24 cached in the command cache 12 and provides them to the command scheduler 16 . The command scheduler 16 arranges and replaces the order of execution of the commands 24 and adjusts the execution timing according to ...

Embodiment approach 2

[0054] Figure 6 It is a block diagram of the processor system of Embodiment 2. The processor system of the present embodiment is a multiprocessor system in which two subprocessors 230a, 230b are bus-bonded, in addition to the main processor 200 corresponding to the CPU core 100 of the first embodiment. The main processor 200 accesses the DRAM 220 via the bus to read data, and caches the data in the cache memory 210 . The main processor 200 appropriately assigns tasks to the two sub-processors 230a and 230b to execute programs.

[0055] The main processor 200 includes each functional structure of the CPU core 100 described in Embodiment 1, that is, the command cache 12, the command decoder 14, the command scheduler 16, the execution unit 18, the thermal coefficient profile 20, the calculation Block heat degree register 22 , heat degree adder 32 , heat degree subtractor 34 and hot spot detector 36 . Hereinafter, operations different from those of the first embodiment will be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com