Vertical pnp transistor and method of making same

A transistor and single crystal technology, applied in the vertical PNP transistor and its manufacturing field, can solve the problems of no additional process steps, increased manufacturing cost, prolonged process time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The subsequent U.S. Patent and U.S. Patent Application Publication are hereby incorporated by reference in their entirety for all purposes:

[0032] U.S. Patent No. 5,111,271, "SEMICONDUCTOR DEVICE USING STANDARD CELL SYSTEM," issued May 5, 1992;

[0033] U.S. Patent Application No. 10 / 065,837, "HIGHPERFORMANCE VERTICAL PNP TRANSISTOR AND METHOD," filed May 27, 2004 and published as U.S. Patent Application Publication No. 2004 / 0099895 on May 27, 2004; and

[0034] US Patent Application No. 10 / 863,630, "HIGHPERFORMANCE VERTICAL PNP TRANSISTOR METHOD," filed June 8, 2004, published December 9, 2004 as US Patent Application Publication No. 2004 / 0248352.

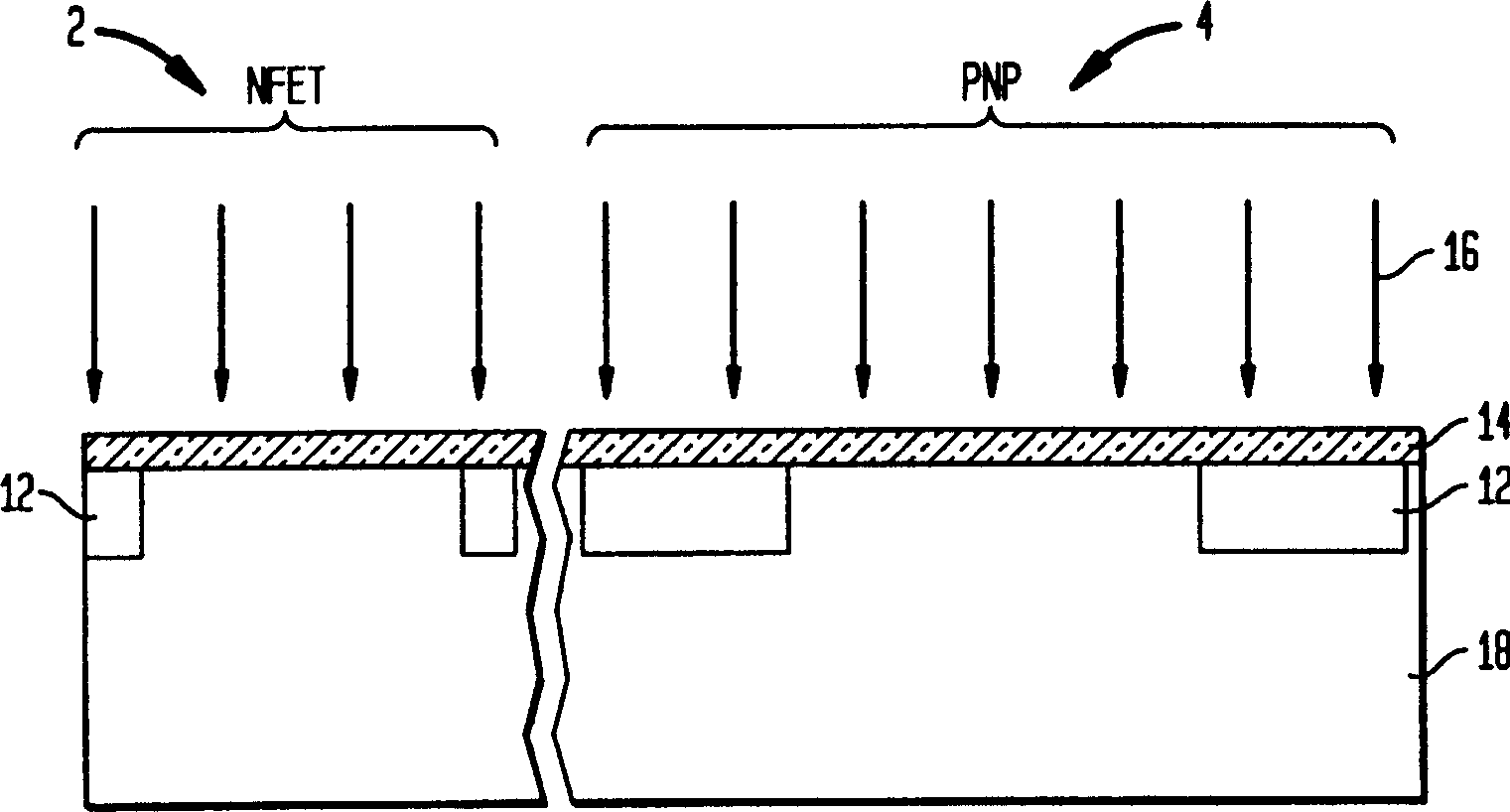

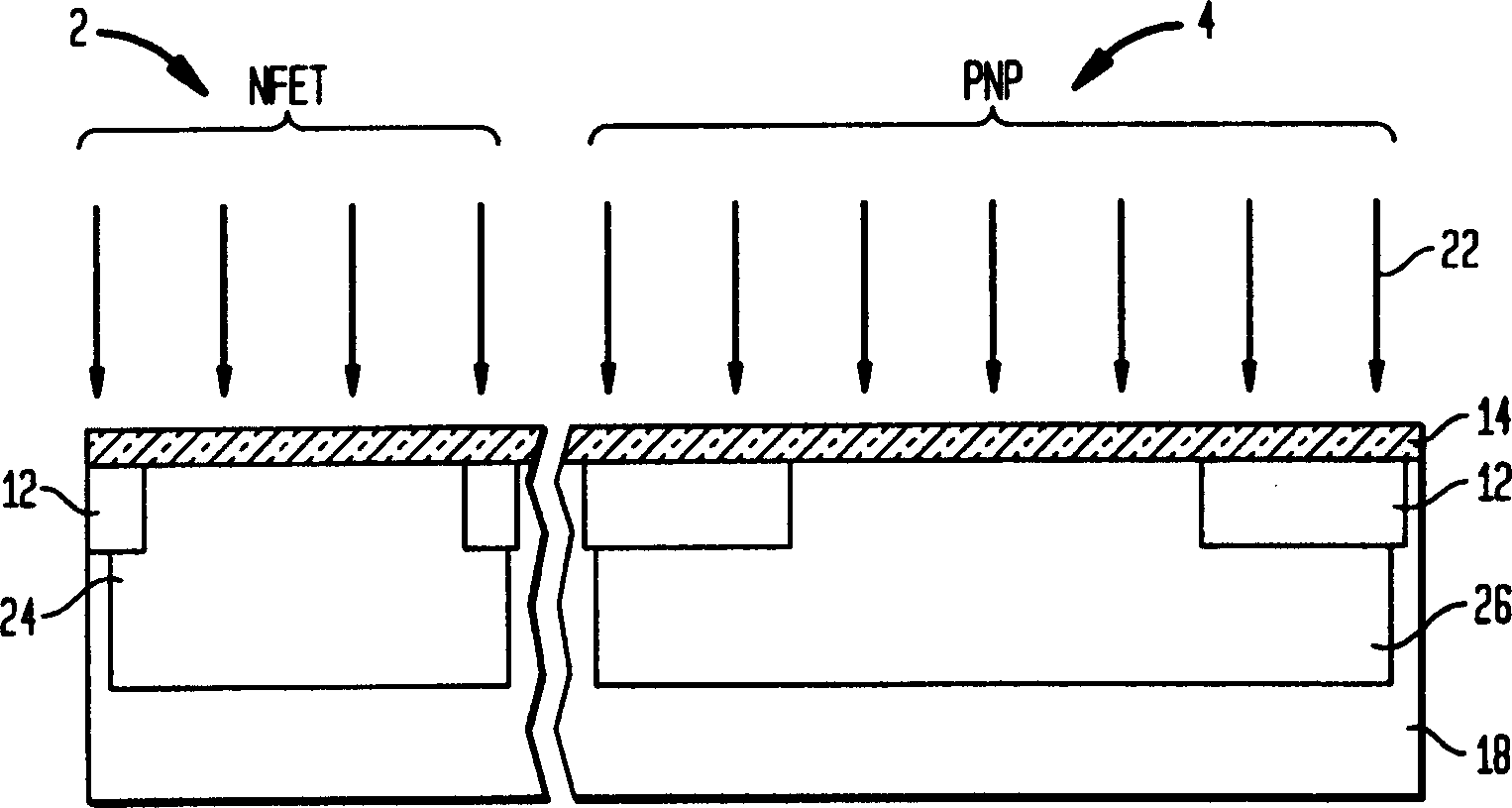

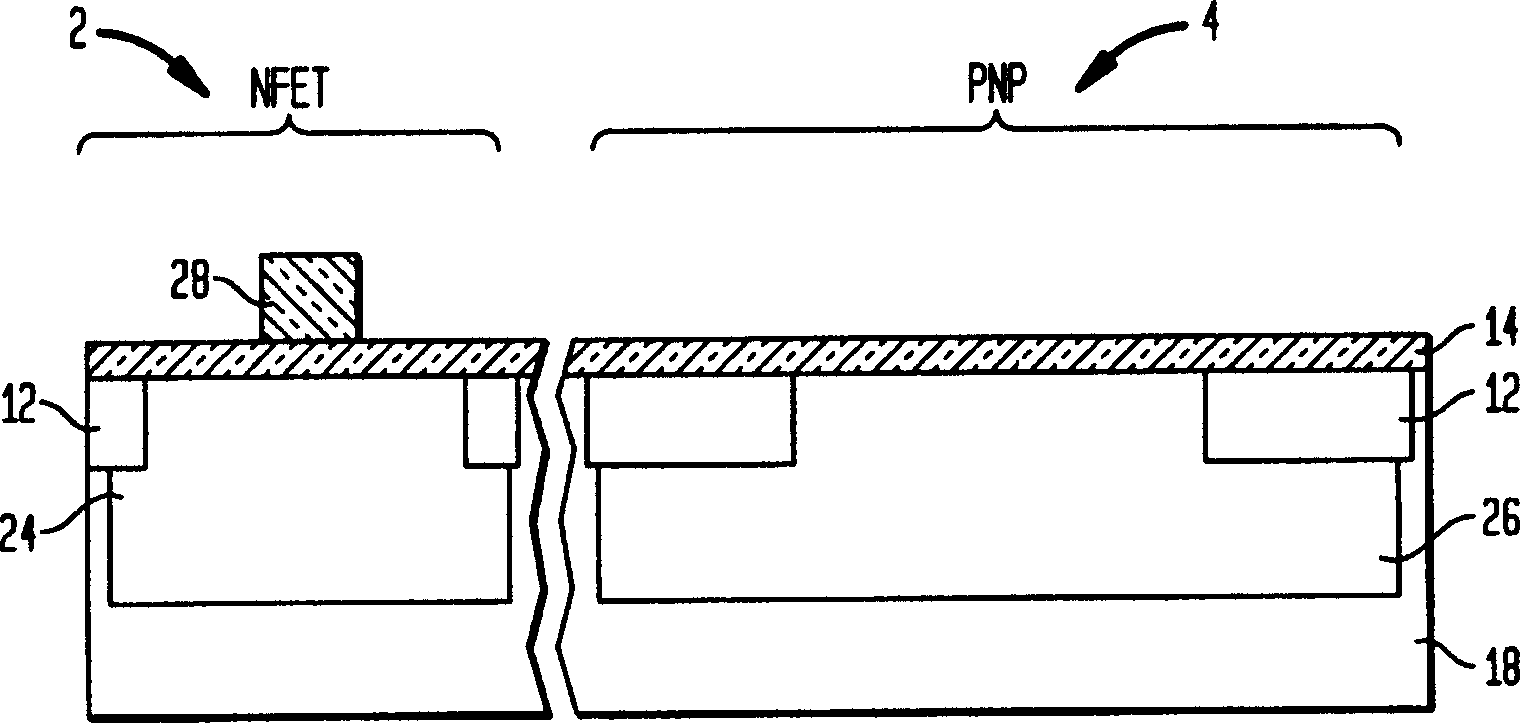

[0035] The present invention provides a method for fabricating high performance vertical PNP transistors utilizing a novel combination of existing process steps and conventional SiGe BiCMOS technology designed to form only n-channel or p-channel field effect transistors ( NFET or PFET) CMOS devices and bipolar NPN transi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More