Method for realizing supporting of EJTAG detection in instruction grade random detection

A technology of random testing and implementation method, applied in the direction of software testing/debugging, etc., can solve the problem of inability to realize on-chip cross-debugger testing, and achieve the effect of high test efficiency, low efficiency and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

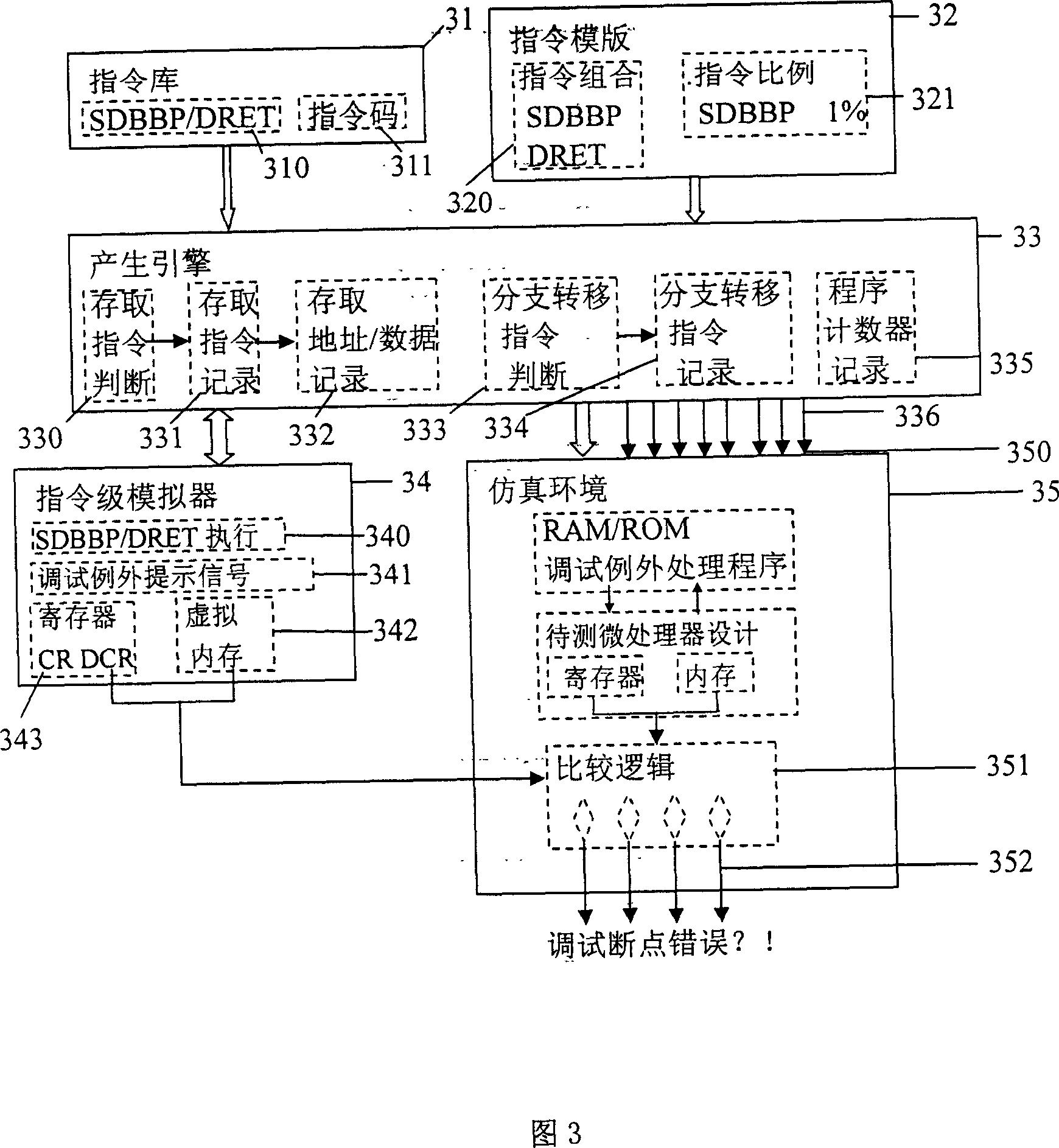

[0036] As shown in Figure 2, a method for supporting EJTAG testing in instruction-level random testing includes the following steps:

[0037]Step 1, add the EJTAG debugging command SDBBP / DRET in the command library;

[0038] Step 2, add constraints related to debugging instructions in the instruction template;

[0039] Step 3, improve the instruction-level random test generation engine, add access instruction judgment, program counter random extraction, access address record, access data record, jump instruction record, and add corresponding output signals at the same time;

[0040] Step 4, add the execution mechanism of the debugging instruction SDBBP / DRET in the instruction level simulator, and add the debugging control register (DCR) at the same time, and provide the correct result when the system enters the EJTAG debugging interrupt;

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More