Thin packing structure for enhancing crystal fin radiation

A thin, crystal-backed technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problems of inability to improve heat dissipation efficiency and inconvenience, prevent overflow glue from flowing in, and enhance chip structural strength , Improve the effect of heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

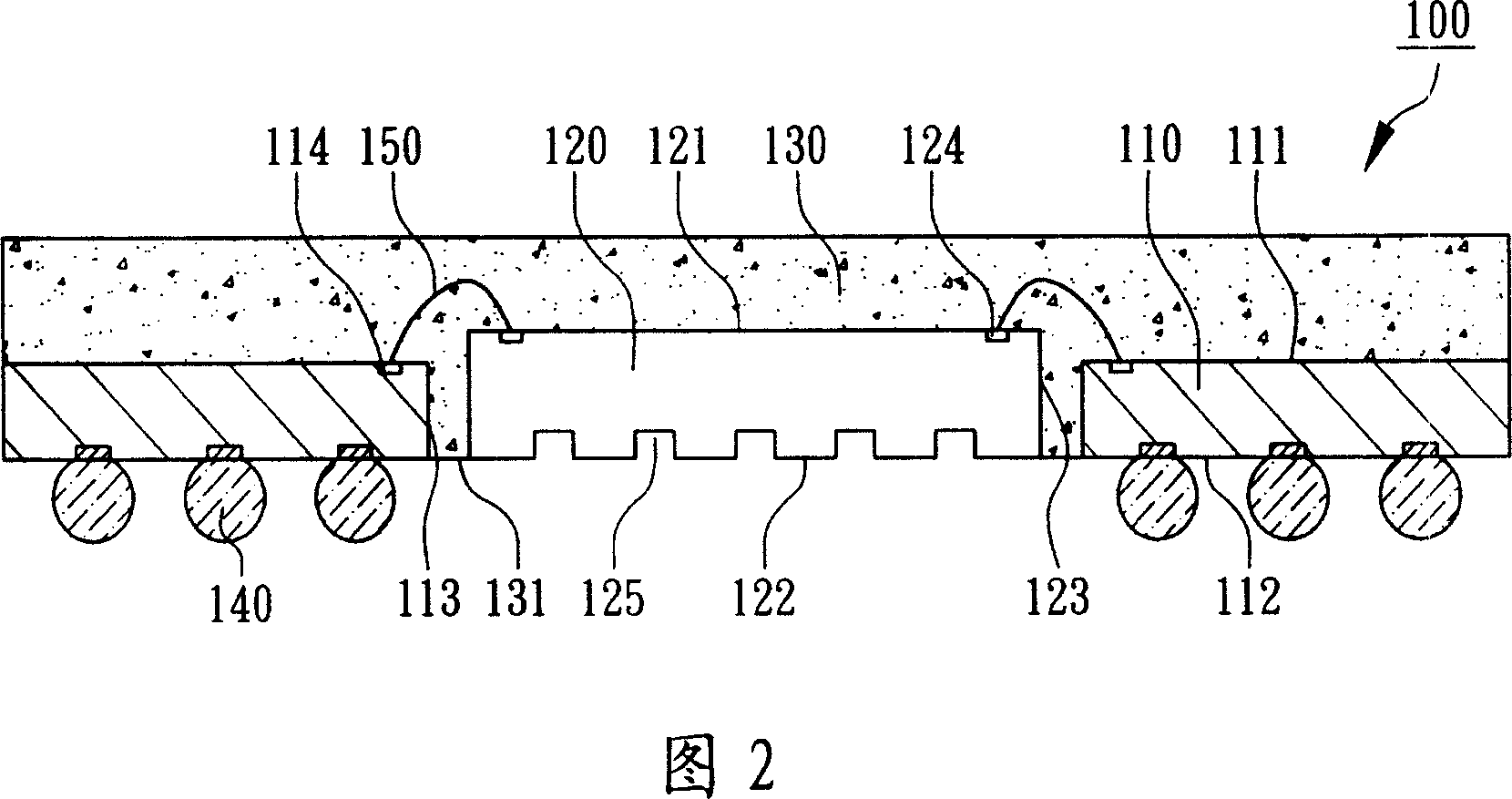

[0070] Please refer to FIG. 2 , which is a schematic cross-sectional view of a thin package structure for improving heat dissipation on the crystal back according to the first embodiment of the present invention. The thin package structure 100 for improving heat dissipation on the crystal back is in the form of a Ball Grid Array (BGA) package. The thin packaging structure 100 mainly includes a substrate 110, a chip 120 and a sealing compound 130, wherein:

[0071] The substrate 110 has an upper surface 111 , a lower surface 112 and a capacitive hole 113 passing through the upper surface 111 and the lower surface 112 . During the packaging process, the substrate 110 is not used to directly carry the chip 120 , but is attached to the lower surface 112 of the substrate 110 with a temporary adhesive tape (not shown) to bond and fix the chip 120 . Therefore, the chip 120 can be accommodated in the crystal hole 113 of the substrate 110;

[0072] The wafer 120 has an active surface...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com