Display apparatus and driving method thereof

A technology for display devices and driving transistors, used in static indicators, instruments, electrical components, etc., to solve problems such as difficulty in realizing large-scale and high-precision image display devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

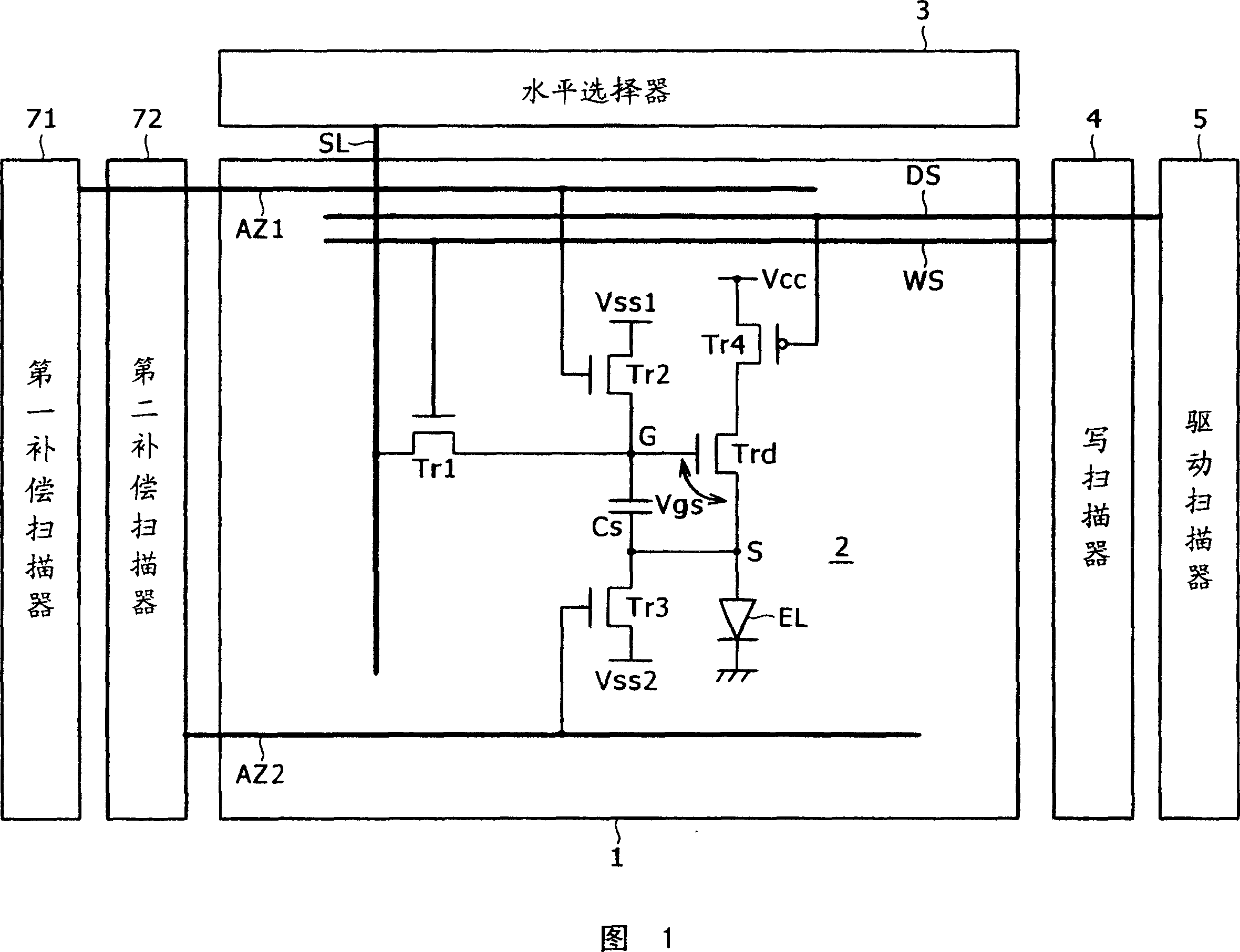

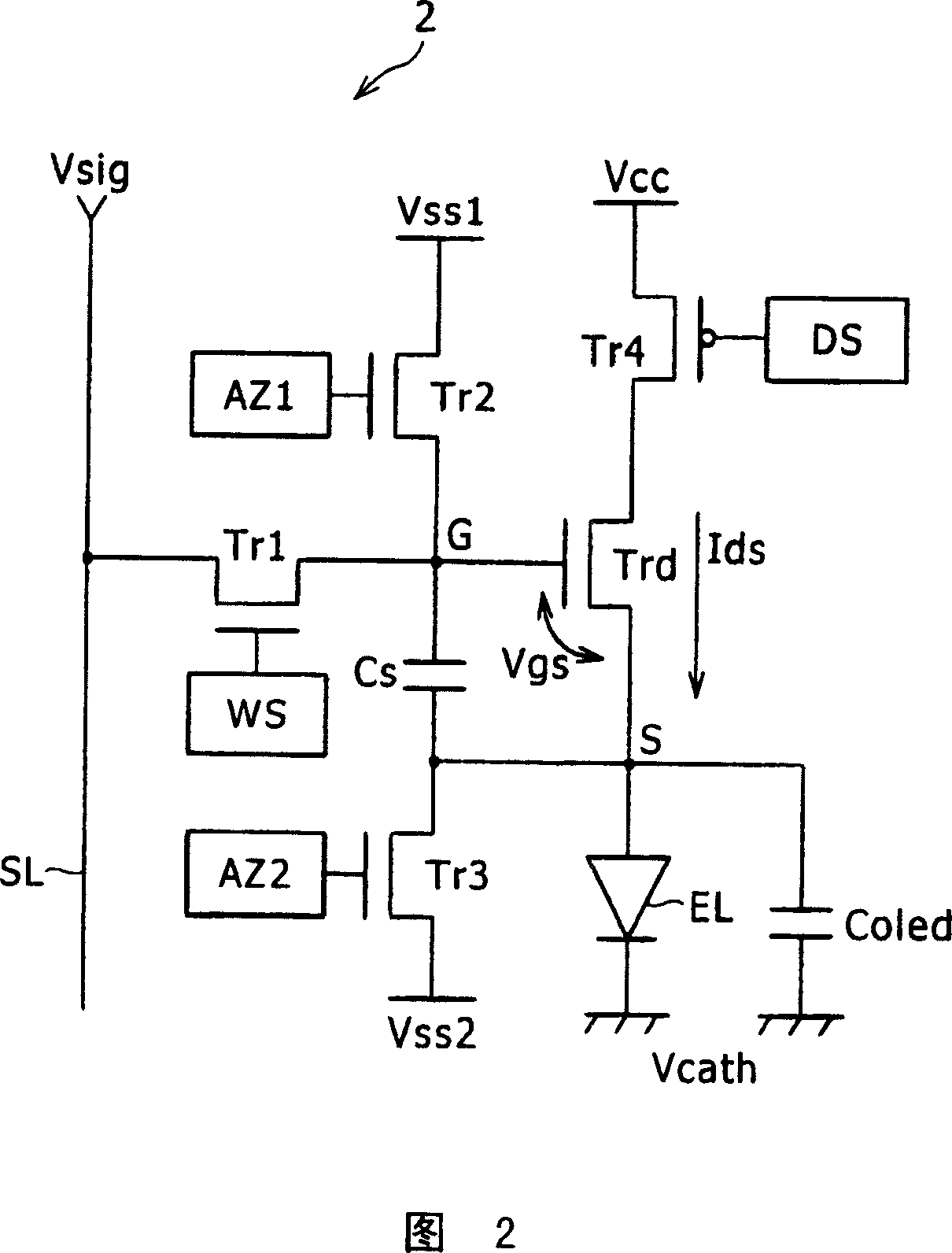

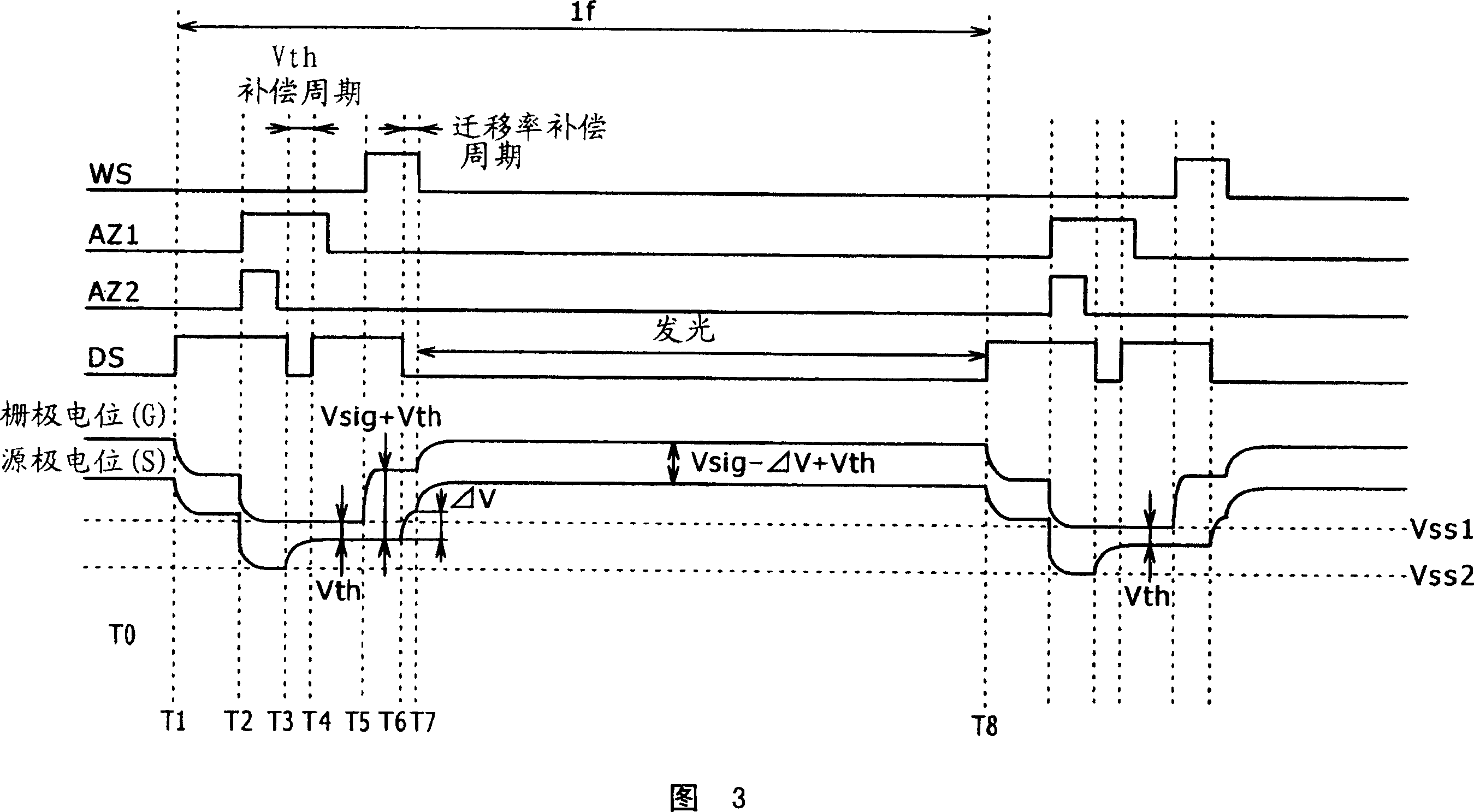

[0068] Preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings. First, a typical reference implementation of an image display device utilizing the principles of the present invention is explained with reference to FIG. 1 . As shown in the figure, the active matrix display device includes a pixel array unit 1 serving as a main part and its peripheral circuits. The peripheral circuit includes a horizontal selector 3 , a write scanner 4 , a drive scanner 5 , a first compensation scanner 71 and a second compensation scanner 72 . The pixel array unit 1 has pixel circuits 2 arranged to form a matrix. Each pixel circuit 2 is disposed at the intersection of the scan lines WS positioned in the row direction of the matrix and the data signal lines SL positioned in the column direction of the matrix. For easy understanding of the figure, only one pixel circuit 2 is shown in enlarged form. The horizontal selector 3 dr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com