Delay library generation method and delay library generation device

a library generation and library technology, applied in the direction of instrumentation, program control, cad circuit design, etc., can solve the problems of increasing affecting the efficiency of library generation, and requiring a long time for obtaining the timing constraint value, etc., to achieve efficient generation, reduce the number of simulation cycles, and high accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

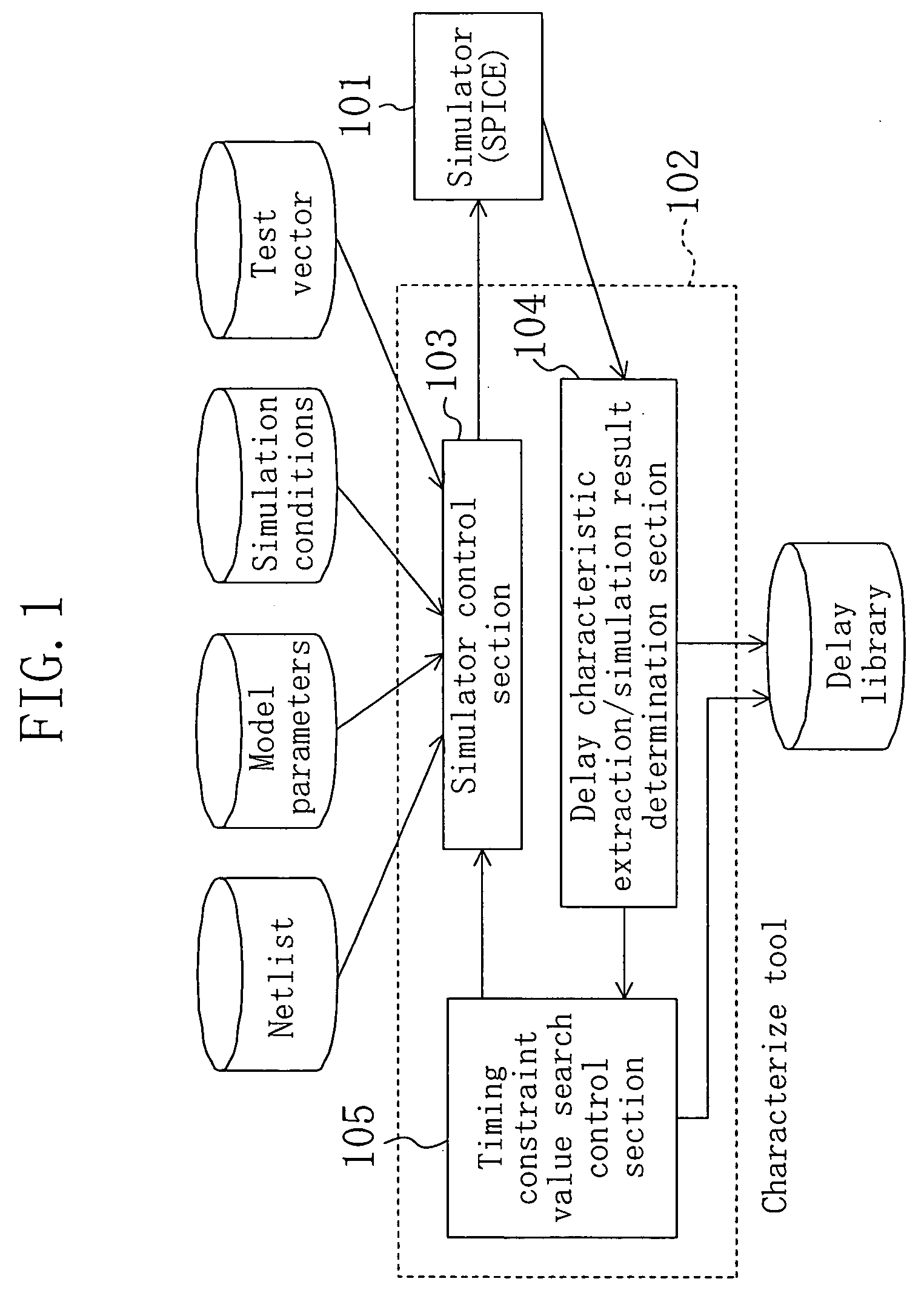

[0042] Referring to FIG. 1, a delay library generation device of embodiment 1 includes a simulator 101 for simulating a circuit operation, such as a SPICE (Simulation Program with Integrated Circuit Emphasis), or the like, and a characterize tool 102 for extracting a characteristic value based on a simulation result. Specifically, the characterize tool 102 includes a simulator control section 103, a delay characteristic extraction / simulation result determination section 104, and a timing constraint value search control section 105.

[0043] The simulator control section 103 inputs data necessary for simulation to the simulator 101 to instruct execution of simulation. For example, the data necessary for simulation includes: [0044] (1) a netlist including circuit connection information of a transistor, parasitic resistance and parasitic capacitance of each cell, which is to be included in a delay library subjected to simulation; [0045] (2) a model parameter for the simulator 101; [0046]...

embodiment 2

[0068] When there are a plurality of cells of the same type or a plurality of cells including a common circuit element, the timing constraint values of these cells are substantially equal in some cases. In such cases, a correct timing constraint value of any of the cells is obtained through the same process as that described in embodiment 1, and then, the initial value of the search range for the other cells is set based on the obtained timing constraint value, whereby the number of simulation cycles is decreased, and the timing constraint value is obtained in a short time period.

[0069] The delay library generation device which performs the above process basically has the same structure as that described in embodiment 1 (FIG. 1) except that the operation of the timing constraint value search control section 105 is different as shown in FIG. 11.

[0070] (S301 to S303) A correct timing constraint value of the first cell (representative cell) is obtained through the same process as tha...

embodiment 3

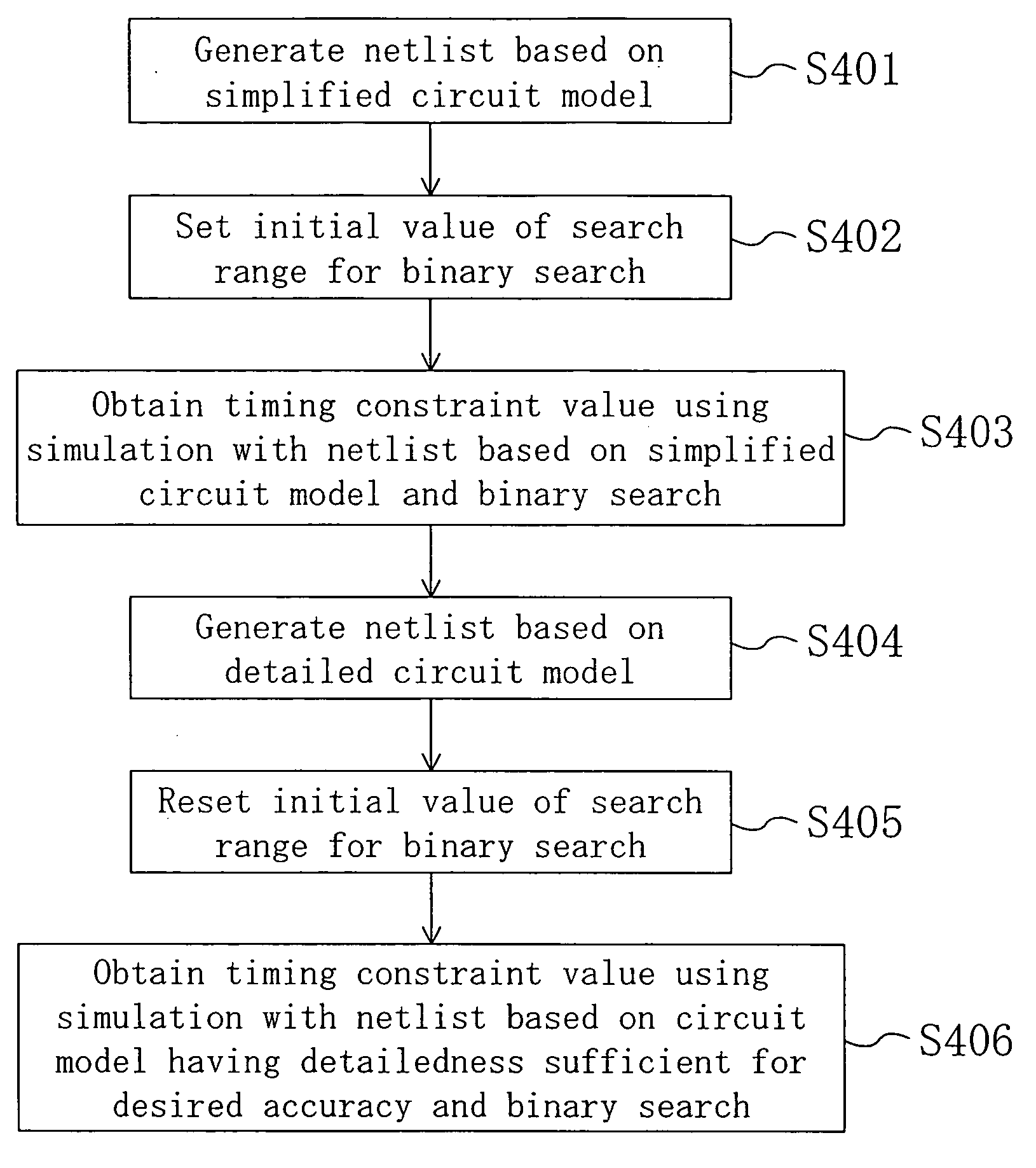

[0078] The data given in the simulation of the circuit operation (logic circuit information, such as a netlist, and the like) are generated based on a circuit model. As the circuit model becomes more detailed, the accuracy of a result obtained from the circuit model becomes higher whereas the time required for the simulation becomes longer. In view of such, in embodiment 3, the timing constraint value is obtained by simulation and binary search based on logic circuit information of a simplified circuit model, and then, the initial value of the search range is reset based on the obtained timing constraint value to perform simulation and binary search based on logic circuit information of a detailed circuit model, whereby a timing constraint value of a desired accuracy is quickly obtained.

[0079] A delay library generation device which performs the above processes has a structure basically equivalent to that of embodiment 1 (FIG. 1) except that the timing constraint value search contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More