Behavior processor system and method

a processor and behavior technology, applied in the field of electronic design automation, can solve the problems of burdening the user, requiring some degree of user sophistication, and cumbersome current software simulation and hardware emulation/acceleration, and achieve the effect of reducing performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

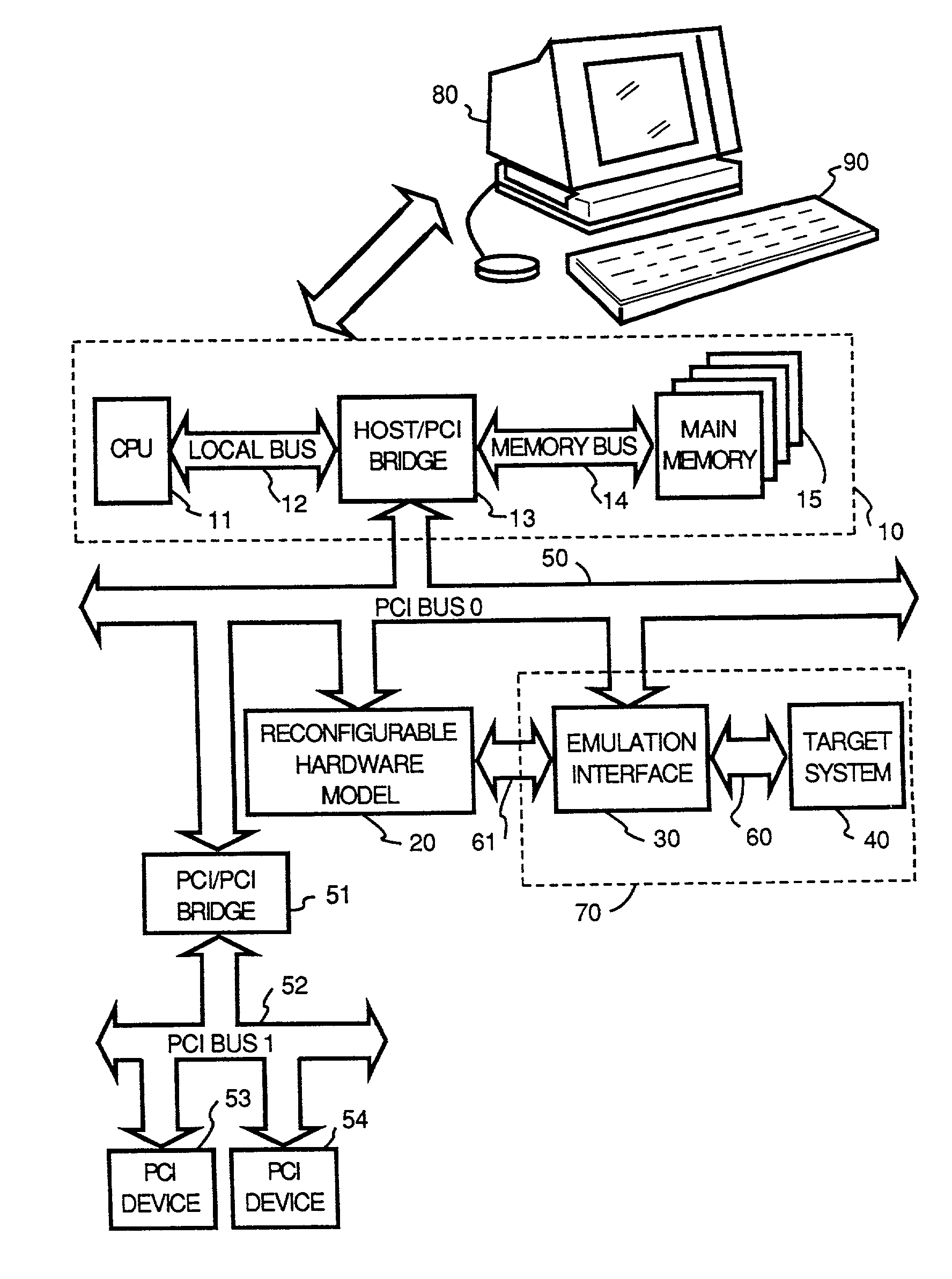

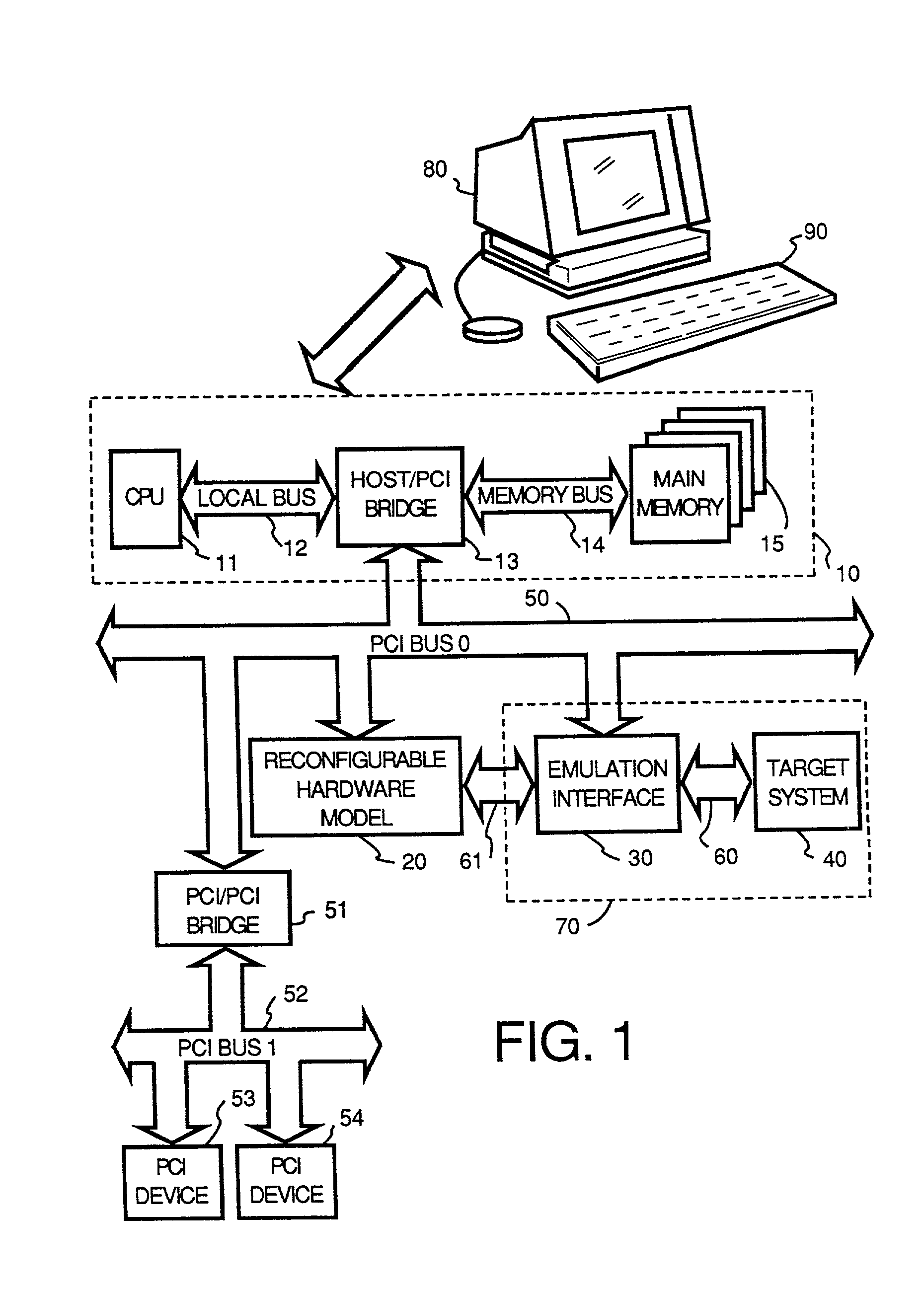

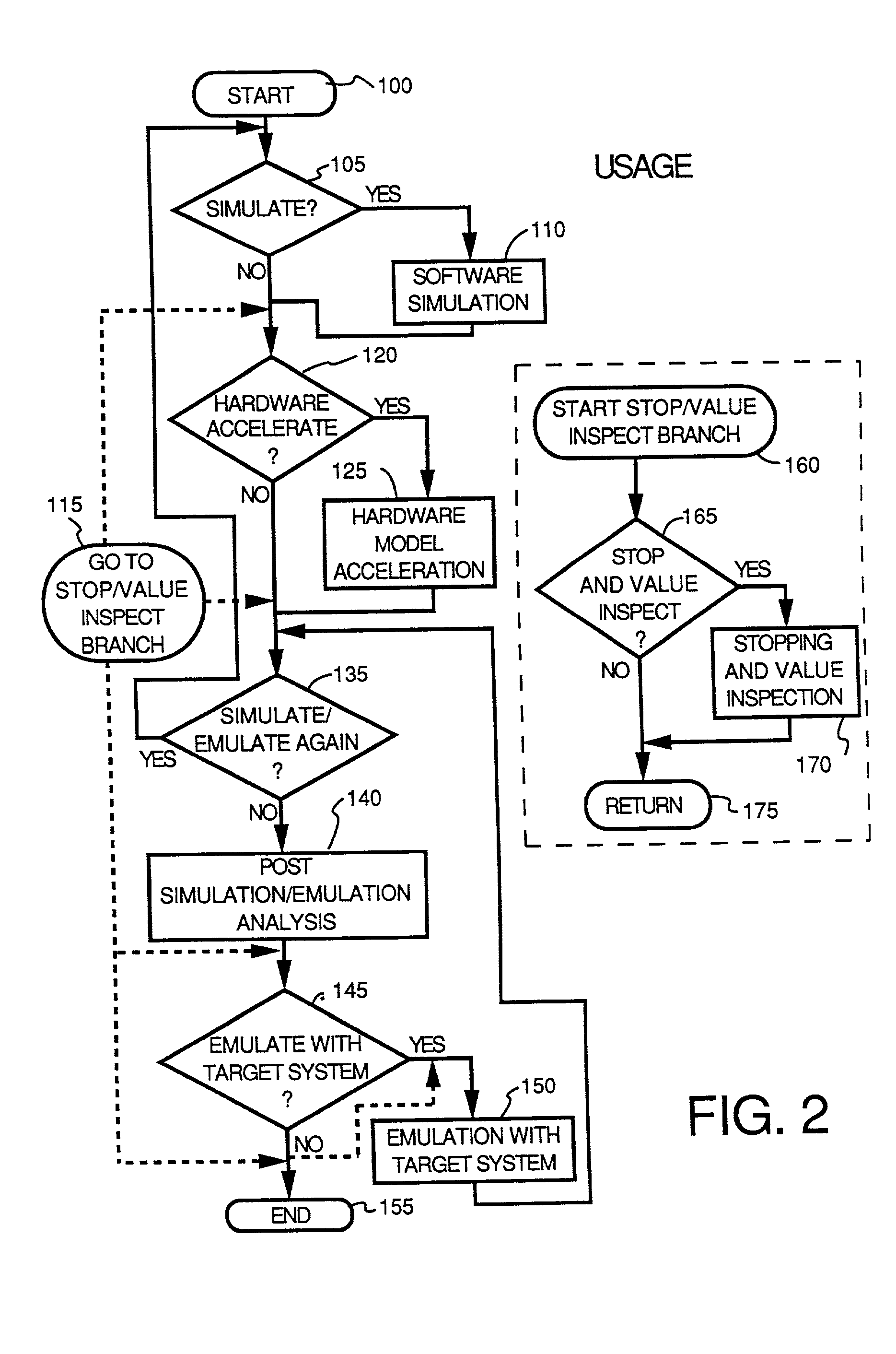

[0127] This specification will describe the various embodiments of the present invention through and within the context of a system called “SEmulator” or “SEmulation” system. Throughout the specification, the terms “SEmulation system,”“SEmulator system,”“SEmulator,” or simply “system” may be used. These terms refer to various apparatus and method embodiments in accordance with the present invention for any combination of four operating modes: (1) software simulation, (2) simulation through hardware acceleration, (3) in-circuit emulation (ICE), and (4) post-sinulation analysis, including their respective set-up or pre-processing stages. At other times, the term “SEmulation” may be used. This term refers to the novel processes described herein.

[0128] Similarly, terms such as “Reconfigurable Computing (RCC) Array System” or “RCC computing system” refers to that portion of the simulation / coverification system that contains the main processor, software kernel and the software model of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More