Process for making a CMOS image sensor

a cmos image sensor and processing technology, applied in the field of image sensors, can solve the problems of reducing the quantum efficiency of the image sensor, the possibility of a low success rate, and the optical sensitivity of the image sensor dropping, so as to reduce the increase the quantum efficiency, and reduce the effect of absorption or reflective loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

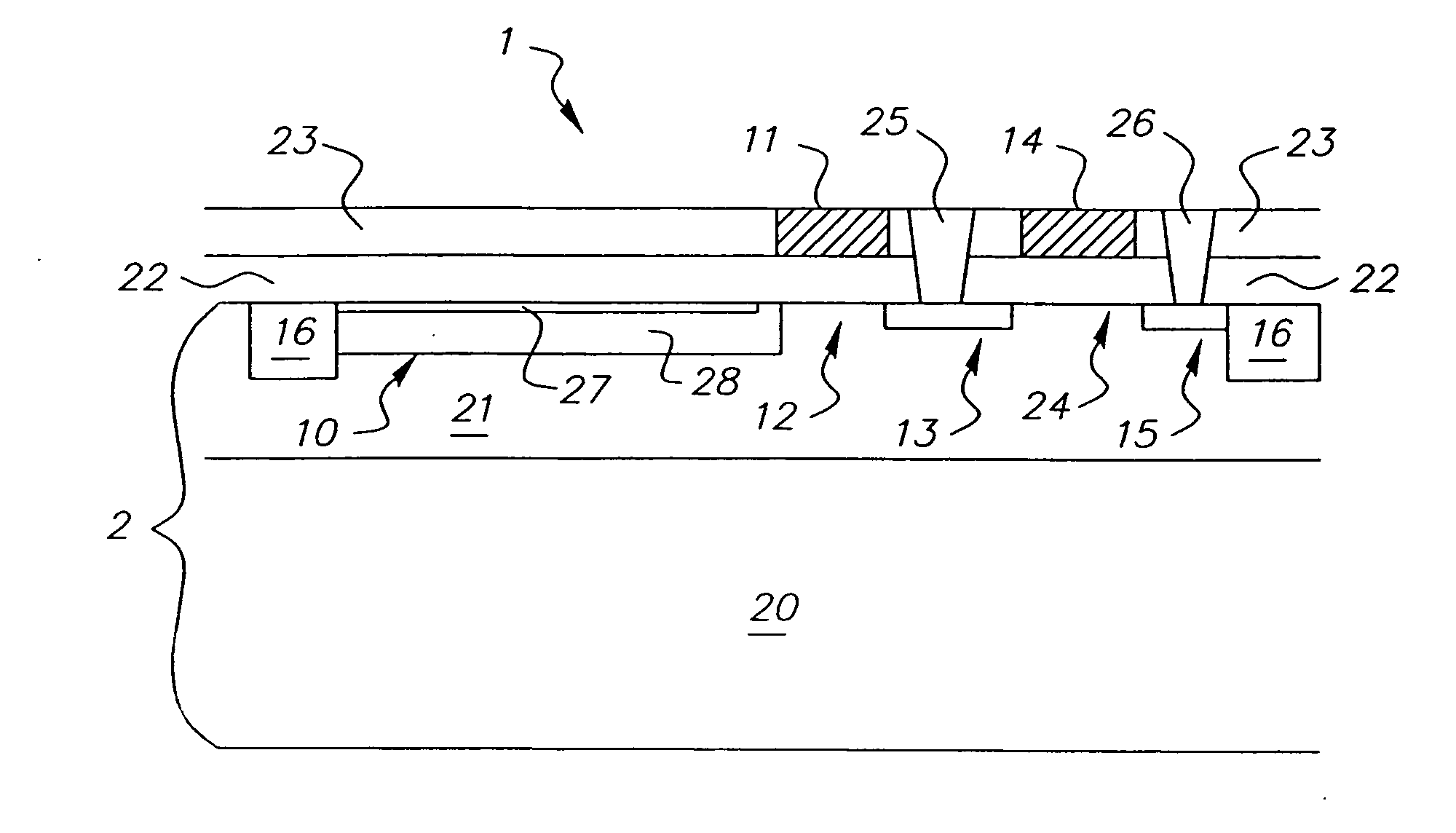

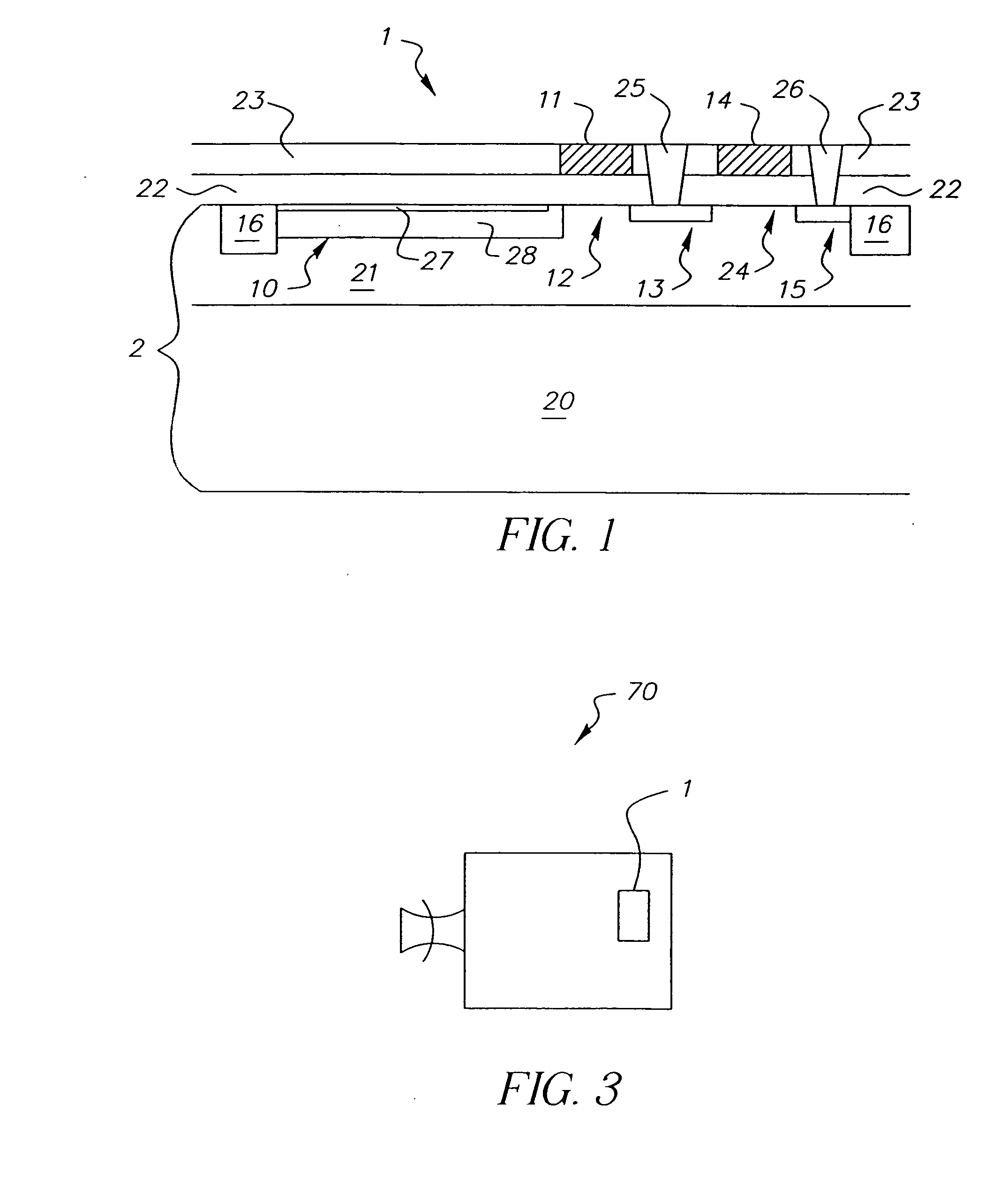

[0012] Referring to FIGS. 1 and 2, there is shown a CMOS image sensor 1 of the present invention. Although a CMOS image sensor is shown as a preferred embodiment, the present invention applies to any suitable image sensor such as a charge coupled device (CCD). The present invention is also preferably implemented on a silicon on insulator wafer which consists of a layer of silicon overlayer 23 on a layer of silicon dioxide 22 which rests on a thick silicon substrate 2. The thick silicon substrate 2 includes two doping regions comprising a first 20 and second layer 21. The second layer region 21 is preferable an epitaxial region. A dielectric layer 22 spans and covers the epitaxial region 21. The silicon overlayer 23 covers and spans the dielectric layer 22. The silicon overlayer 23 is preferably made of a single crystal and is preferably less than 1 micrometer in thickness.

[0013] A pinned photodiode 10 having a p+ layer 27 and an n layer 28 is disposed in the epitaxial layer 21. The...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More