Method for fabricating an integrated circuit comprising a three-dimensional capacitor

a three-dimensional capacitor and integrated circuit technology, applied in the field of integrated circuits, can solve problems such as the dispersion of the capacitive values of theoretically identical capacitors, and achieve the effect of reducing the access resistance of the capacitor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

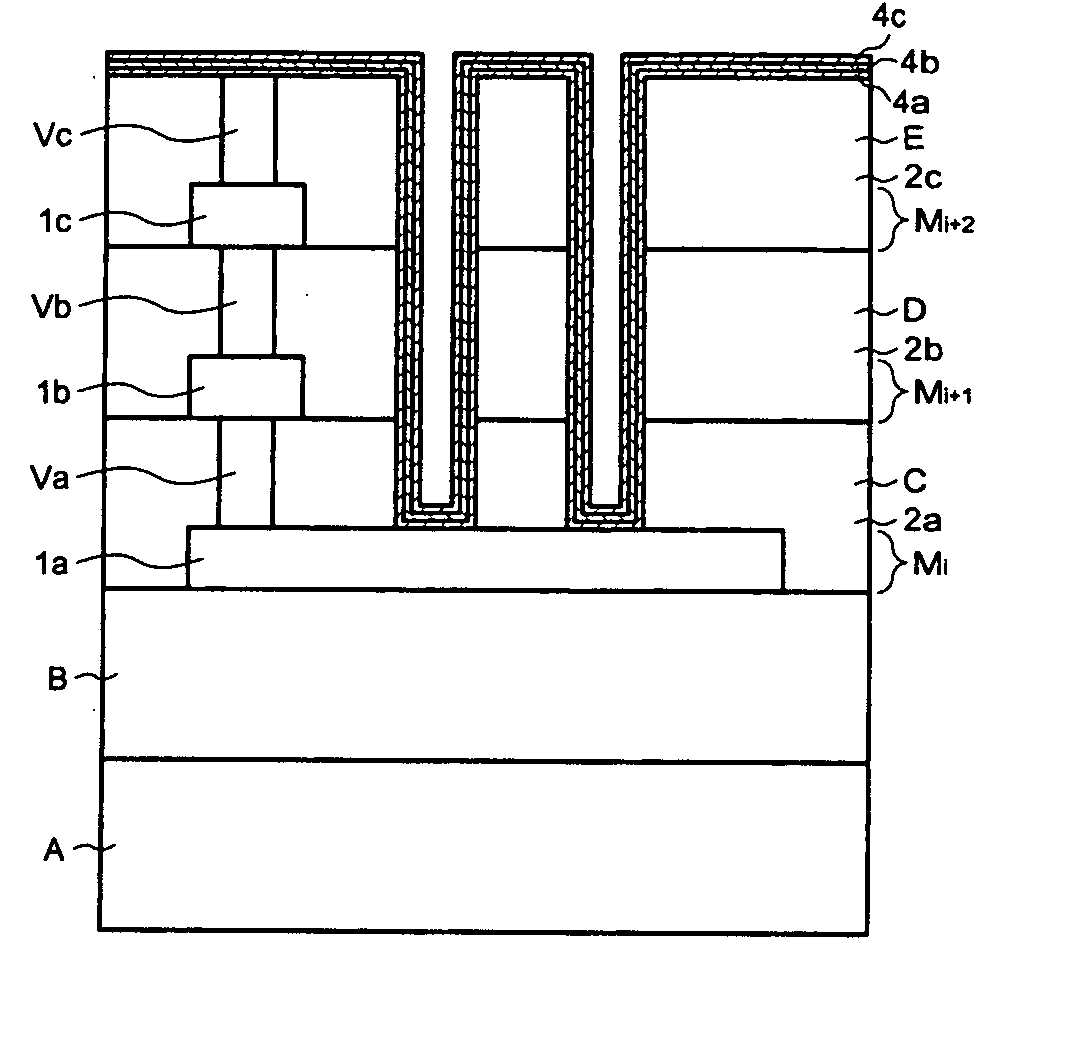

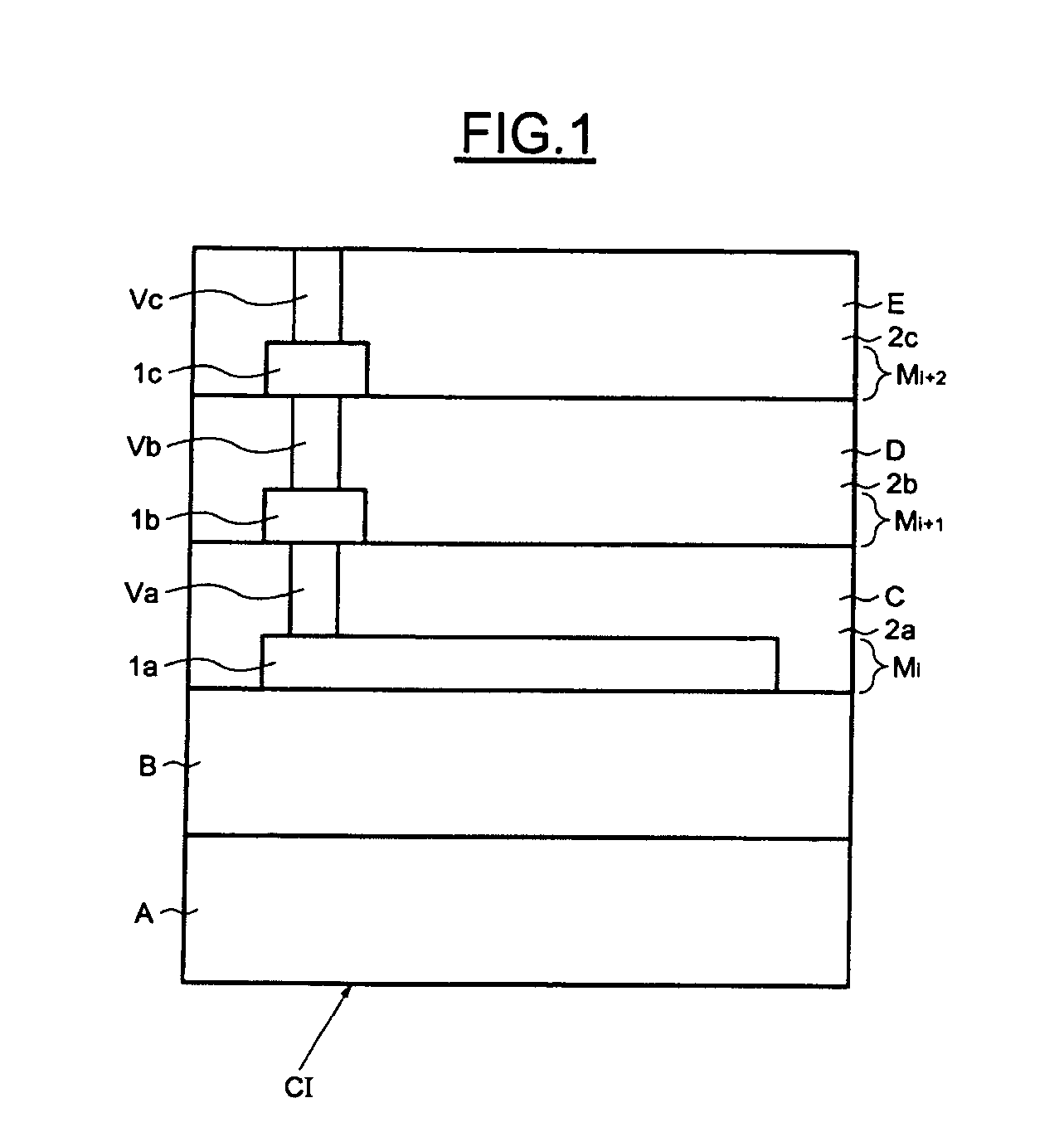

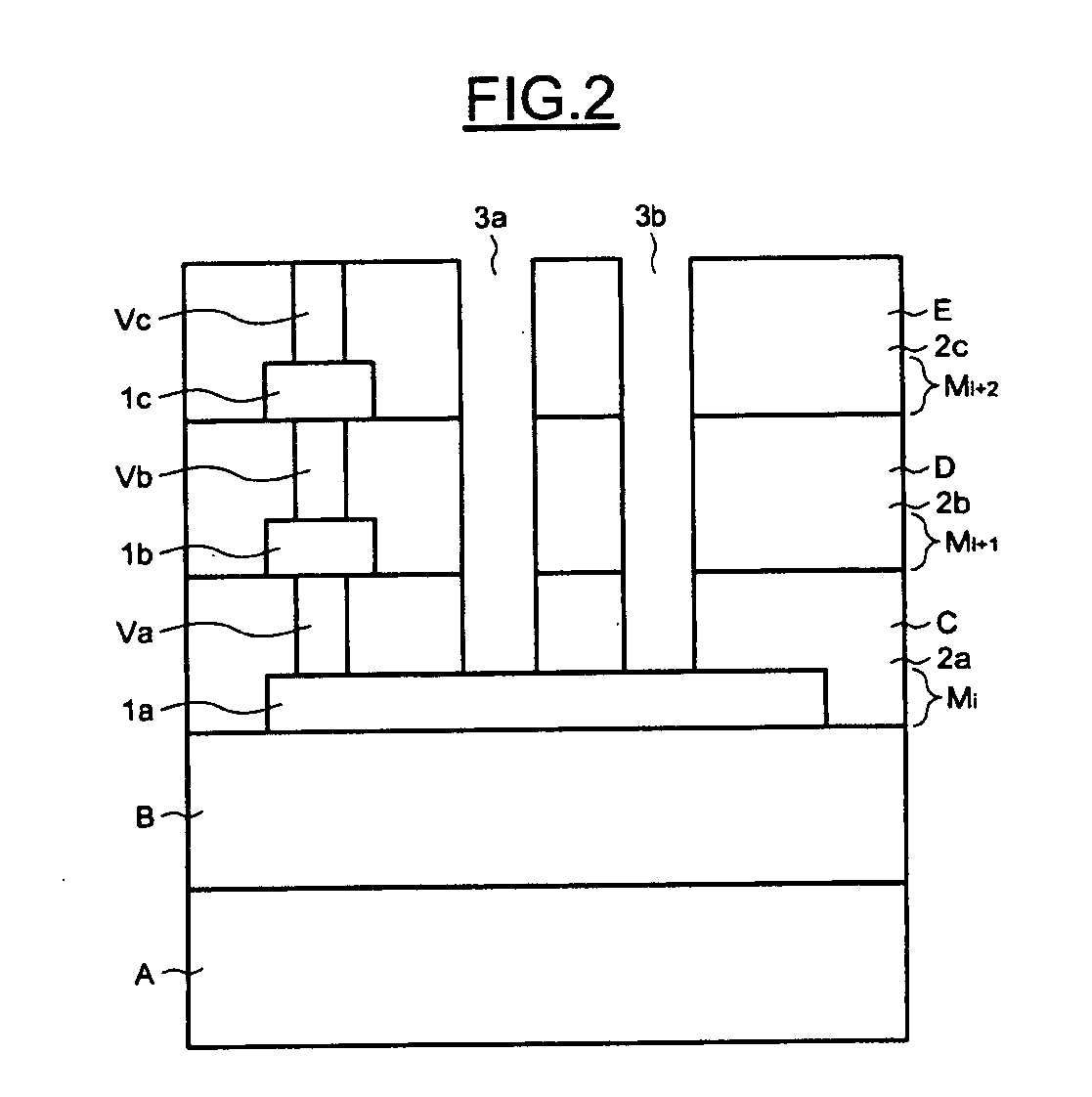

[0018]FIG. 1 represents an integrated circuit CI comprising a silicon substrate A on which a dielectric layer B has been deposited. A plurality of interconnection levels C, D and E rest on the dielectric layer B. Each interconnection level includes a metallization level formed by metal tracks and a level of vias, all of this coated in a dielectric material. The production of each interconnection level is conventional and known per se by those skilled in the art. In the example described here, the metallization level Mi of the interconnection level C comprises a metal layer 1a. The layer 1a may be of aluminum or copper. The metallization level Mi+1 of the interconnection level D comprises an interconnection line, or track 1b. The metallization level Mi+2 of the interconnection level E comprises an interconnection line, or track 1c. The interconnection lines 1a, 1b, 1c of the various interconnection levels C, D, E are connected to one another by the vias Va, Vb, Vc formed in the diele...

PUM

| Property | Measurement | Unit |

|---|---|---|

| distance | aaaaa | aaaaa |

| conductive | aaaaa | aaaaa |

| electrically | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More