Method for fabricating semiconductor device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

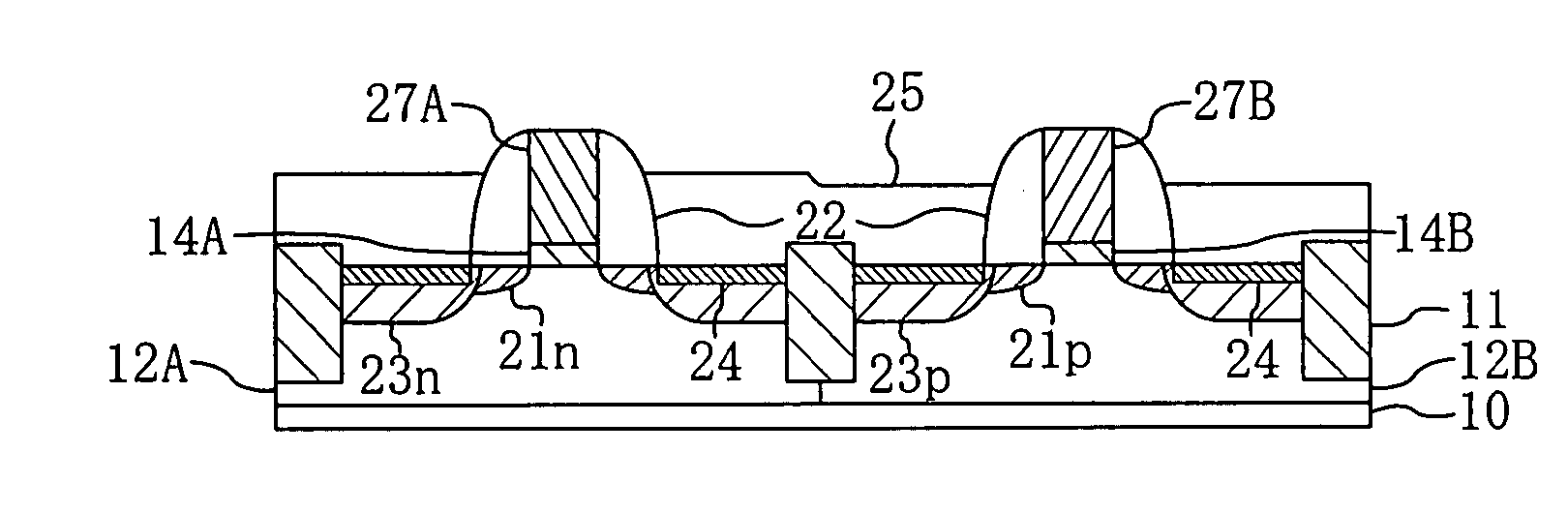

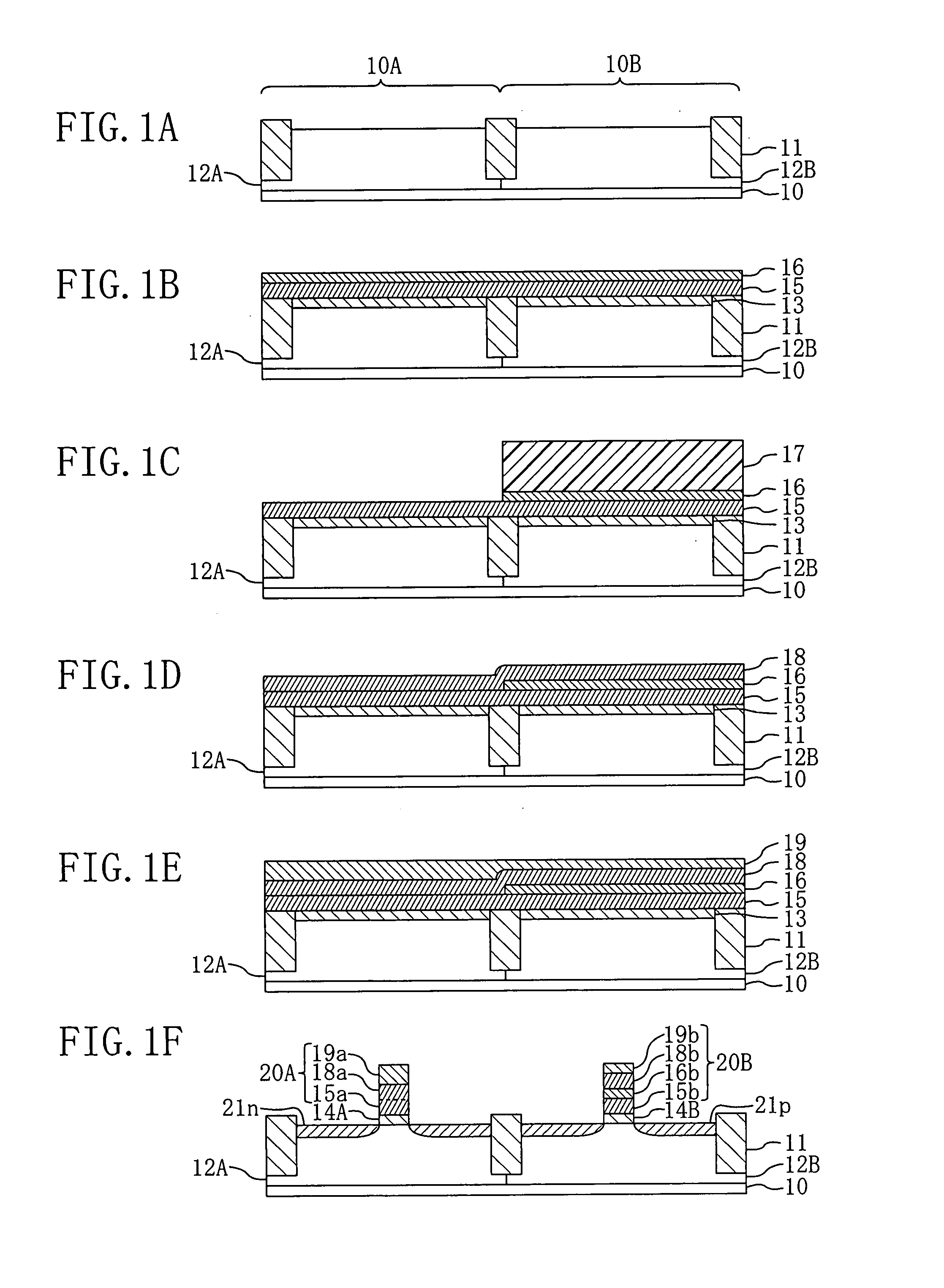

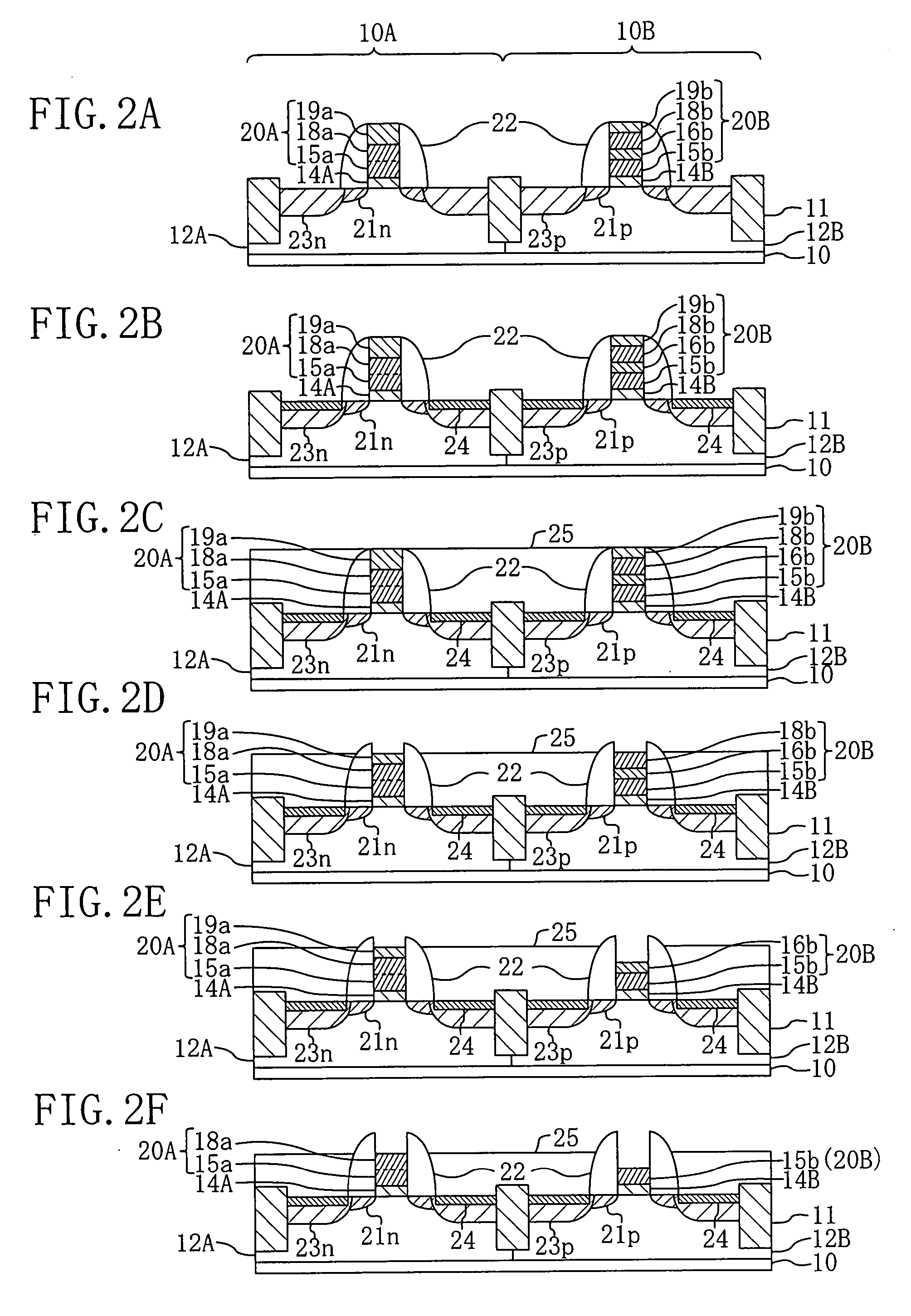

[0037] One embodiment of the present invention will be described with reference to the accompanying drawings. FIGS. 1 to 3 show cross-sectional structures of successive fabrication process steps of a method for fabricating a semiconductor device according to one embodiment. In this embodiment, description will be made of a method for fabricating n- and p-type MIS transistors in first and second regions 10A and 10B, respectively.

[0038] Referring to FIG. 1A, first, on a semiconductor substrate 10 made of, for example, p-type silicon, an isolation region 11 for electrically isolating elements is provided by an STI (shallow trench isolation) method or the like to form the first region 10A and the second region 10B. Then, by a lithography method and an ion implantation method, a p-type first well 12A and an n-type second well 12B are formed in the upper portion of the first region 10A and the second region 10B, respectively.

[0039] Next, as shown in FIG. 1B, in a region of the main surf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More