Semiconductor device and manufacturing method of the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

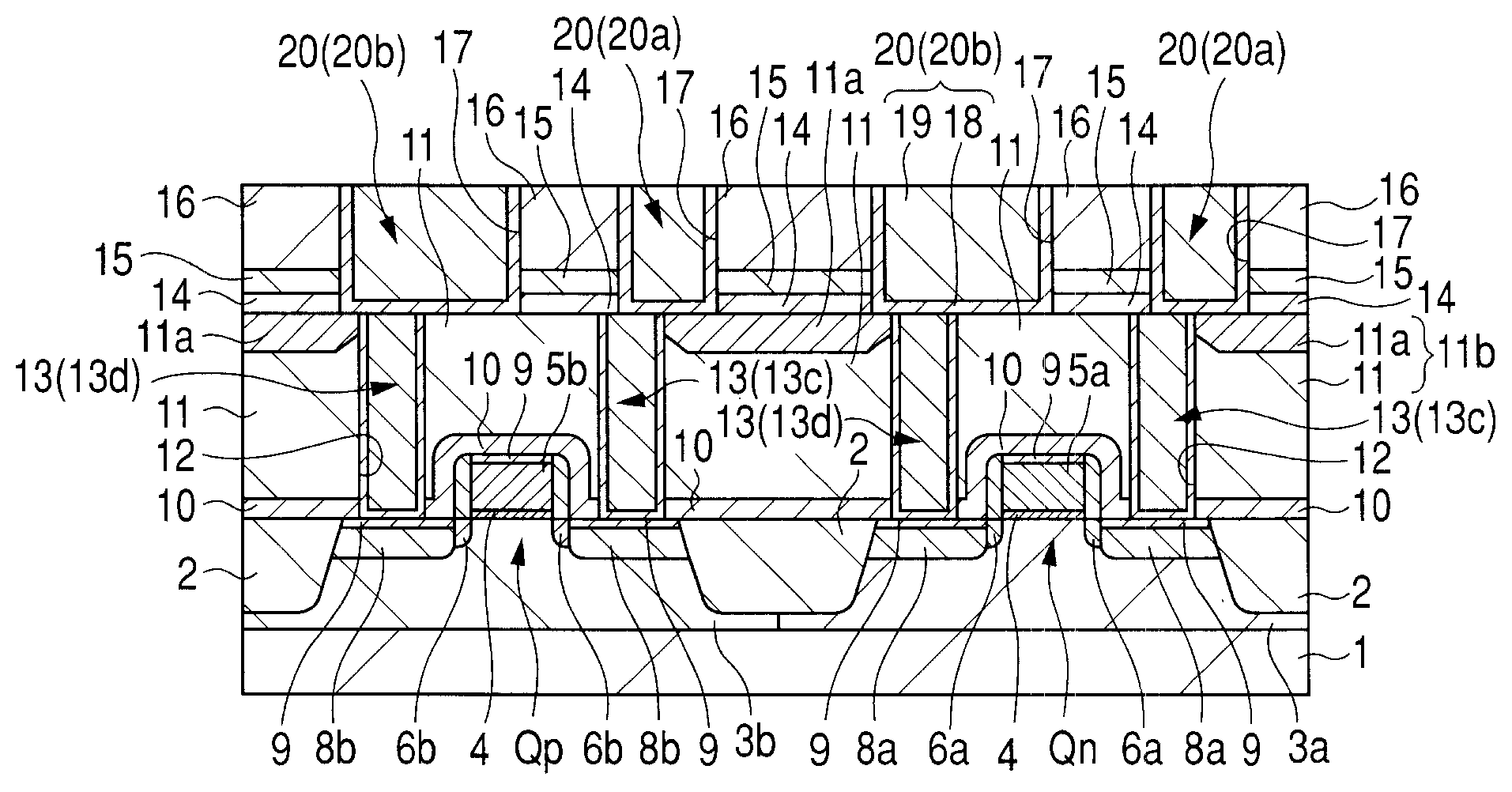

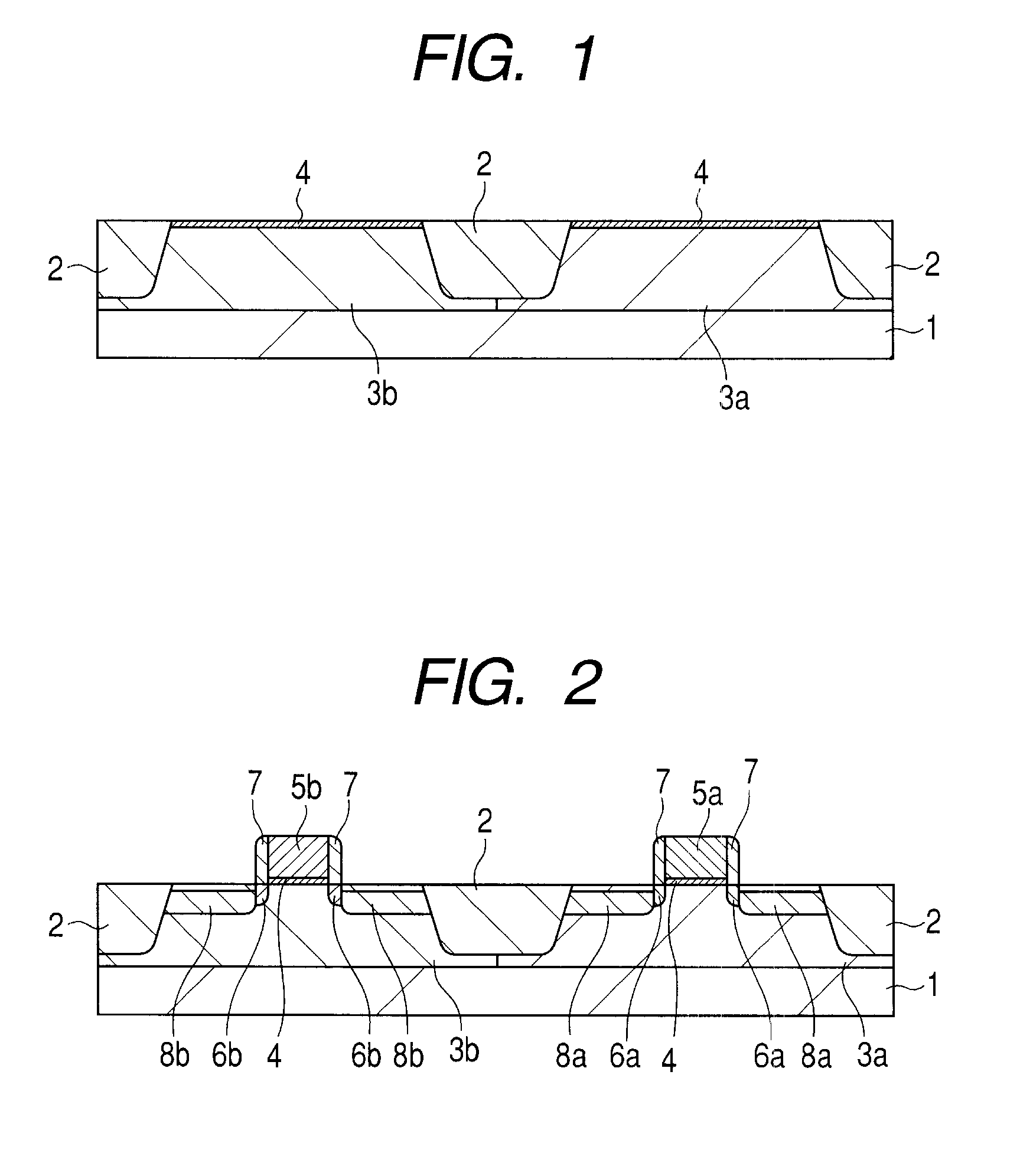

[0046]Semiconductor devices according to the preferred embodiments and their manufacturing process will be described with reference to the drawings. FIG. 1 to FIG. 14 are sectional views of essential parts in the manufacturing process of a semiconductor device according to an embodiment, for example, a semiconductor device having a MISFET (Metal Insulator Semiconductor Field Effect Transistor).

[0047]In order to manufacture a semiconductor device according to the present embodiment, first, a semiconductor substrate (semiconductor wafer) 1 including a p-type single crystal silicon etc. having a specific resistance of about, for example, 1 to 10 Ω·cm is prepared. Then, an element isolation region 2 is formed in the main surface of the semiconductor substrate 1. The element isolation region 2 includes silicon oxide etc. and can be formed by, for example, the STI (Shallow Trench Isolation) method or the LOCOS (Local Oxidization of Silicon) method.

[0048]Next, a p-type well 3a is formed in...

second embodiment

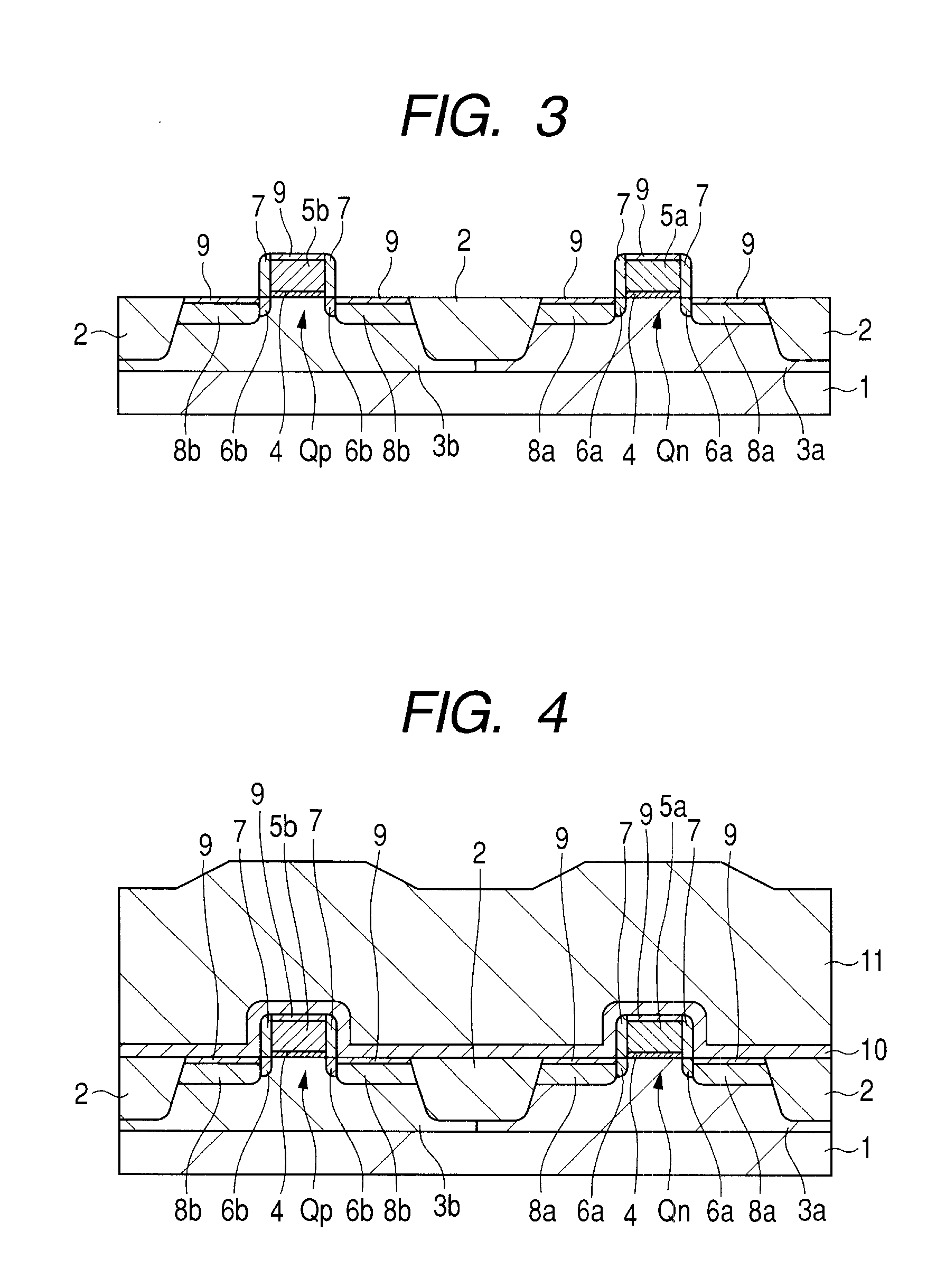

[0146]FIG. 19 to FIG. 23 are cross-sectional views of essential parts in a manufacturing process of a semiconductor device according to the present embodiment. The processes up to that in FIG. 4 are substantially the same as those in the first embodiment described above, and therefore, their description is omitted here and subsequent processes that follow that in FIG. 4 are described.

[0147]After substantially the same structure as that in FIG. 4 is obtained by carrying out the processes up to the film forming process of the insulating film 11 in the same manner as that in the first embodiment, in the present embodiment, an insulating film 11a (sixth insulating film) 11a is formed over the insulating film (first insulating film) 11, as shown in FIG. 19. The insulating film 11a includes a silicon oxide film formed by the plasma CVD method. Since the gap between gate electrodes 5a, 5b is filled with the insulating film 11, no problem about embeddability will arise even if the insulatin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More