Structure and Method of Sub-Gate NAND Memory with Bandgap Engineered SONOS Devices

a sonos device and sub-gate technology, applied in semiconductor devices, transistors, instruments, etc., can solve the problems of large vt distribution of erase state, difficult to erase, and high threshold cell charge loss, and achieve excellent charge retention, eliminate inter-floating gate coupling effect, and improve scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

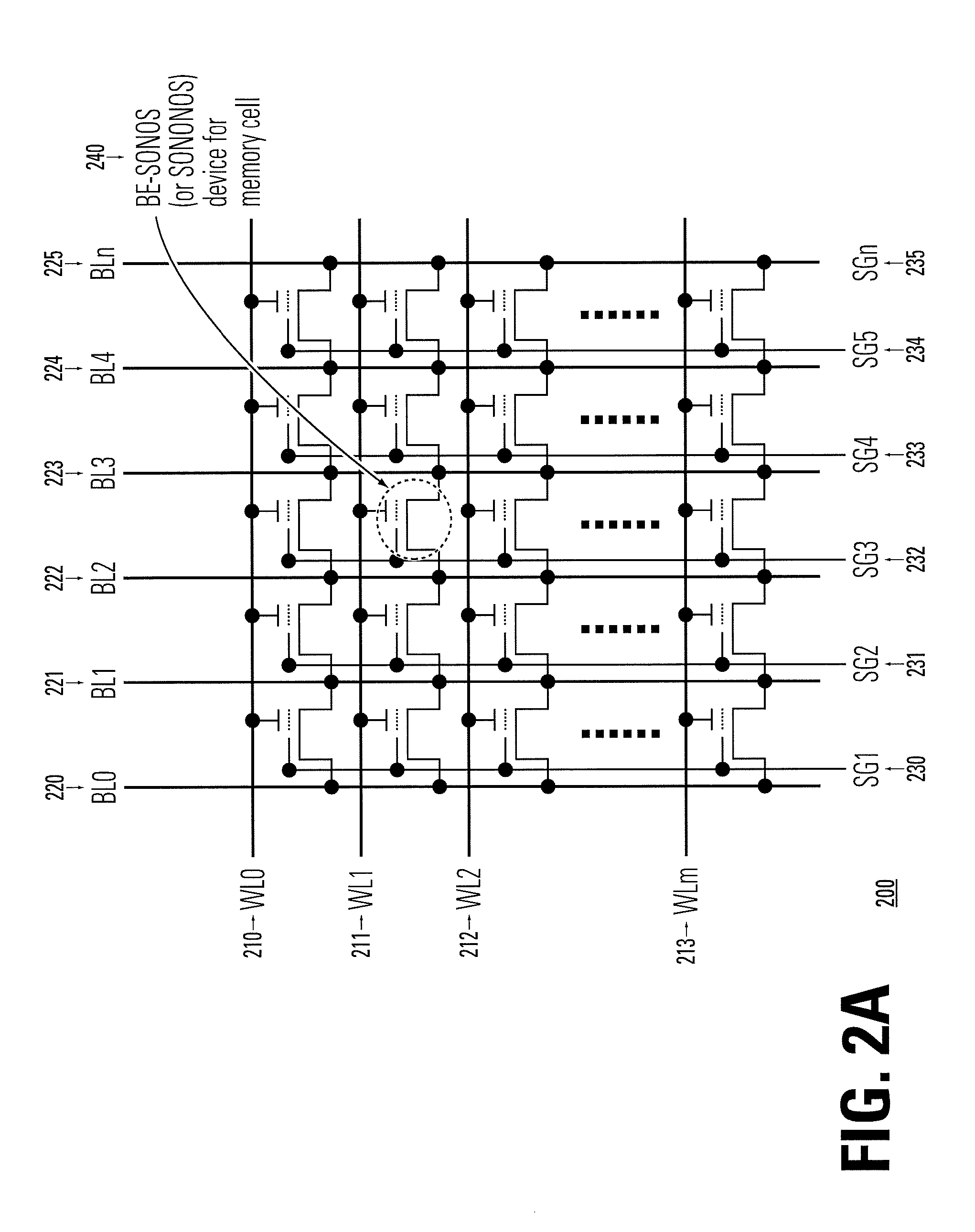

[0069]In FIG. 2A, there is shown a circuit diagram illustrating a BE-SONOS SG-AND array architecture 200 with diffusion bitlines. A plurality of SONONOS devices are connected in parallel to form the BE-SONOS SG-AND array architecture 200. The BE-SONOS array architecture 200 comprises a plurality of wordlines WL0210, WL1211, WL2212, WLm 213 intersecting a plurality of bitlines BL0220, BL1221, BL2222, BL3223, BL4224 and BLn 225. A corresponding sub-gate line is parallel and located nearby a bitline. A sub-gate SG1230 is located adjacent to the bitline BL0220. A sub-gate SG2231 is located adjacent to the bitline BL1221. A sub-gate SG3232 is located adjacent to the bitline BL2222. A sub-gate SG4233 is located adjacent to the bitline BL3223. A sub-gate SG5234 is located adjacent to the bitline BL4224. A sub-gate SGn 235 is located adjacent to the bitline BL5225. A sample BE-SONOS (or SONONOS) device 240 that functions as a memory cell is shown in a circled area.

[0070]As shown in FIG. 2B,...

second embodiment

[0087]In FIG. 10A, there is a circuit diagram illustrating an electrical reset of the SONONOS SGIB-AND array architecture 1000 in the During the electrical reset, the wordlines (or gates) WL0810, WL1811, WL2812, and WLm 813 are set to −10 volts, the bitlines BL0820, BL1821, BL2822, BL3823, BL4824 and BL5825 are left floating, the sub-gates SG0830, SG1831, SG2832, SG3833, SG4834, and SGn 835 are set to 0 volt, and P-well 1010 is set to 5 volts. When a sub-gate SG=is equal to zero volt, that means the SG is not turned on so that there is no inversion bitline. In one embodiment, every fourth sub-gates are connected together such that SG0830 is connected to SG4, SG1831 is connected to SG5, and so on.

[0088]Before operations, the memory circuit 1000 is reset by applying Vgb=−15V (or partition the gate voltage into each WL and p-well), which produces a desirable self-converging property, as shown in the graph 1050 in FIG. 10B. Various circles and triangles in the graph 1050 represent diff...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More