Ultra low power memory cell with a supply feedback loop configured for minimal leakage operation

a low power consumption, random access technology, applied in the direction of information storage, static storage, digital storage, etc., can solve the problems of increasing the cost of performance loss, and increasing the difficulty of maintaining functionality, so as to reduce the flow of leakage currents and maintain the readability of the memory cell

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018]The following description is presented to enable a person skilled in the art to make and use the invention. Various modifications to the embodiments will be readily apparent to those skilled in the art, and the generic principles herein may be applied to other embodiments and applications without departing from the spirit and scope of the present invention. Thus, the present invention is not intended to be limited to the embodiments shown, but is to be accorded the widest scope consistent with the principles and features disclosed herein.

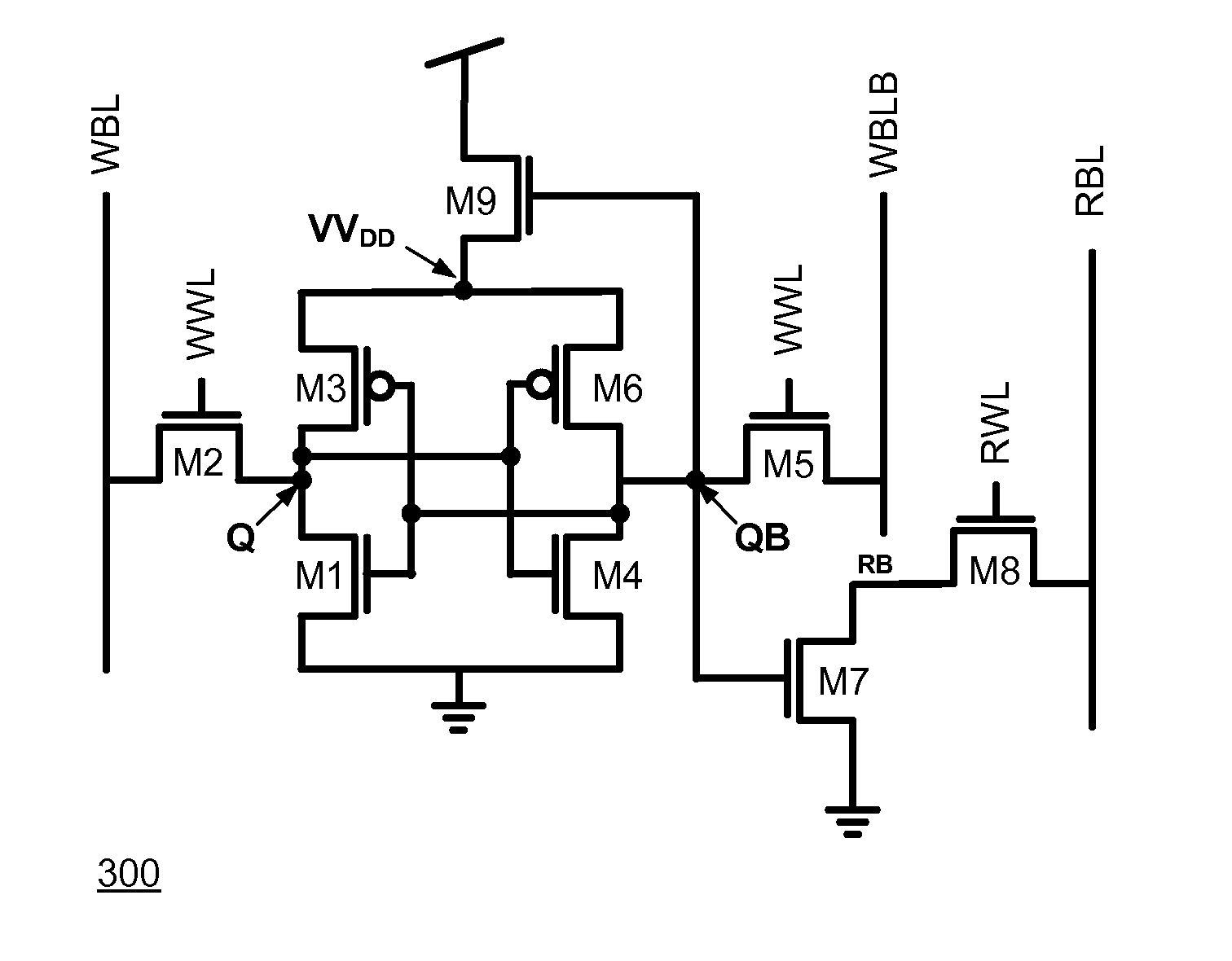

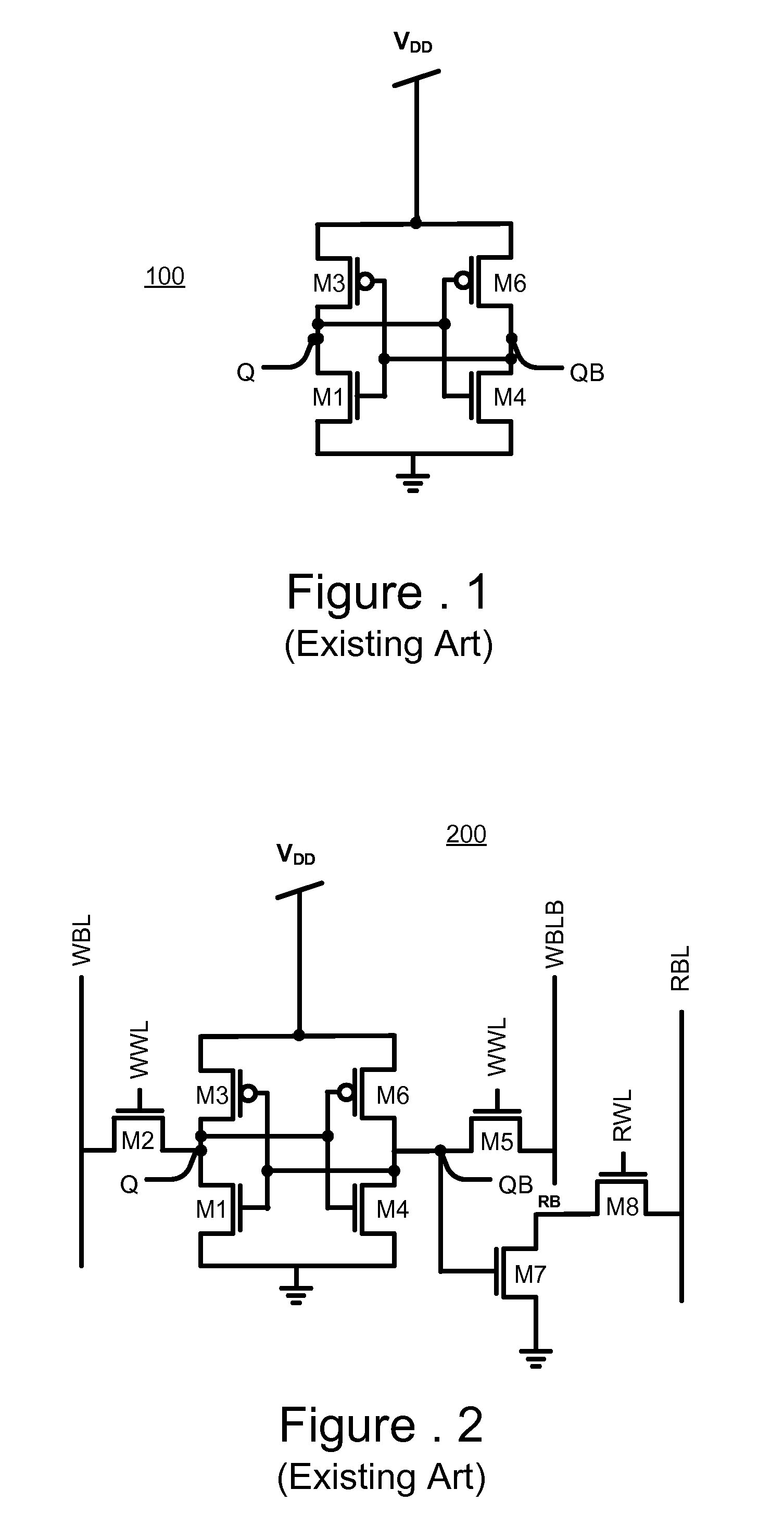

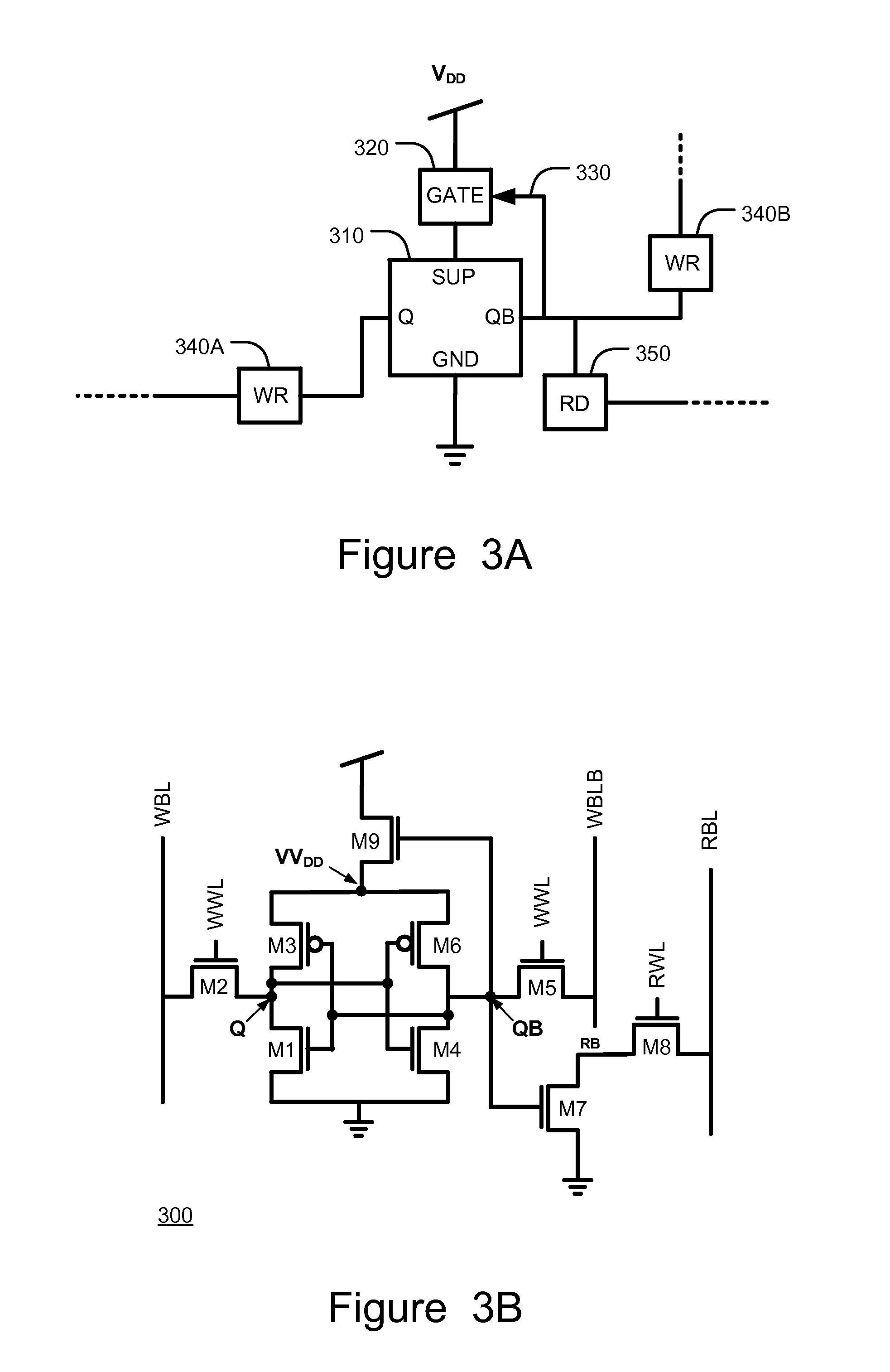

[0019]FIG. 3A is a schematic block diagram of a memory cell according to an exemplary non-limiting embodiment of the present invention. The memory cell may include a latch 310 having a storage node Q, a storage node QB, a supply node SUP, and a ground node GND. Supply node SUP is coupled via a gating device 320 to a supply voltage VDD and ground node GND is connected to ground. In addition, storage node QB is fed back via feedback loop 330 int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More