Transistor structure and related transistor packaging method thereof

a technology of transistors and transistors, applied in the direction of semiconductor devices, electrical devices, semiconductor/solid-state device details, etc., can solve the problems of high energy loss, damage to semiconductor elements, poor efficiency and high spike voltage value, etc., and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

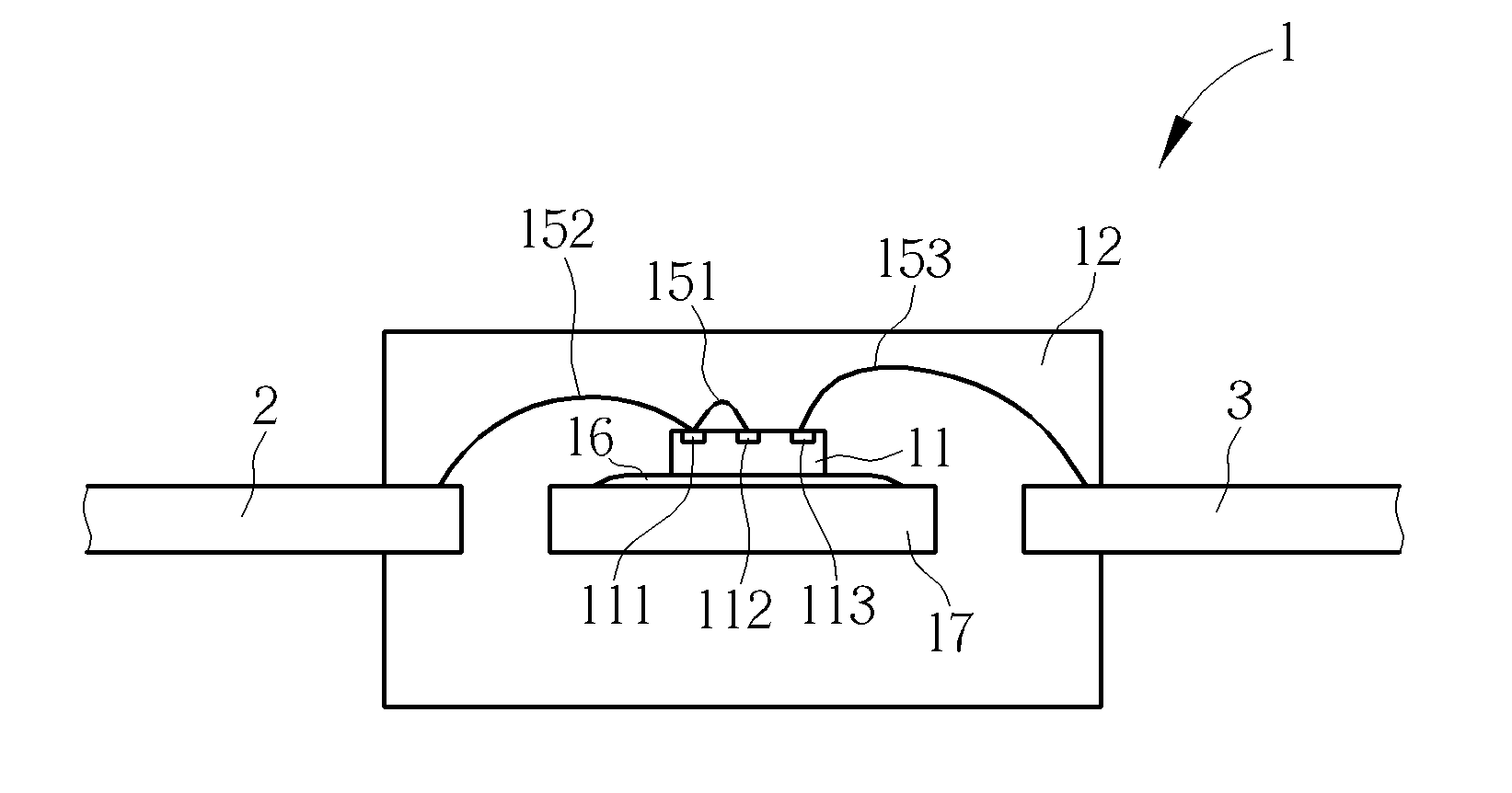

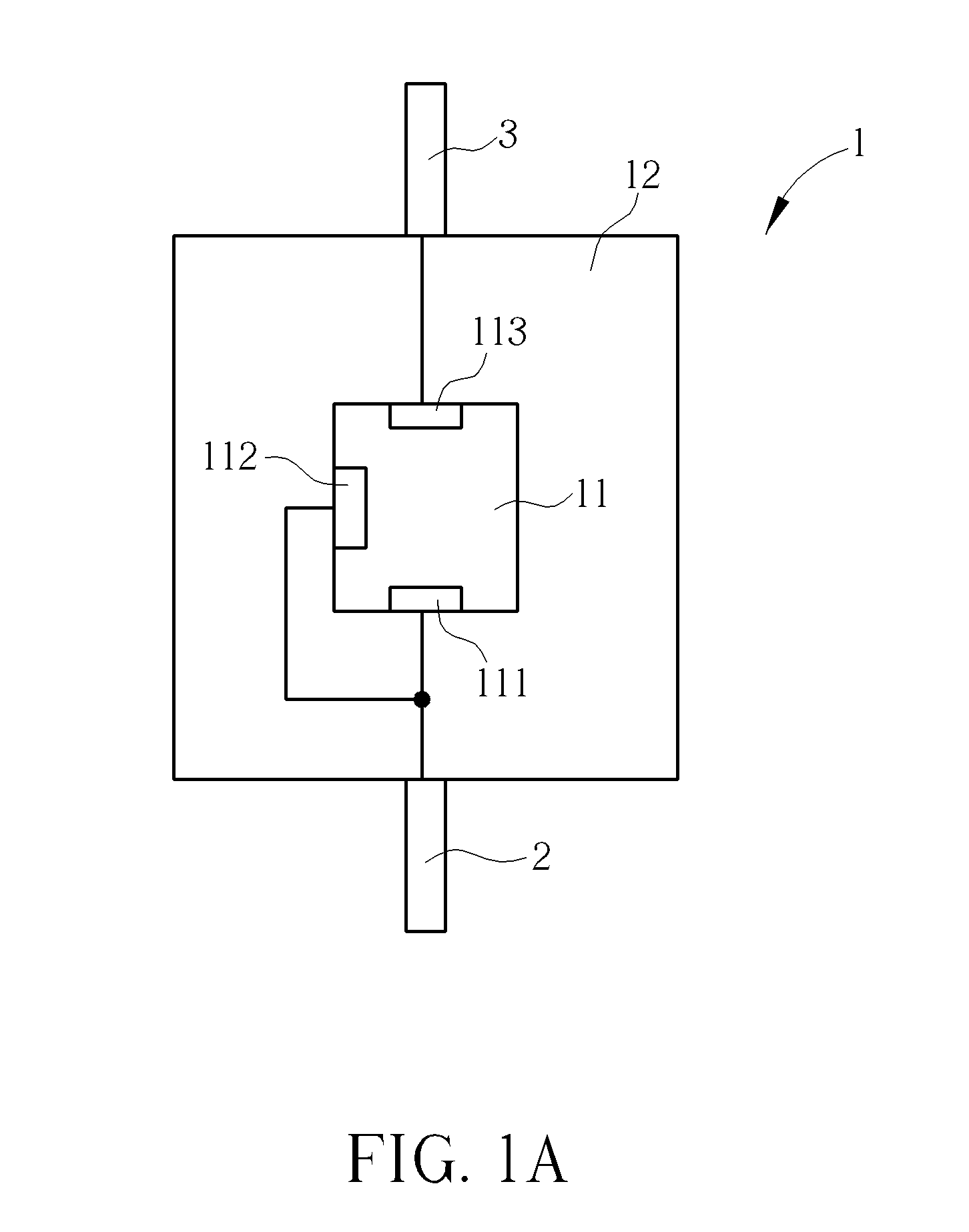

[0054]Please refer to FIG. 1A, which is a diagram illustrating a transistor structure according to the present invention. The transistor structure of the present invention includes a chip package 1 and two pins 2 and 3, wherein the chip package 1 includes a transistor die 11 and a molding compound 12 encapsulating the transistor die 11; and the pin 2 is electrically connected to a first bonding pad 111 and a second bonding pad 112 of the transistor die 11, and the pin 3 is electrically connected to a third bonding pad 113 of the transistor die 11.

[0055]The transistor die 11 of the transistor structure of the present invention is a Bipolar Junction Transistor (BJT) die, and the BJT may be an NPN type BJT die or a PNP type BJT die. Please refer to FIG. 1 in conjunction with FIG. 2A and FIG. 2B. The first bonding pad 111 of the transistor die 11 is an emitter bonding pad, and the second bonding pad 112 is a base bonding pad, and the third bonding pad 113 is a collector bonding pad, whe...

second embodiment

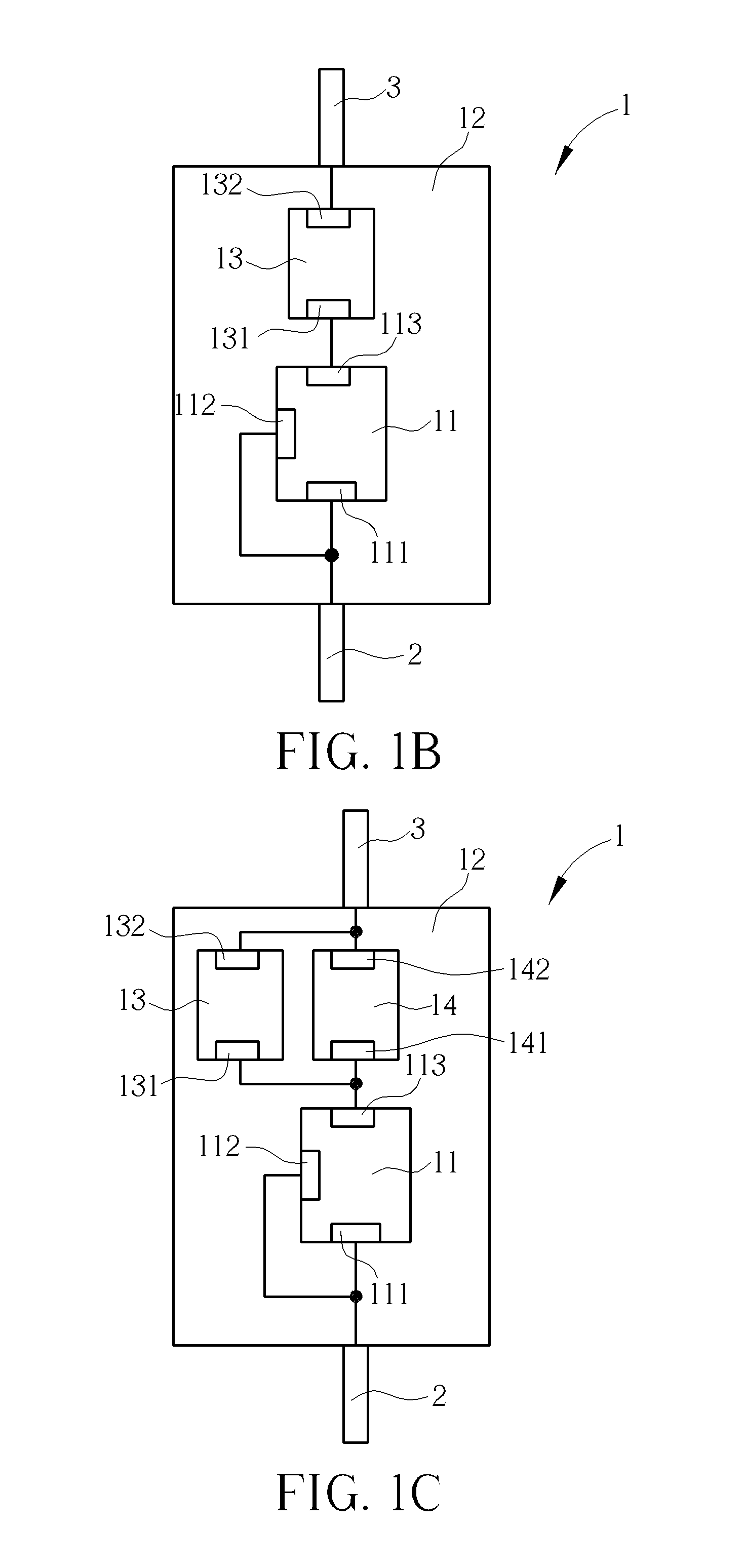

[0061]Please refer to FIG. 1B, which is a diagram illustrating a transistor structure according to the present invention. The transistor structure of the present invention includes a chip package 1 and two pins 2 and 3, wherein the chip package 1 includes a transistor die 11, a capacitor die 13, and a molding compound 12 encapsulating the transistor die 11 and the capacitor die 13. The third bonding pad 113 of the transistor die 11 is electrically connected to a first bonding pad 131 of the capacitor die 13. The pin 2 is electrically connected to a first bonding pad 111 and the second bonding pad 112 of the transistor die 11, and the pin 3 is electrically connected to a second bonding pad 132 of the capacitor die 13. The transistor structure of this embodiment may make the first bonding pad 111 (or the second bond 112) of the transistor die 11 electrically connected to the first bonding pad 131 of the capacitor die 13, may make the pin 2 electrically connected to the second bonding ...

third embodiment

[0064]Please refer to FIG. 1C, which is a diagram illustrating the transistor structure according to the present invention. The transistor structure of the present invention includes a chip package 1 and two pins 2 and 3, wherein the chip package 1 includes a transistor die 11, a capacitor die 13, a zener diode die 14, and a molding compound 12 encapsulating the transistor die 11, the capacitor die 13, and the zener diode die 14. The third bonding pad 113 of the transistor die 11 is electrically connected to a first bonding pad 131 of the capacitor die 13 and a first bonding pad 141 of the zener diode die 14. The pin 2 is electrically connected to a first bonding pad 111 and the second bonding pad 112 of the transistor die 11, and the pin 3 is electrically connected to a second bonding pad 132 of the capacitor die 13 and a second bonding pad 142 of the zener diode die 14. The transistor structure of this embodiment may make the first bonding pad 111 and the second bonding pad 112 of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More