Circuits and methods for fault testing

a fault testing and circuit technology, applied in the field of electronic circuits, can solve problems such as signal delay faults, failures to detect faults, and failures to occur after the ic, and achieve the effect of significant ate and/or interface complexity and cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

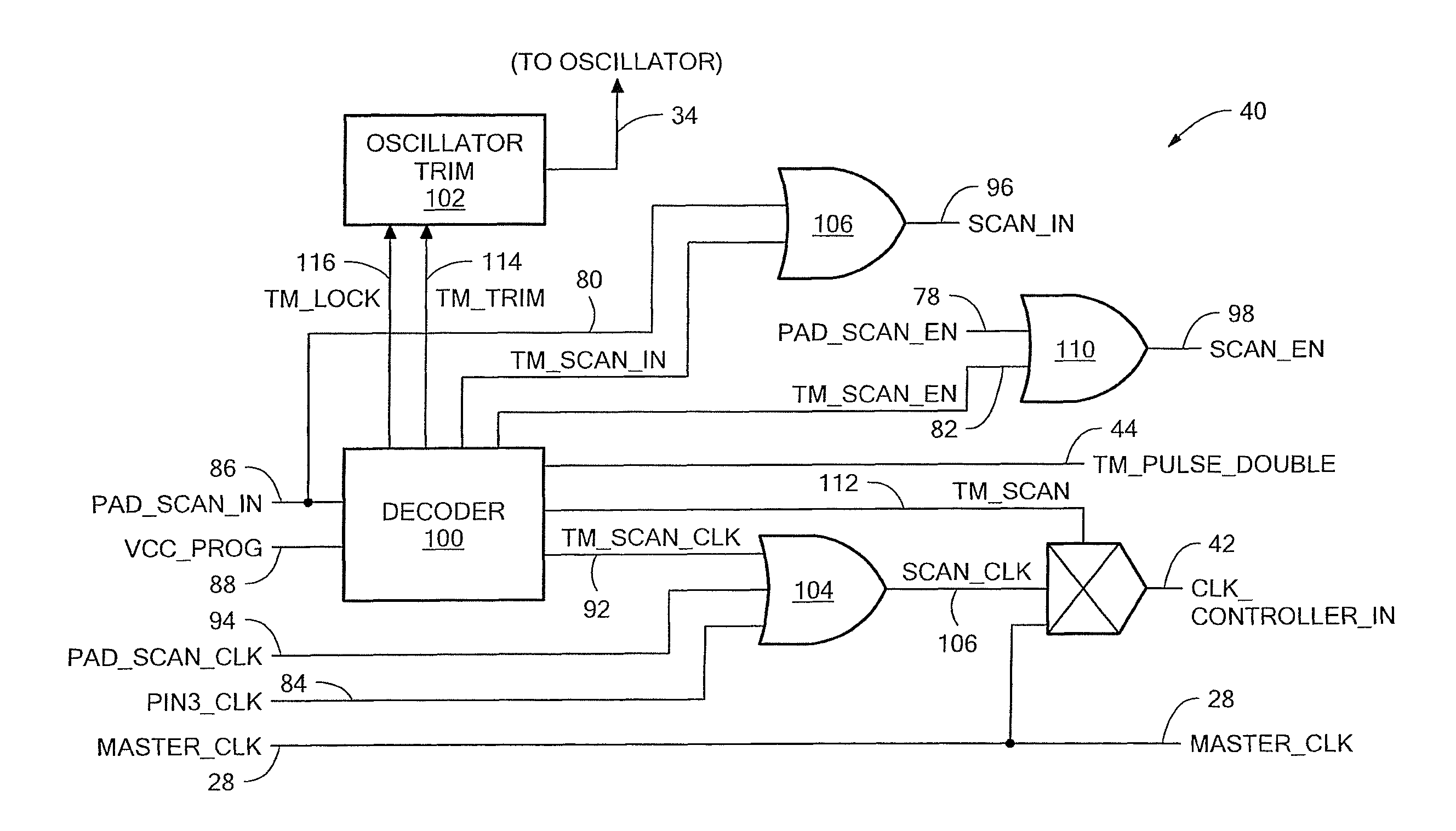

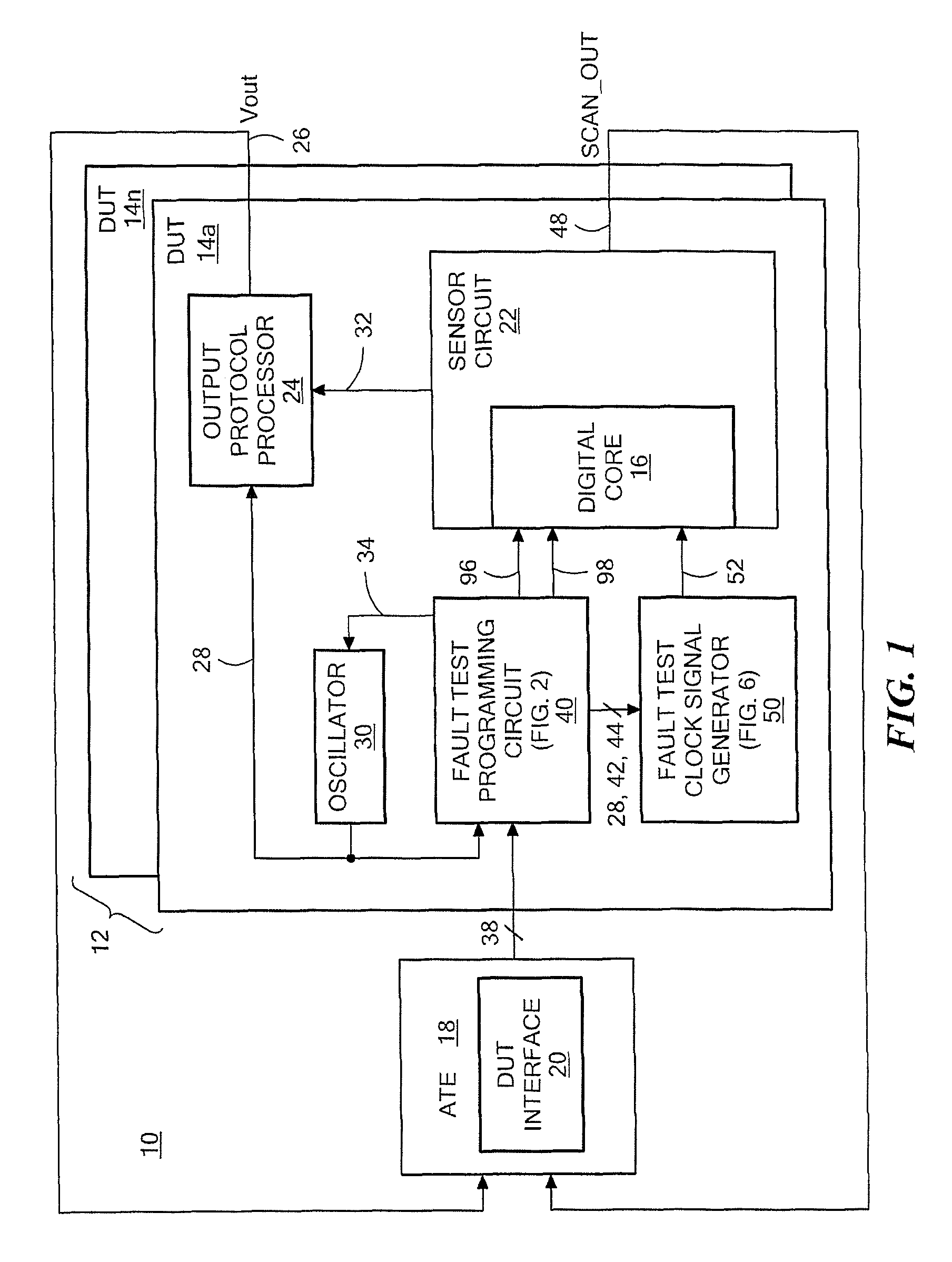

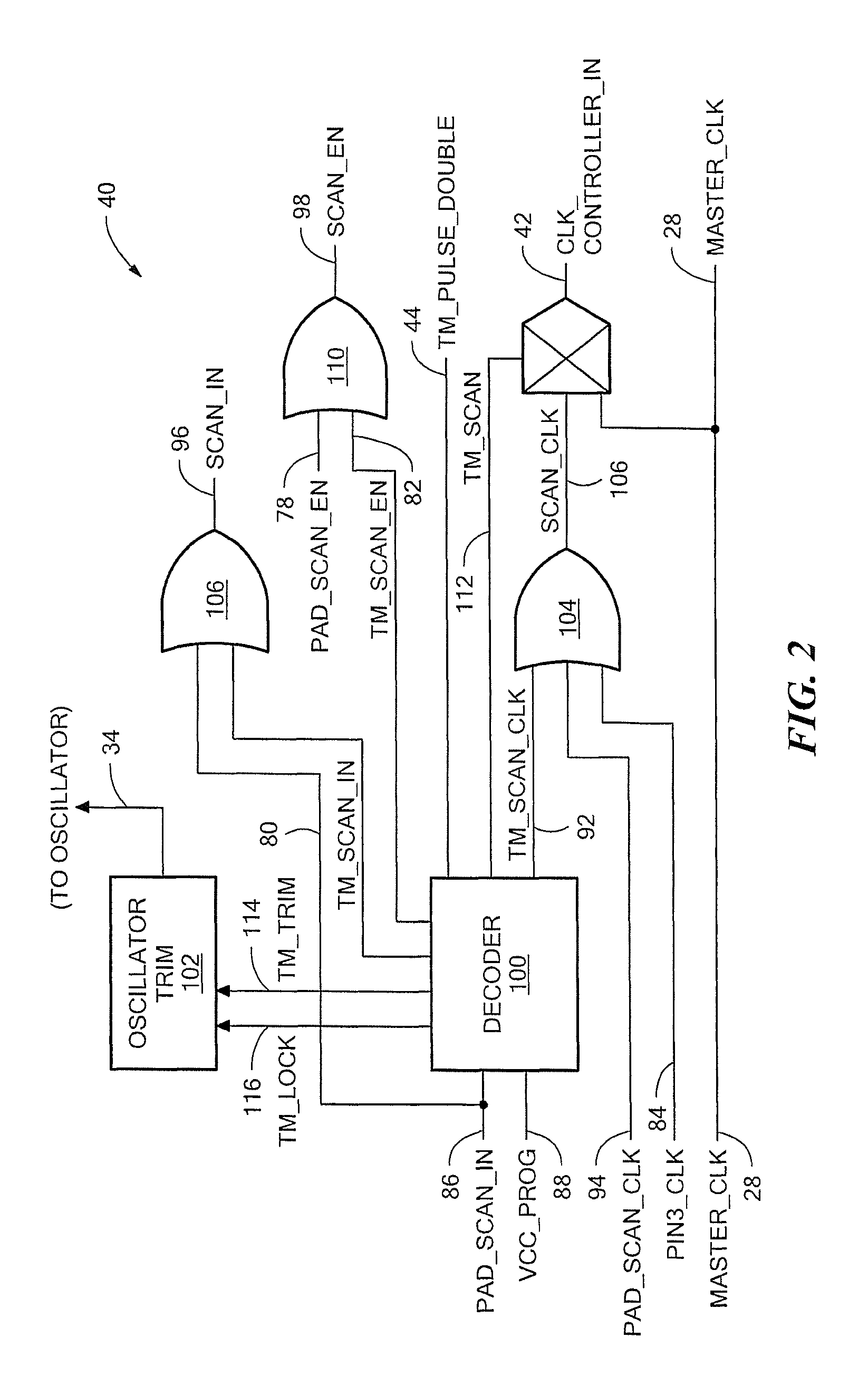

[0021]Referring to FIG. 1, a test system 10 for testing one or more electronic circuit devices, or Devices Under Test (DUTs) 14a-14n, is shown. The DUTs 14a-14n may take the form of semiconductor ICs or ASICs for a variety of applications, each including a digital core 16 for which fault testing is desired. Fault testing may be performed during a stage of manufacture when a semiconductor wafer 12 supports the DUTs 14a-14n (i.e., wafer level testing). An Automatic Test Equipment (ATE) unit 18 including a DUT interface 20 is coupled to the wafer 12 for this purpose. It may also be desirable to perform testing on each individual DUT 14a-14n after the wafer is diced and the DUTs are individually packaged in which case the ATE 18 (or an alternative less complex ATE) is coupled to the individual DUT 14a for example.

[0022]In the illustrative embodiment, each DUT 14a-14n (as shown and described in conjunction with illustrative DUT 14a which is referred to herein alternatively as sensor IC 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More