Load reduced memory module and memory system including the same

a memory module and load reduction technology, applied in the field of memory modules and memory systems, can solve the problems of increasing the capacity of a data line on the motherboard, reducing signal quality, and difficult to provide the required memory capacity with a single memory module, and achieves the effects of enhancing signal quality, reducing the length of the line between the data register buffer and the memory chip, and enhancing signal quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044]Preferred embodiments of the present invention will be explained below in detail with reference to the accompanying drawings.

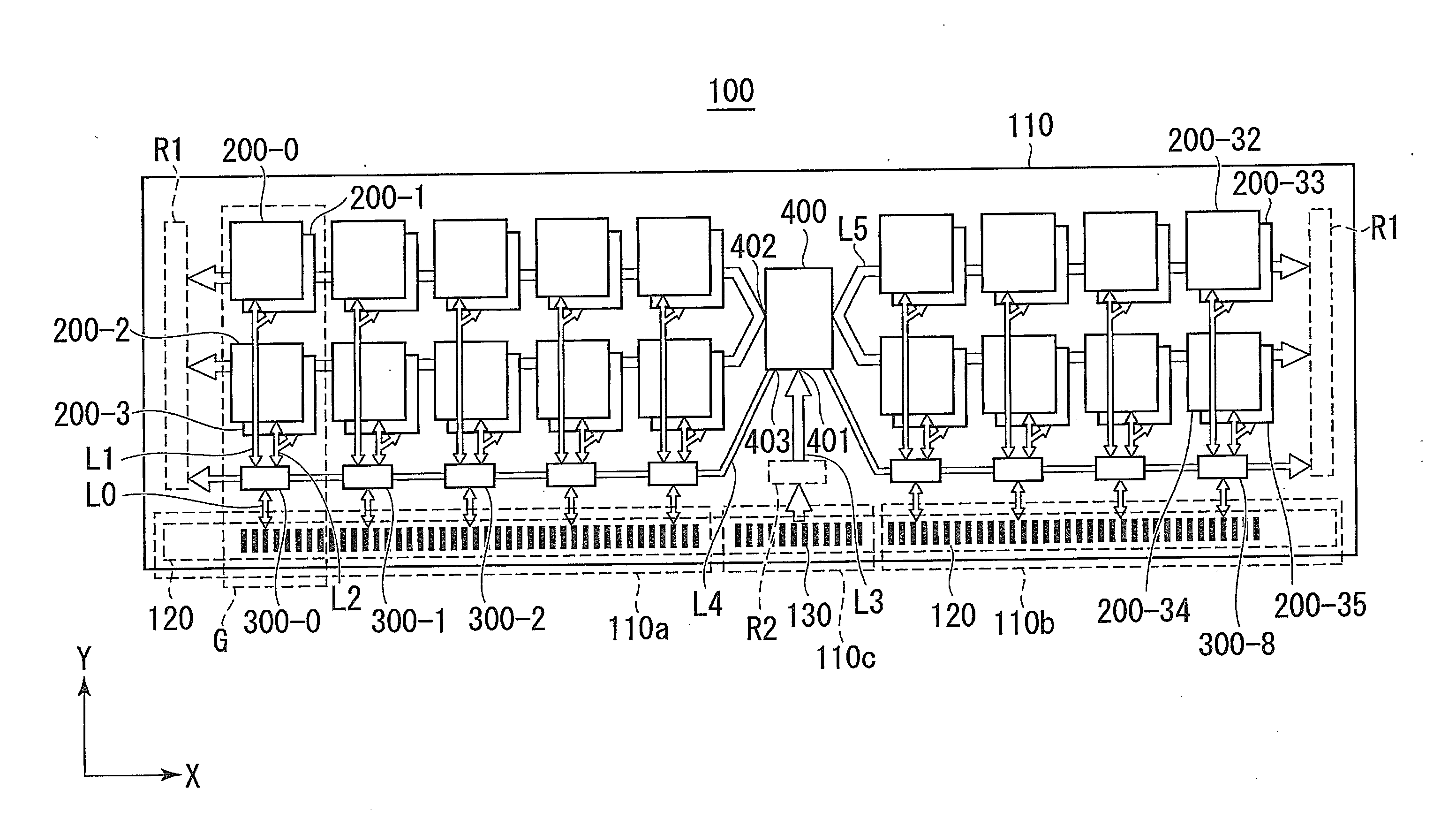

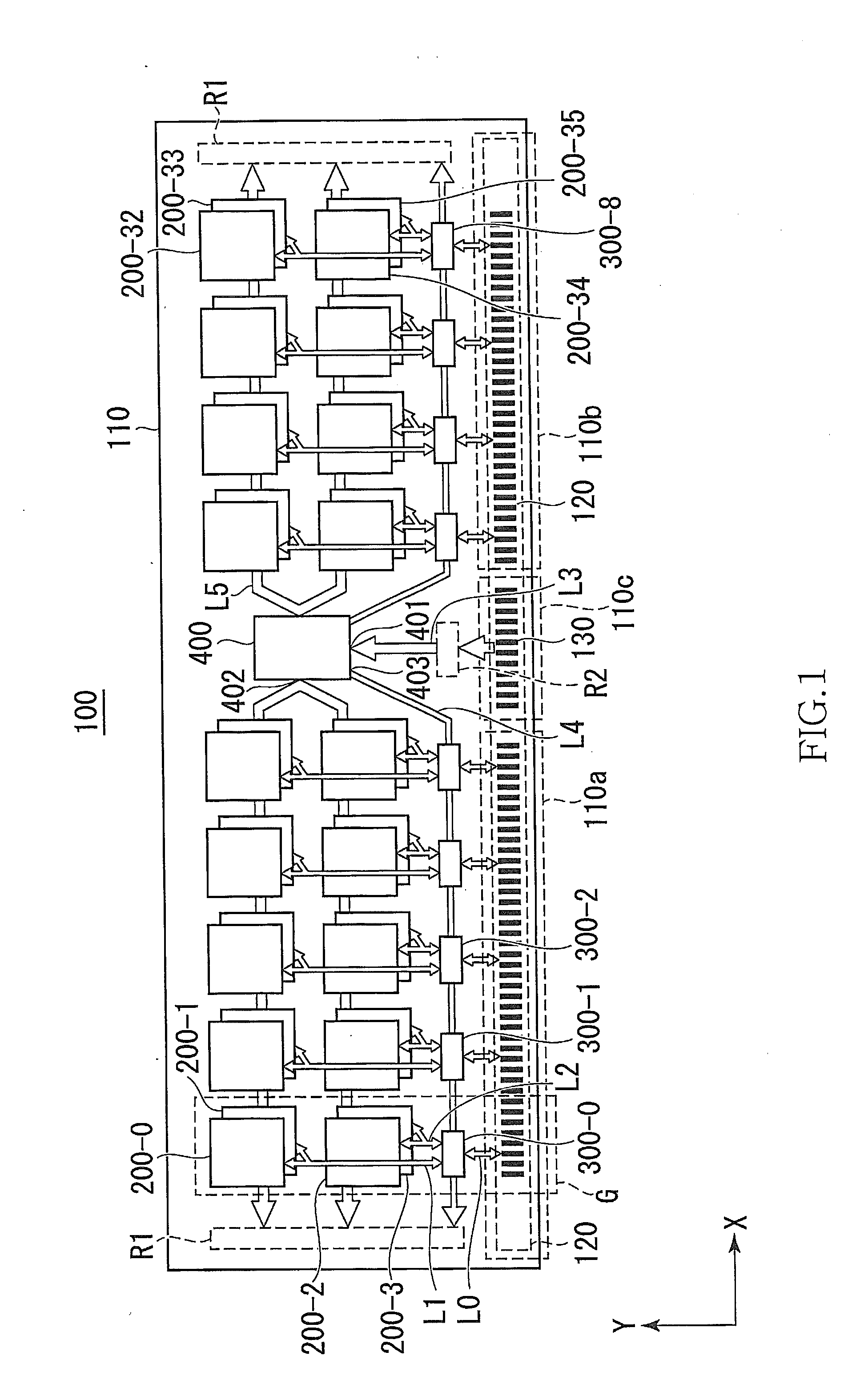

[0045]FIG. 1 is a schematic diagram of a configuration of a memory module 100 according to an embodiment of the present invention.

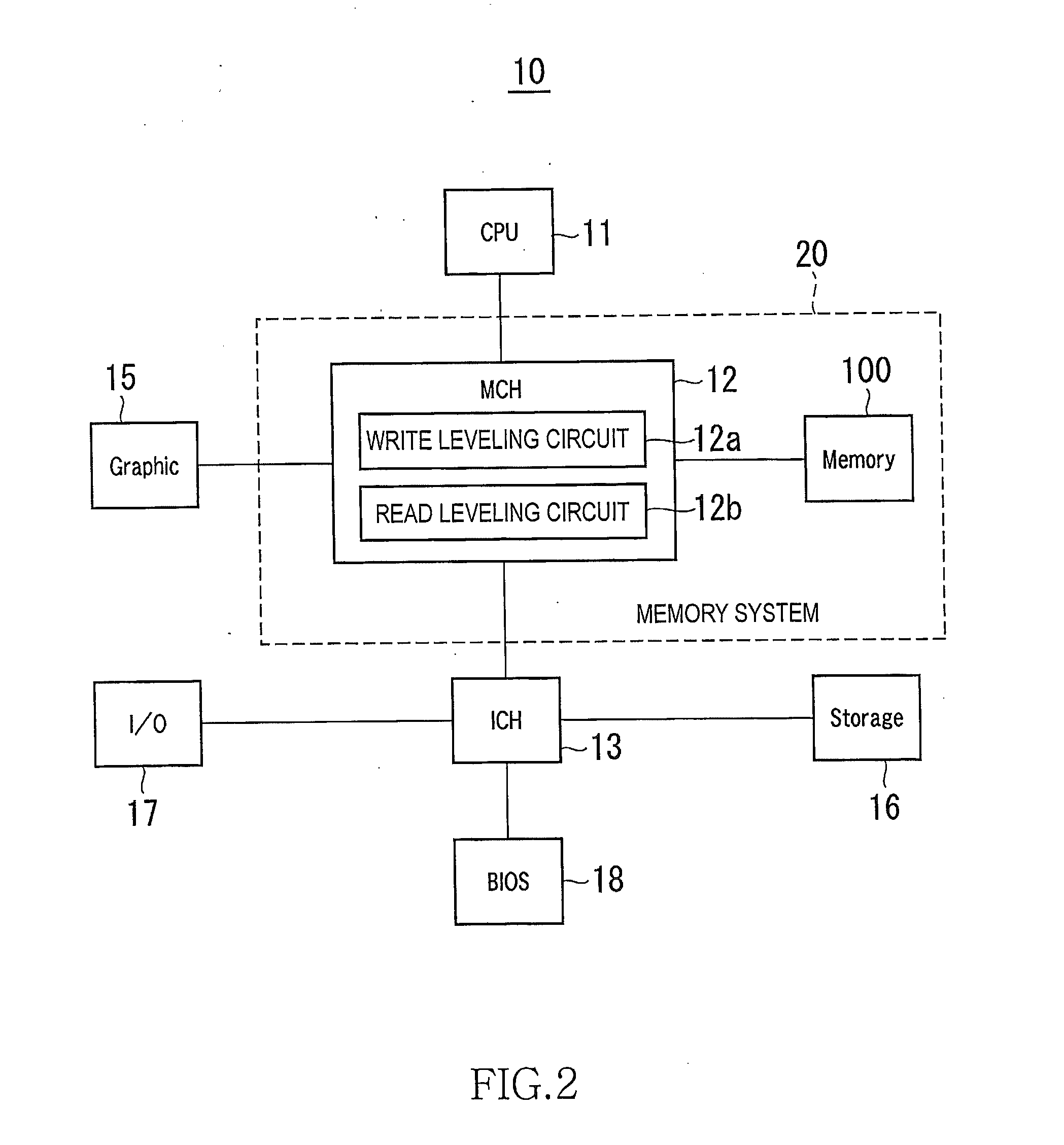

[0046]As shown in FIG. 1, the memory module 100 according to the present embodiment includes a module PCB 110, a plurality of memory chips 200 mounted on the module PCB 110, a plurality of data register buffers 300, and a command / address / control register buffer 400.

[0047]In the present embodiment, the memory module 100 includes thirty-six memory chips 200. When it is necessary to specify each of the memory chips, the memory chips are respectively represented by memory chips 200-0 to 200-35. Furthermore, in the present embodiment, the memory module 100 includes nine data register buffers 300. When it is necessary to specify each of the data register buffers, the data register buffers are respectively represented by data registe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More