Bipolar transistor, semiconductor device, and bipolar transistor manufacturing method

a manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve problems such as etching anisotropy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0023]A bipolar transistor according to a first embodiment of the present invention mainly includes a collector layer, a base layer, and an emitter layer on a substrate. In the first embodiment of the present invention, a hetero-junction bipolar transistor (hereinafter, referred to as “HBT”) in which at least one of a pair of the collector layer and the base layer and a pair of the base layer and the emitter layer has a hetero-junction connection is described as an example of the bipolar transistor.

Structure

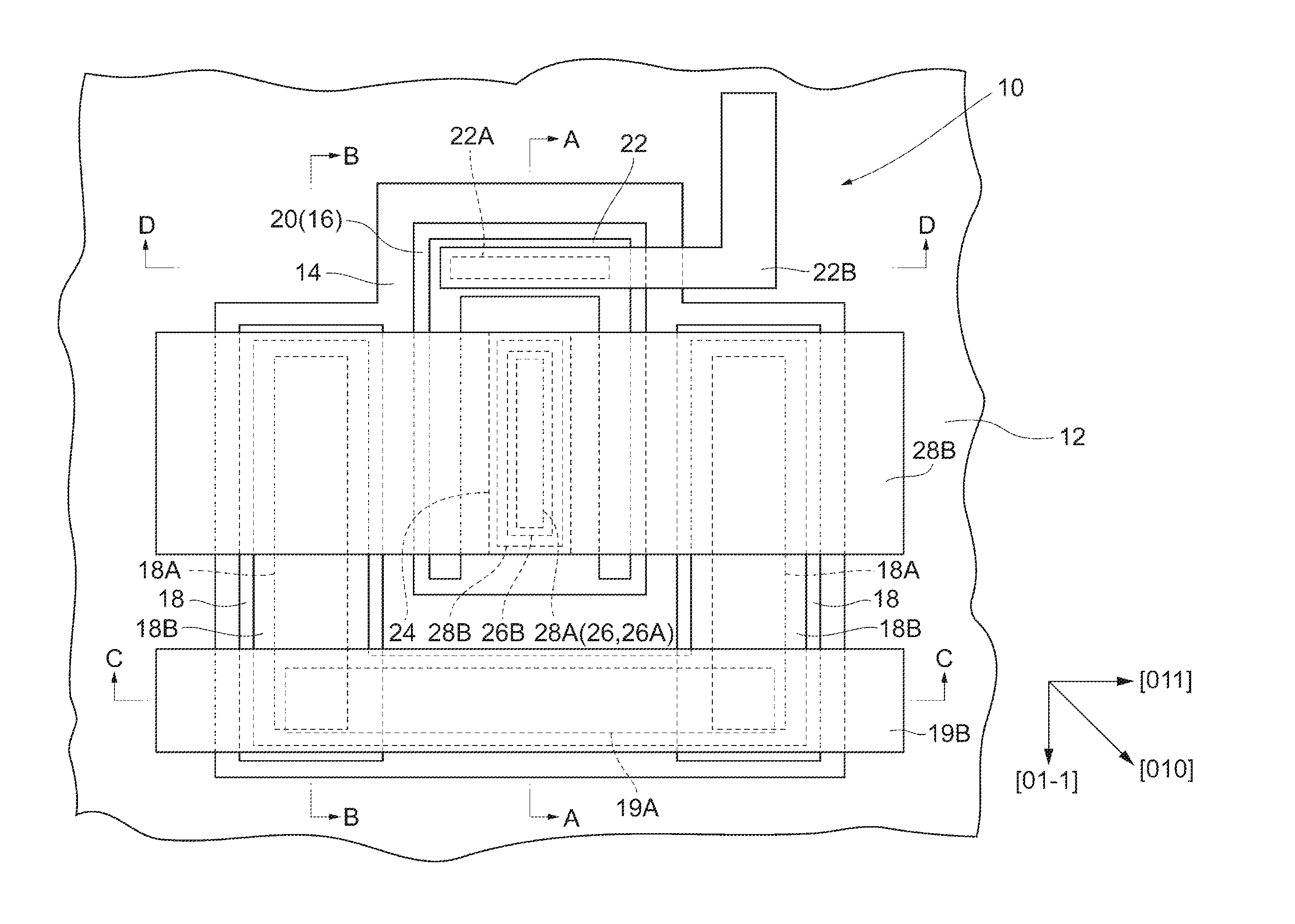

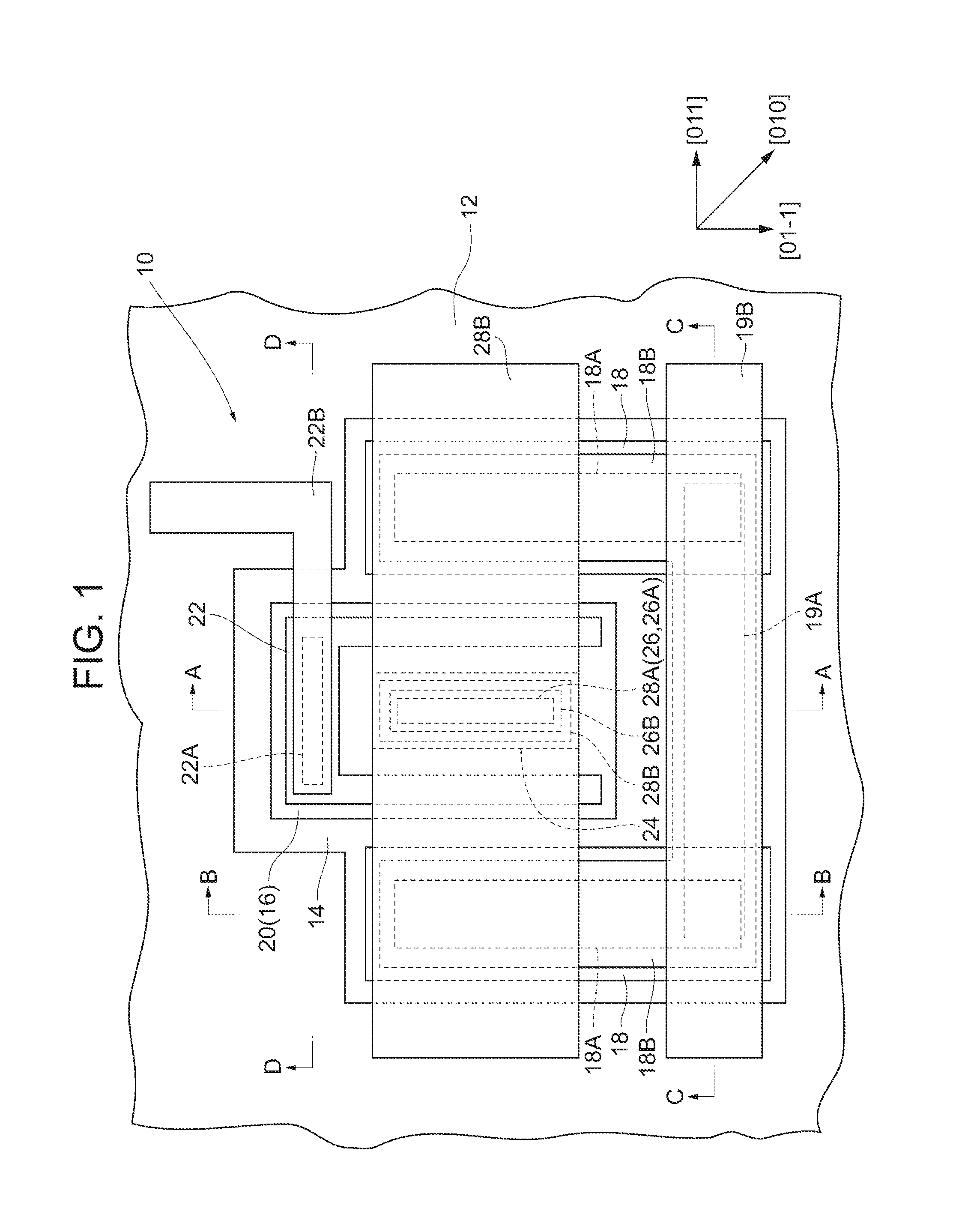

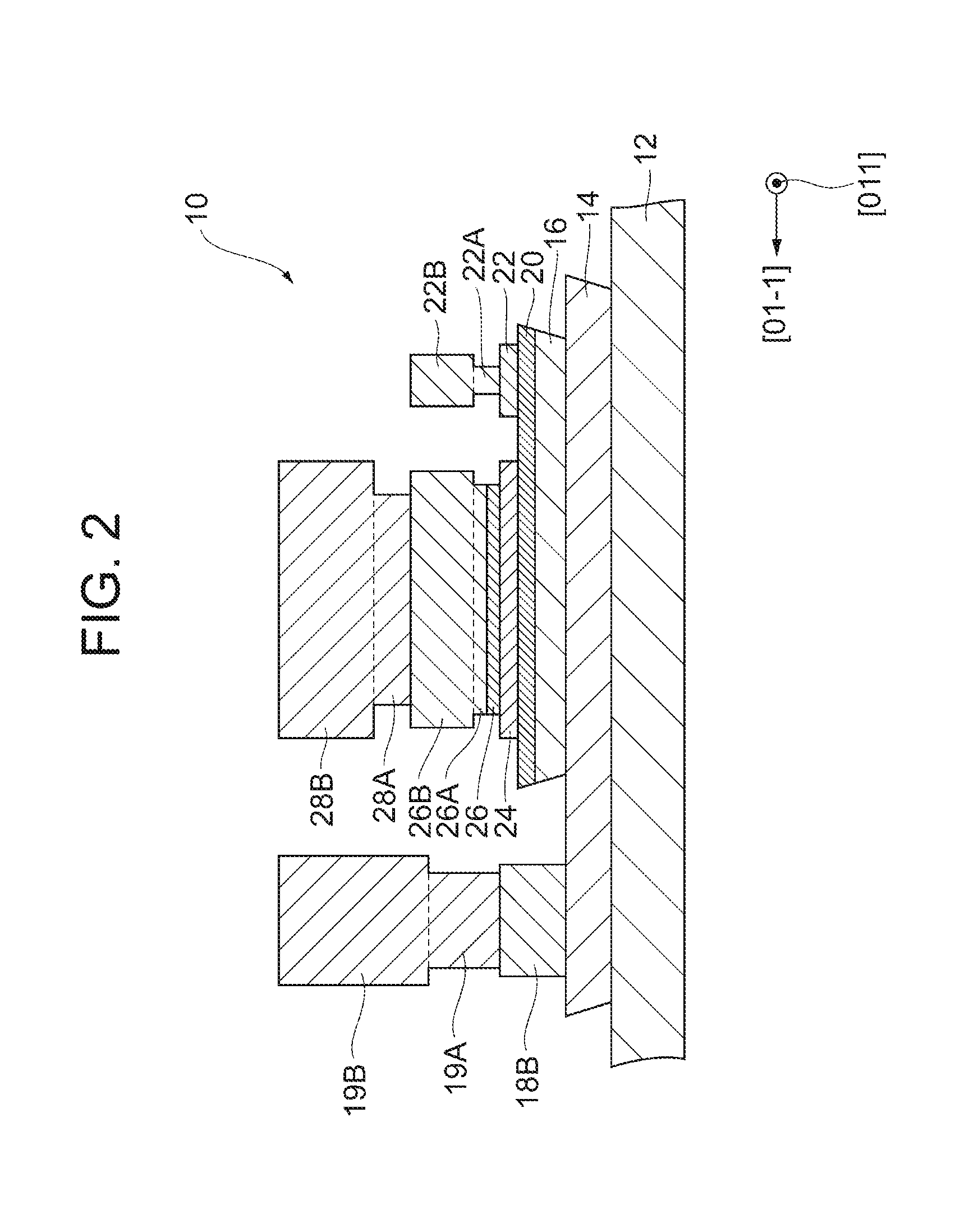

[0024]First, the structure of the HBT according to the first embodiment will be described below. FIG. 1 is a plan view of an HBT 10 as an example of the bipolar transistor according to the first embodiment of the present invention. FIG. 2 is a cross-sectional view taken along line A-A of FIG. 1. FIG. 3 is a cross-sectional view taken along line B-B of FIG. 1. FIG. 4 is a cross-sectional view taken along line C-C of FIG. 1. FIG. 5 is a cross-sectional view taken along line D-D of ...

second embodiment

[0077]An HBT according to a second embodiment of the present invention will be described below.

[0078]The HBT according to the second embodiment is different from the HBT according to the first embodiment, in a base line drawing method. The other configurations are the same as in the first embodiment.

[0079]FIG. 6 is a plan view of an HBT 40 as an example of a bipolar transistor according to the second embodiment of the present invention.

[0080]As illustrated in FIG. 6, the HBT 40 includes a base line 42 connected to a base electrode 22 via a contact hole 22A. The base line 42 is drawn out from an end in the short-side direction of the collector layer. As a result, the base line 42 goes over the side surfaces which are the forward mesa surfaces of the base layer 20, the collector layer 16, and the sub collector layer 14. More specifically, the base line 42 includes a first portion 42A, a second portion 42B, and a third portion 42C.

[0081]The first portion 42A is a portion that is presen...

third embodiment

[0085]A semiconductor device according to a third embodiment of the present invention will be described below.

[0086]FIG. 7 is a plan view of a semiconductor device 50 according to the third embodiment of the present invention.

[0087]The semiconductor device 50 according to the third embodiment includes at least one HBT 10 which has been described in the first embodiment and at least one HBT 60 different from the HBT 10 in the base line drawing method.

[0088]The HBT 60 includes a sub collector layer 62, a collector layer 64, a collector electrode 66, a base layer 68, a base electrode 70, an emitter layer 72, and an emitter electrode 74. The HBT 60 further includes a collector line 76, an emitter line 78, and a base line 80.

[0089]The collector layer 64 and the base layer 68 contain, for example, GaAs as a major component. The collector layer 64 and the base layer 68 have, for example, a rectangular shape. In the collector layer 64 and the base layer 68, the long-side direction thereof e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More