Three-dimensional stacked phase change memory and preparation method thereof

a phase change memory and three-dimensional technology, applied in the field of microelectronic devices and memories, can solve the problems of limited memory cell feature size, low reliability, photoetching process, etc., and achieve the effect of reducing the number of photoetching operations, increasing the cost of the photoetching process, and reducing the number of times of photoetching operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

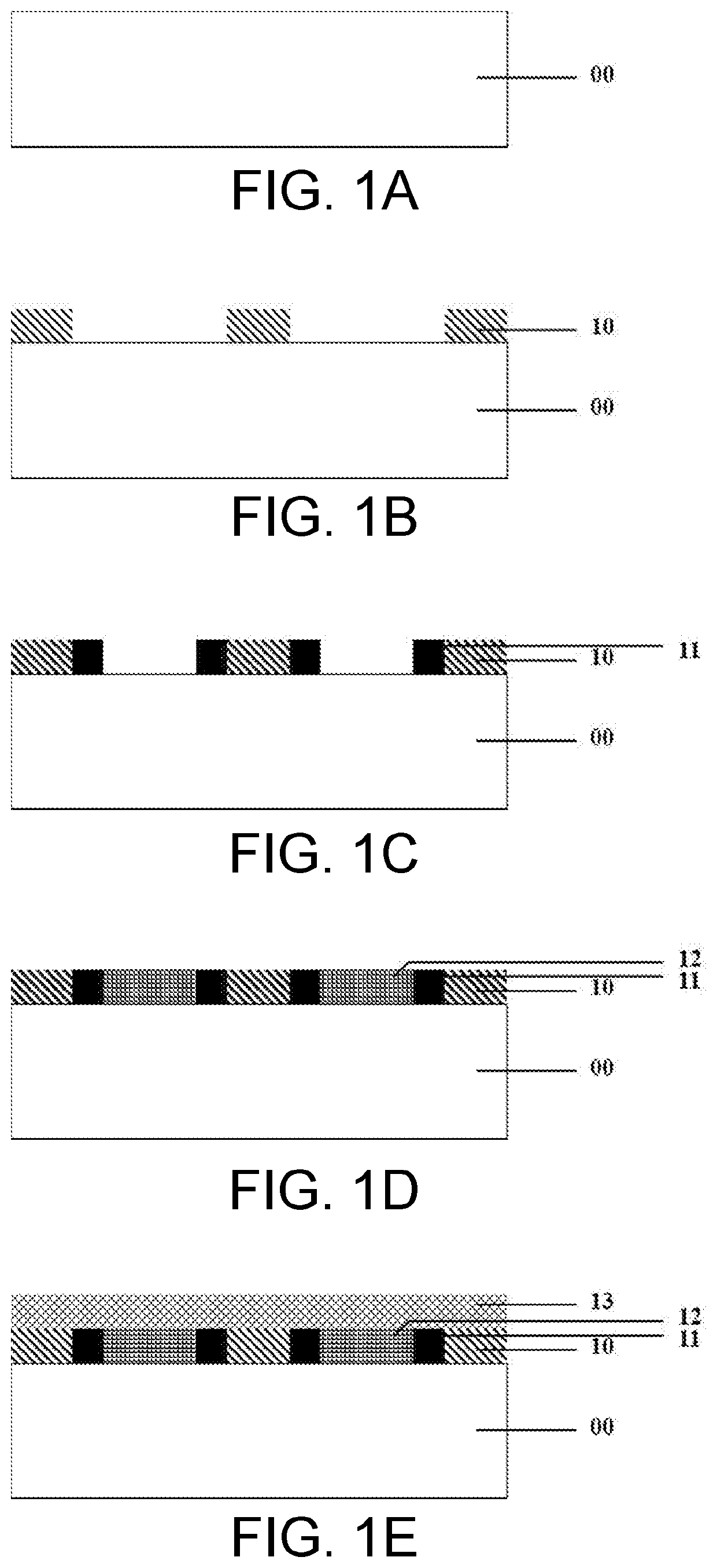

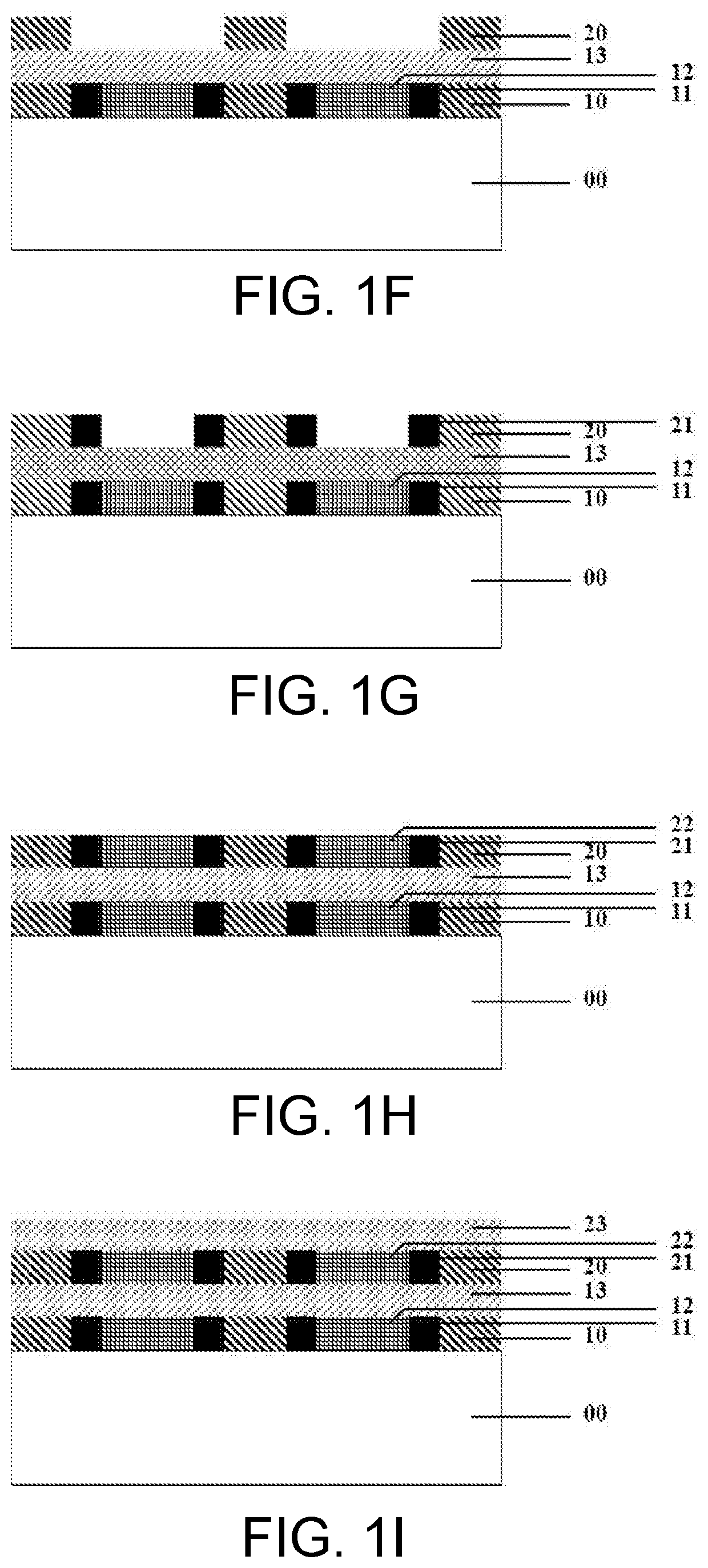

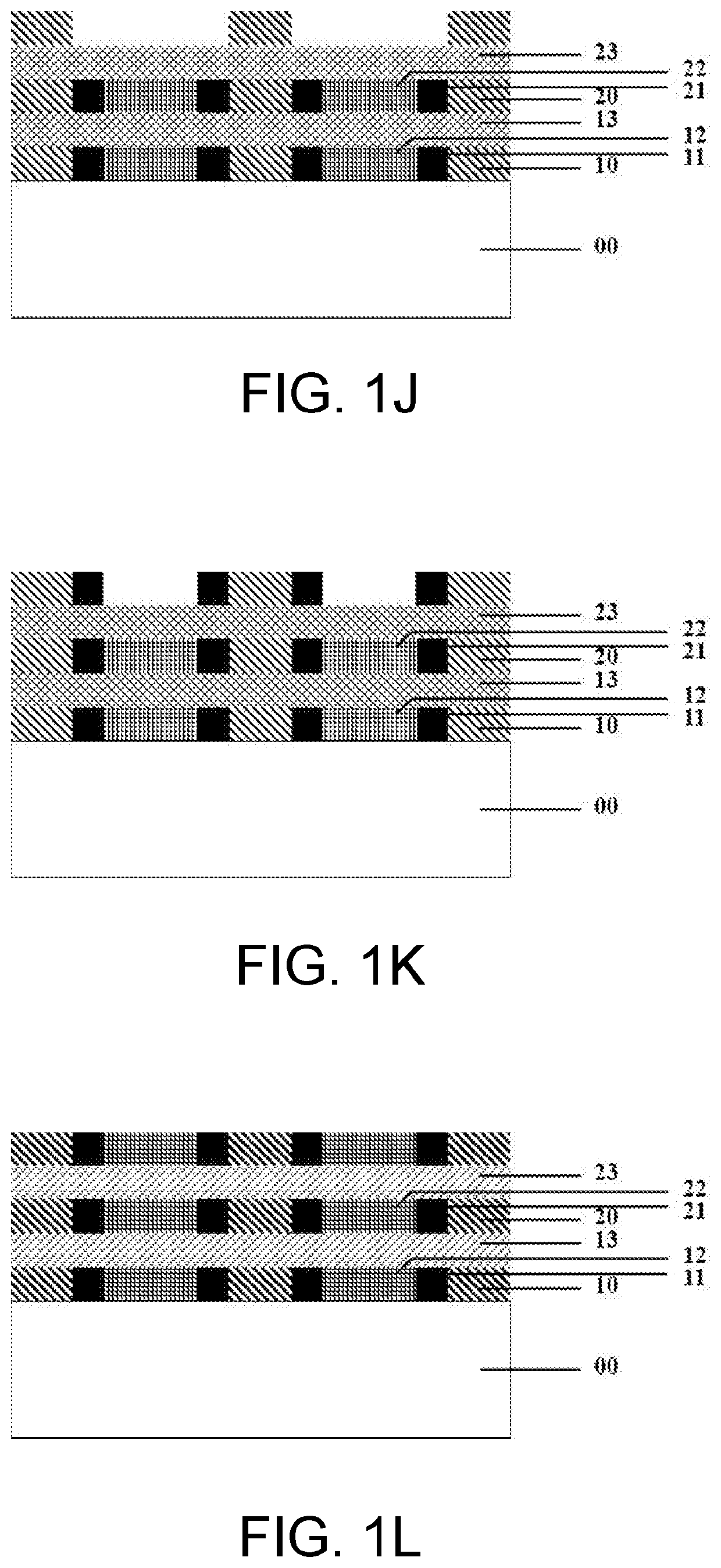

[0071]In this embodiment, a three-dimensional stacked phase change memory and a preparation method thereof are provided by taking a multilayer stacked memory as an example, and the method specifically includes the following steps.

[0072]Step 1: performing a photoetching process on a single crystal silicon substrate 00 to obtain a plurality of first horizontal electrode patterns having a line width of 10 μm and an interval of 15 μm in a certain direction, depositing a 100 nm TiW alloy electrode material on the photoetched substrate, and then performing a lift-off process to obtain first horizontal electrodes 10 corresponding to the photoetching patterns, as shown in FIG. 1A to FIG. 1B and FIG. 2A to FIG. 2B.

[0073]Step 2: on the basis of the step 1, performing a photoetching process to obtain first strip-shaped phase change layer patterns having a line width of 17 μm, a central gap of 10 μm and an interval of 8 μm, in which the patterns cover the intervals of the first horizontal elect...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More