Methods and apparatus for dynamic instruction controlled reconfigurable register file with extended precision

a dynamic instruction and register file technology, applied in the field of processing improvement, to achieve the effect of reducing the size of the register file, reducing the number of read and write ports, and improving the performance of the implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

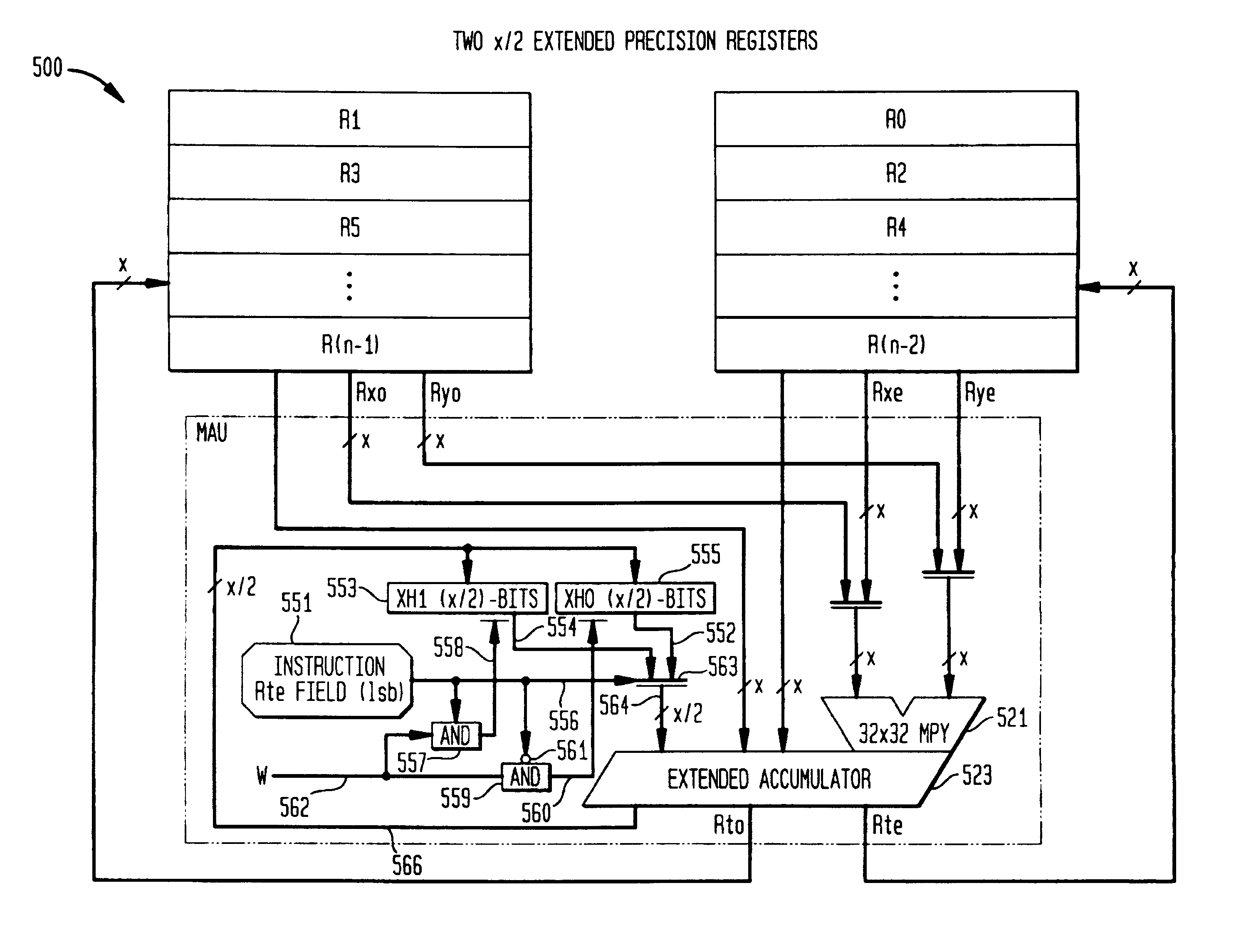

Embodiment Construction

[0016]Further details of a presently preferred ManArray architecture are found in U.S. patent application Ser. No. 08 / 885,310 now U.S. Pat. No. 6,023,753 and Ser. No. 08 / 949,122 now U.S. Pat. No. 6,167,502 filed Jun. 30, 1997 and Oct. 10, 1997, respectively, Provisional Application Ser. No. 60 / 064,619 entitled Methods and Apparatus for Efficient Synchronous MIMD VLIW Communication” filed Nov. 7, 1997, Provisional Application Ser. No. 60 / 067,511 entitled “Method and Apparatus for Dynamically Modifying Instructions in a Very Long Instruction Word Processor” filed Dec. 4, 1997, Provisional Application Ser. No. 60 / 068,021 entitled “Methods and Apparatus for Scalable Instruction Set Architecture” filed Dec. 18, 1997, Provisional Application Ser. No. 60 / 071,248 entitled “Methods and Apparatus to Dynamically Expand the Instruction Pipeline of a Very Long Instruction Word Processor” filed Jan. 12, 1998, Provisional Application Ser. No. 60 / 072,915 entitled “Methods and Apparatus to Support C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More