Dynamic memory and its manufacturing method

A dynamic storage and storage unit technology, applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., to reduce aberrations, solve line shortening effects, and reduce proximity effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

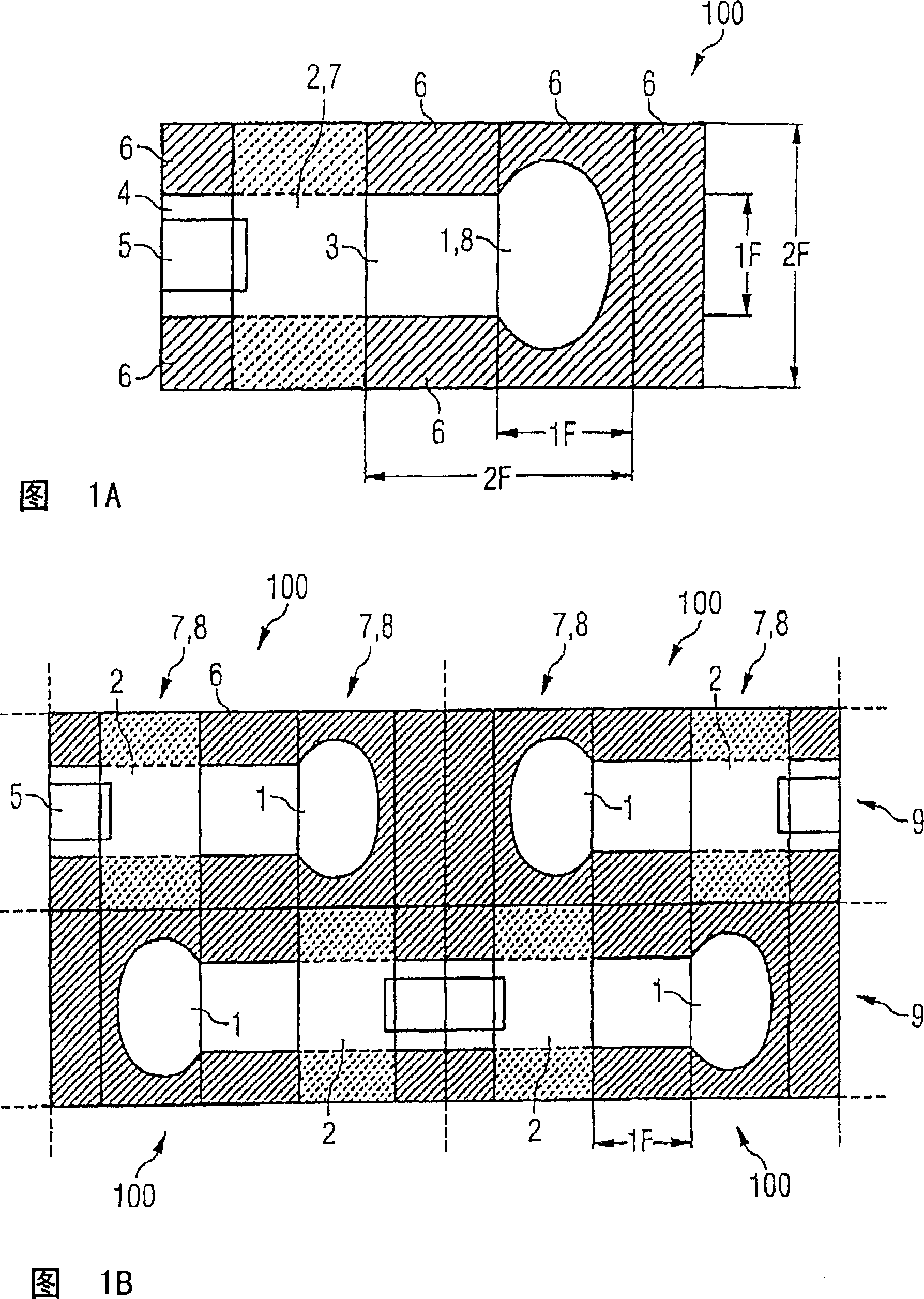

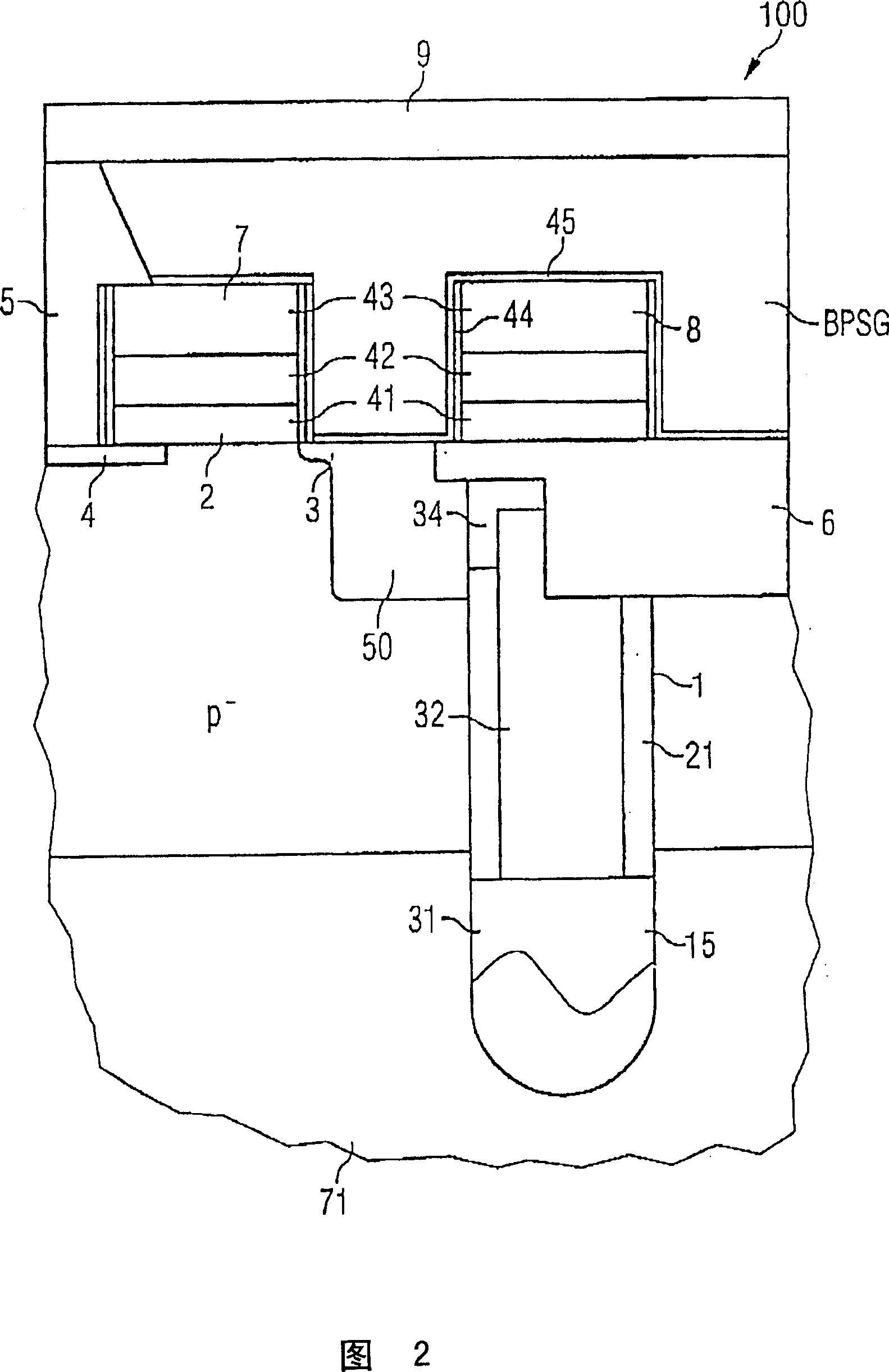

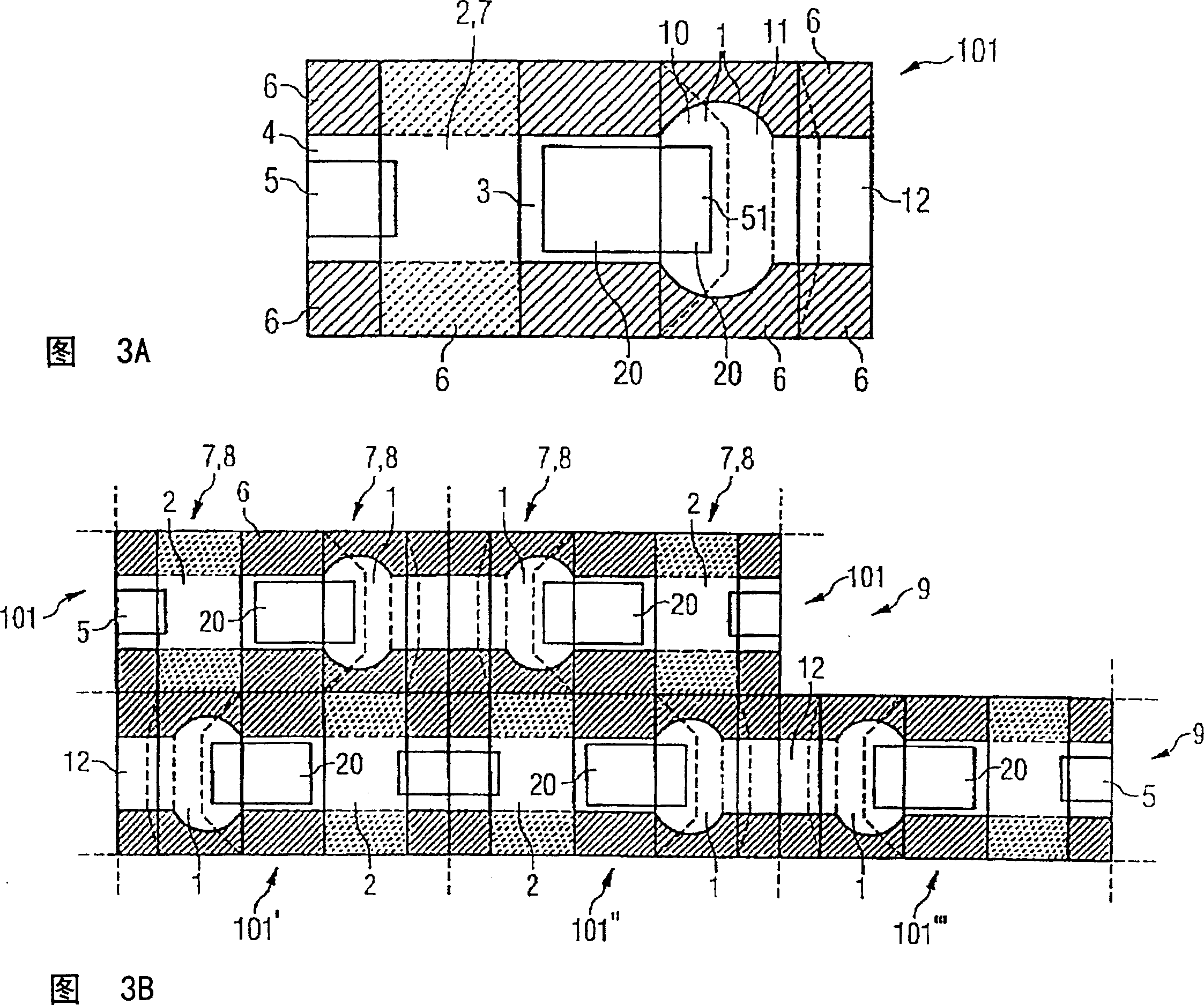

[0055] hereby utilize and an 8F 2 A comparison of conventional DRAM memory cells (100) in the MINT cell configuration of the cell area to illustrate the features of the present invention. Accompanying drawing 1 shows a kind of with prior art making with 8F in a schematic way 2 A top view of a DRAM memory cell (100) configured with a MINT cell with a cell area of . Trench capacitor (1) is located in the right area of the cell surface shown in Fig. 1 . The trench capacitor (1) is located under a passive word line (8). The trench capacitor (1) is connected to a source region (3). A gate contact (2) disposed under an active word line (7) is located on one side of the source region (3). The selection transistor also has a drain region (4) on which a bitline contact (5) from above forms an electrically conductive connection with the drain region (4) on the drawing plane. A shallow insulating trench (6) separates the active area of the cell of FIG. 1 from the active area o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com