Micron level chip packing structure

A chip packaging structure, micron-level technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems that affect the performance of the chip, the solder balls are easy to deviate from the solder pads, and the bonding force of the ball-planted joints is reduced.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

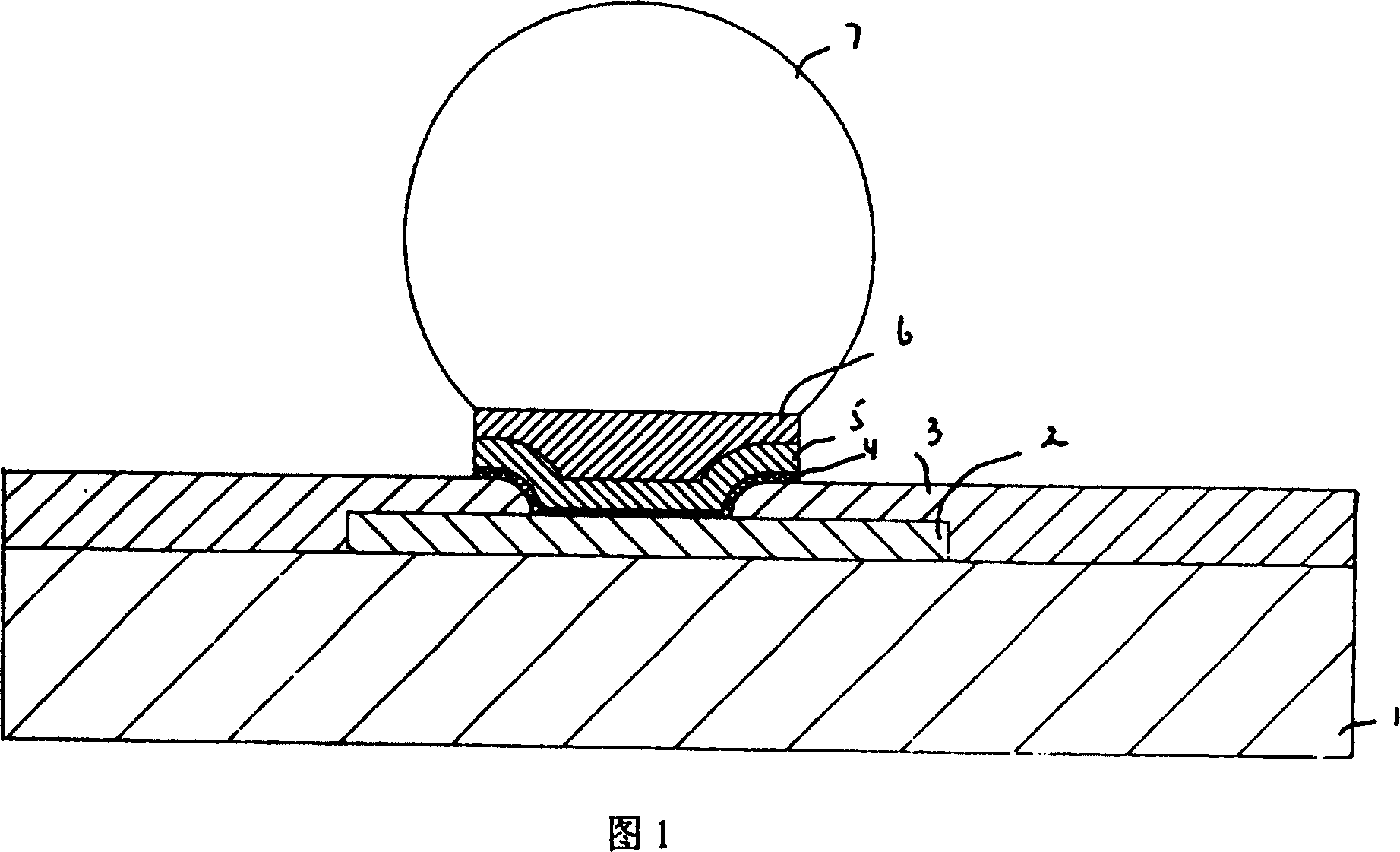

[0014] Referring to Fig. 1, the present invention is a kind of micron-scale chip package structure, and it is to be provided with a welding pad 2 on one surface of chip body 1, and protective layer 3 is set on the outer periphery of welding pad 2 and chip body 1 surface outside outer periphery, and welding pad 2 The protective layer 3 on the surface and its outer periphery is successively superimposed on the titanium layer 4, the copper layer 5 and the copper pillar 6, and the top of the copper pillar 6 is planted with tin balls 7, and all the solder balls are placed on the top of the copper pillar.

[0015] The thickness of the copper pillar 6 should be determined according to the reliability requirements of the chip, and is generally controlled within 5 μm˜100 μm.

Embodiment 2

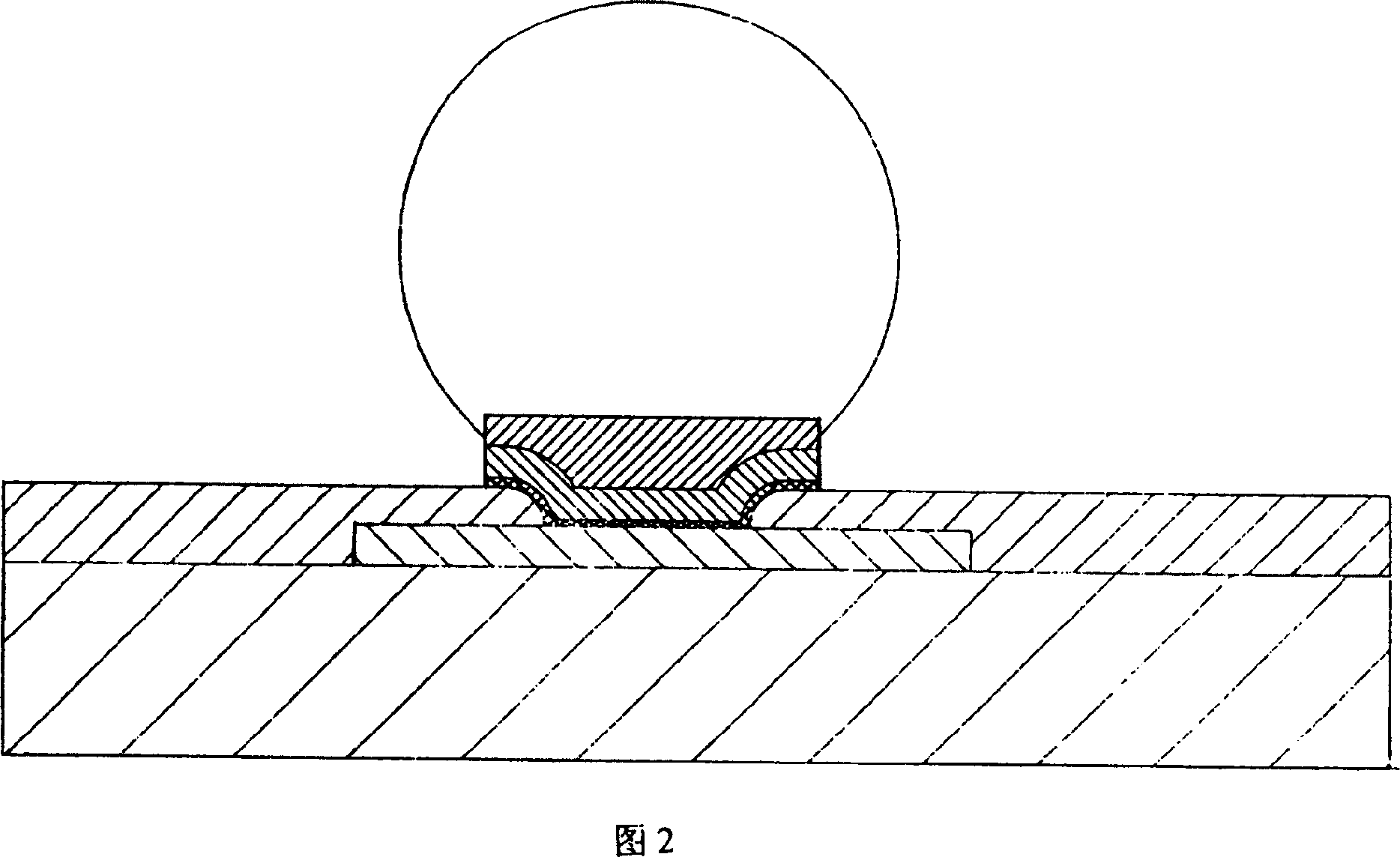

[0017] Referring to FIG. 2 , the difference between this embodiment and the first embodiment is that the solder balls 7 partially cover the copper pillars 6 .

Embodiment 3

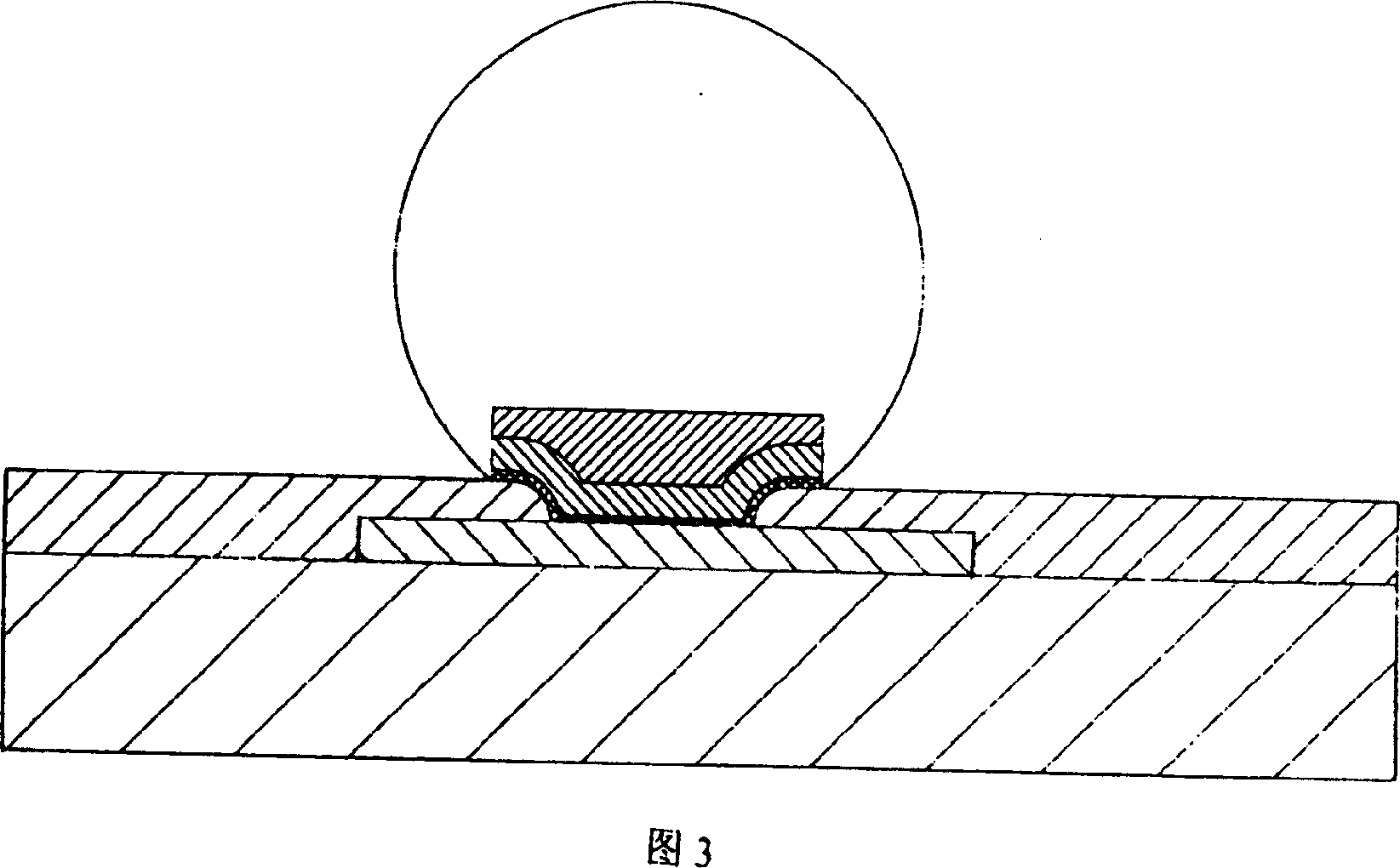

[0019] Referring to FIG. 3 , the difference between this embodiment and the first embodiment is that the solder balls 7 completely cover the copper pillars 6 , the copper layer 5 and the titanium layer 4 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More