Method for mfg. selective local self-aligned silicide

A technology of self-aligned silicide and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve problems such as misalignment, process margin reduction, and difficulties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] 2A to 2F are cross-sectional views of the fabrication process of selective local salicide according to an embodiment of the present invention.

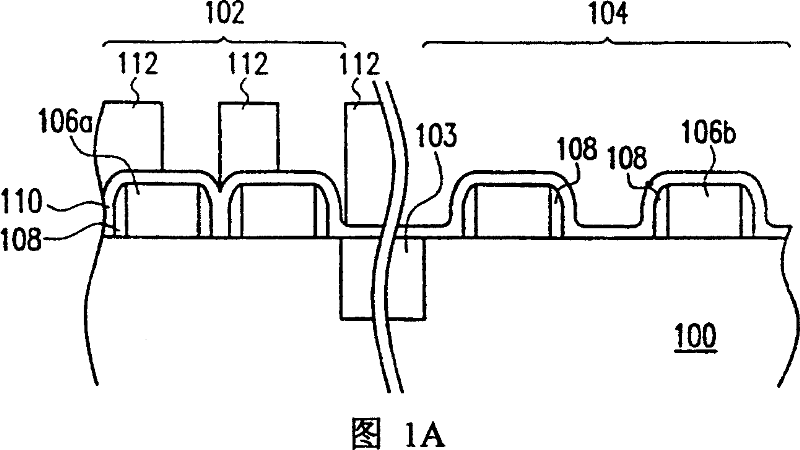

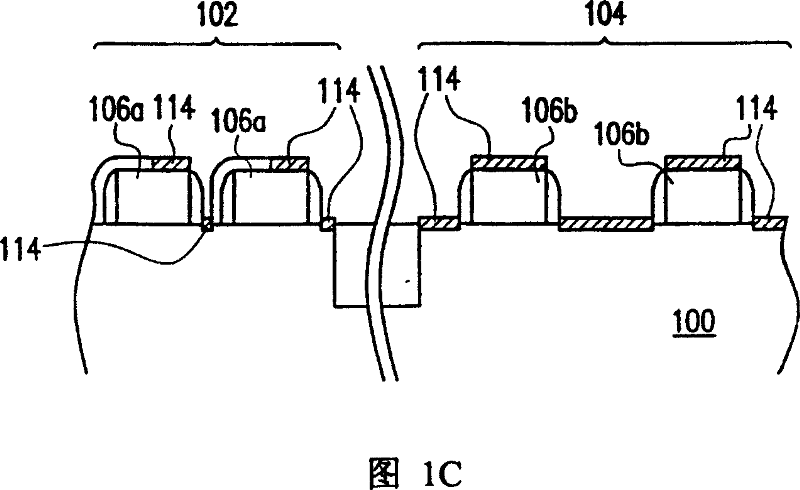

[0030] Referring to FIG. 2A , firstly, a substrate 200 divided into a memory cell area 202 and a logic circuit area 204 by an isolation area 203 is provided. Then, a plurality of gates 206 a, 260 b are formed on the substrate 200 , and the gap between the gates 206 a of the memory cell region 202 is narrower than that of the gates 206 b of the logic circuit region 204 . In addition, a spacer 208 is formed on the sidewalls of the gates 206a and 206b.

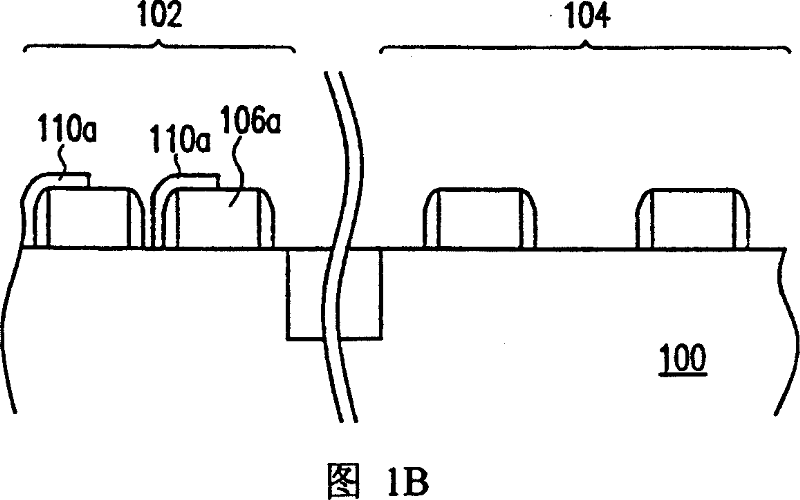

[0031] Next, referring to FIG. 2B , a conformal first barrier layer 210 is formed on the substrate 200, such as a photoresist protection oxide layer (Resist Protect Oxide, PRO for short), and its material is such as silicon oxide to cover the memory cell area. 202 and logic circuit area 204 . The first barrier layer 210 on the memory cell area 202 can reduce the width of the gap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More