Method for removing lattice defect in pad area of semiconductor device

A technology of lattice defects and pad areas, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, etc., can solve the reliability impact of DRAM, not particularly reliable, lattice defects in pad areas And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

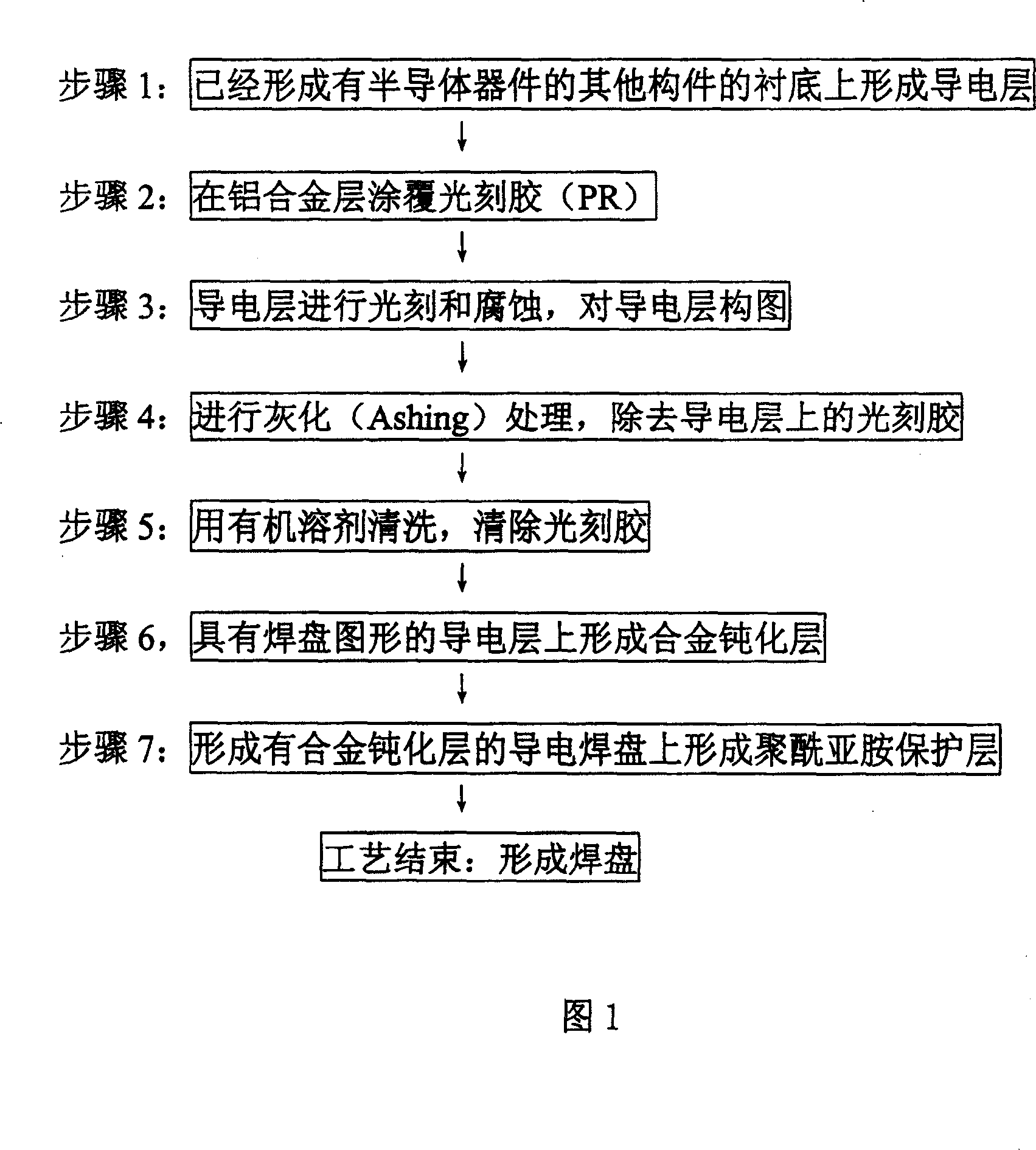

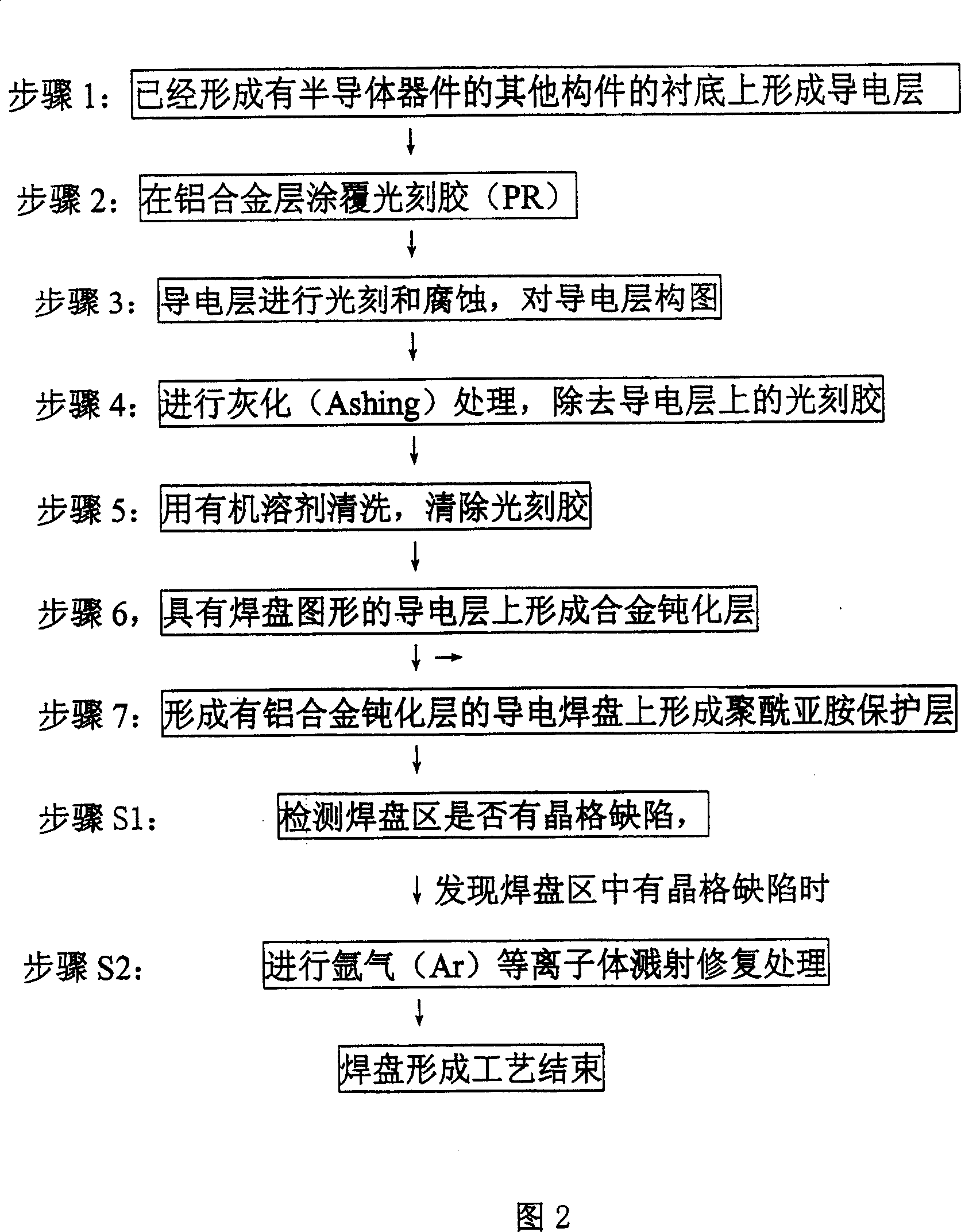

[0014] A method for removing lattice defects in a pad (PAD) region of a semiconductor device according to the present invention will be described in detail below with reference to FIG. 2 . Fig. 2 is a flowchart of a pad forming process of a semiconductor device according to the present invention.

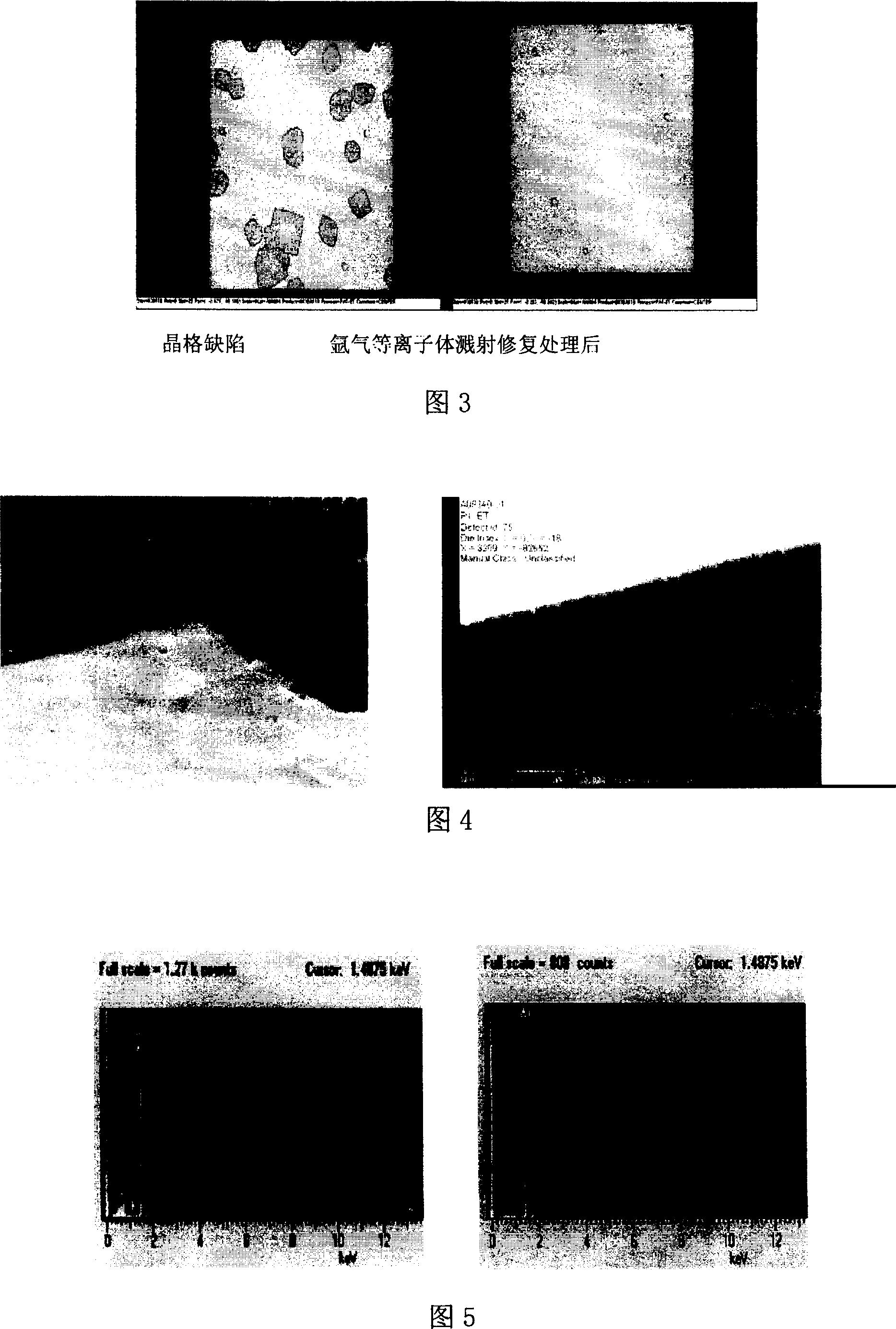

[0015] The pad formation process flow of the semiconductor device according to the present invention shown in Fig. 2 is to increase after the step 7 (forming the polyimide protective layer) of the pad formation process flow of the existing semiconductor device shown in Fig. 1 : Step S1, detecting whether there is a lattice defect in the pad area; and Step S2, performing argon (Ar) plasma sputtering repair treatment when step S1 detects that there is a lattice defect in the pad area. In step S1, use an optical microscope (OM) to detect whether there is a lattice defect in the pad area. When it is found that there is a lattice defect in the pad area, take a microscopic photo of the pa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com