Patents

Literature

38results about How to "Eliminate lattice defects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

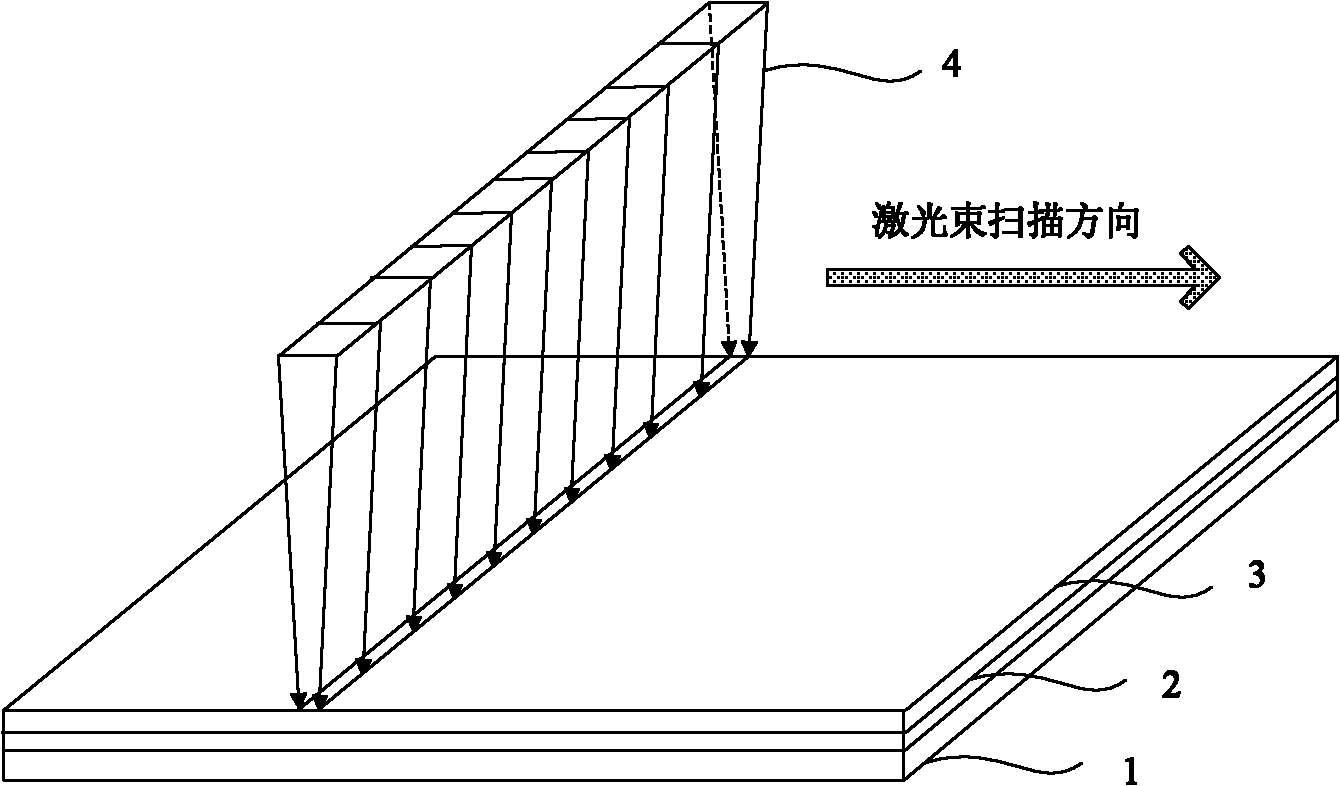

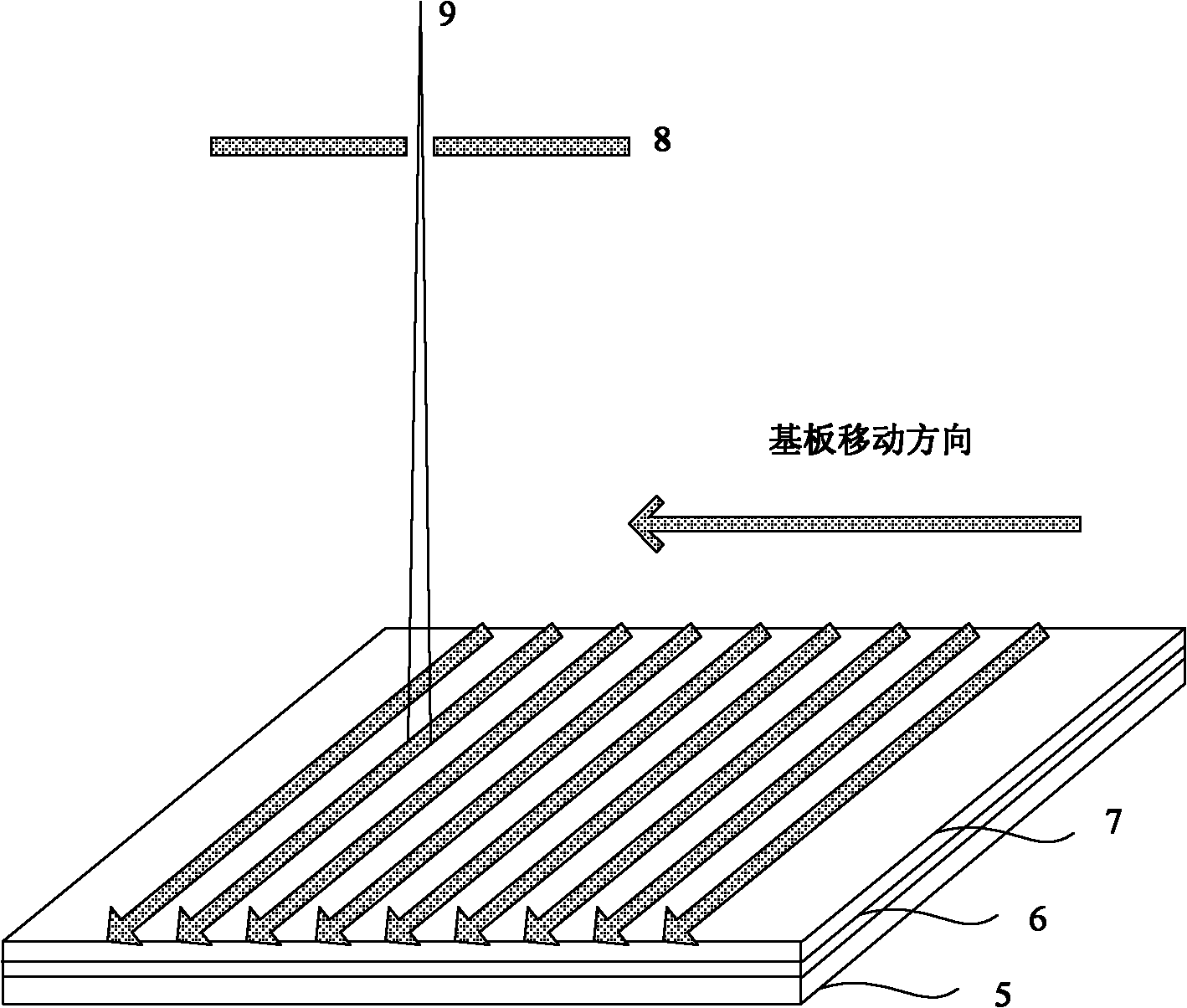

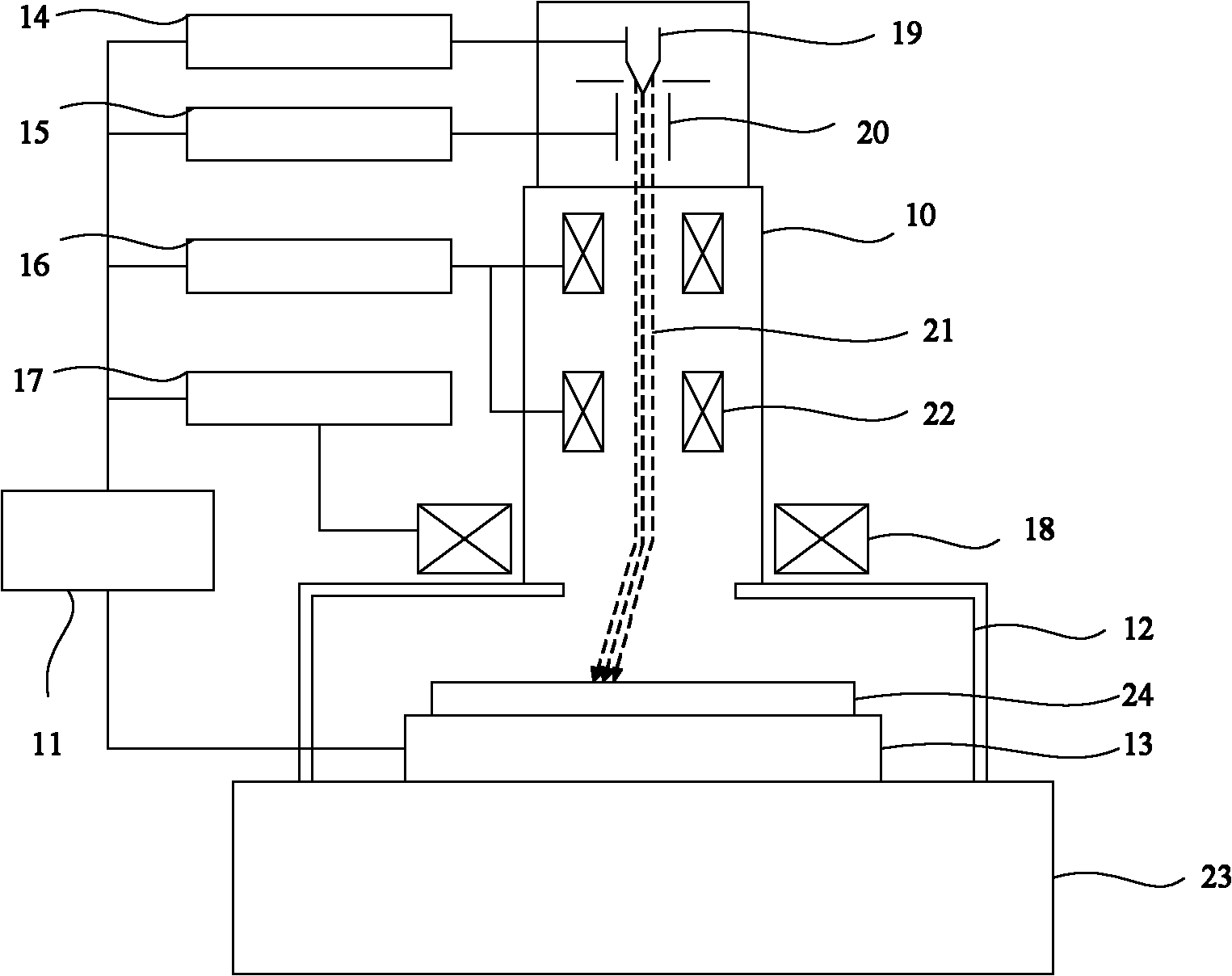

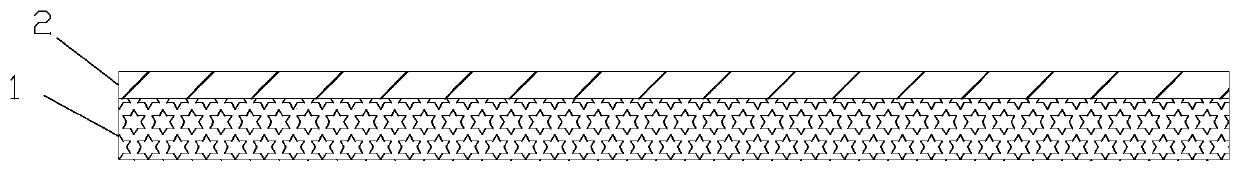

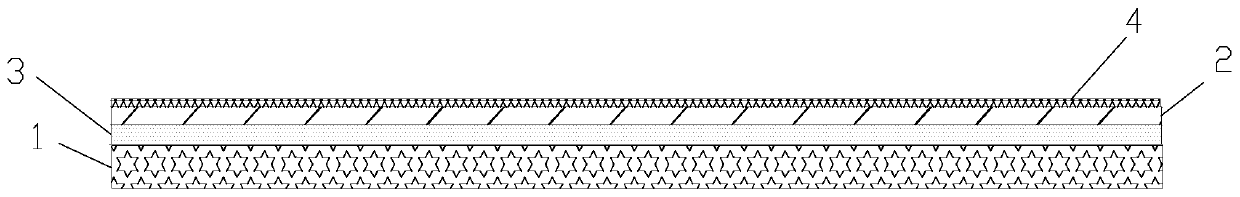

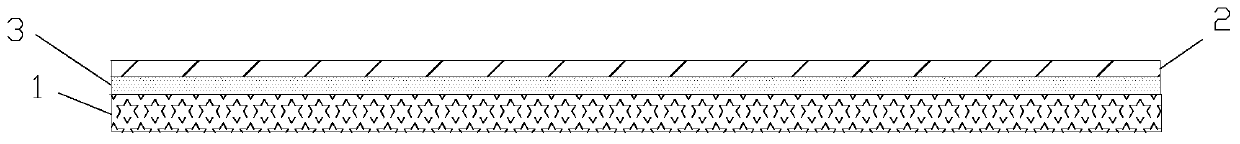

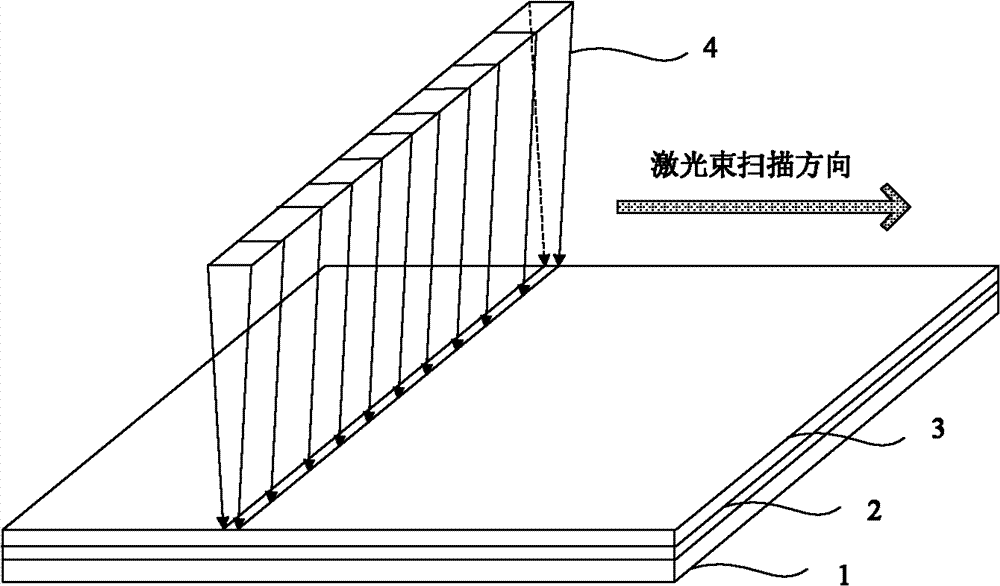

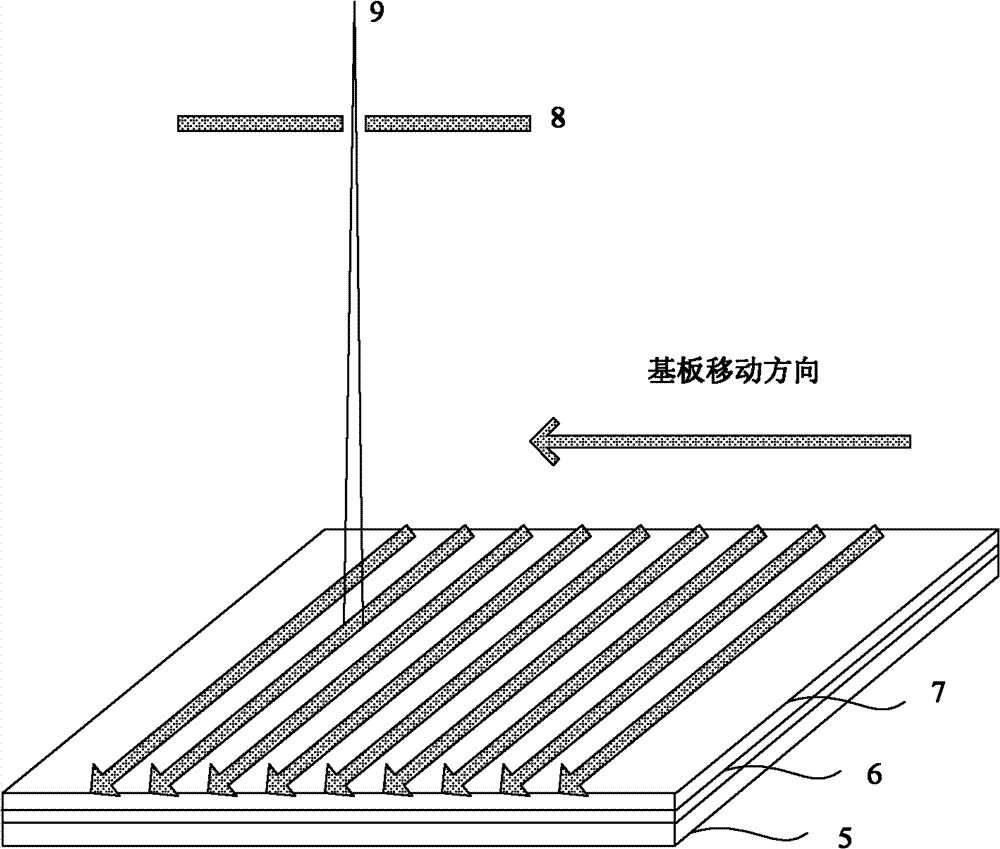

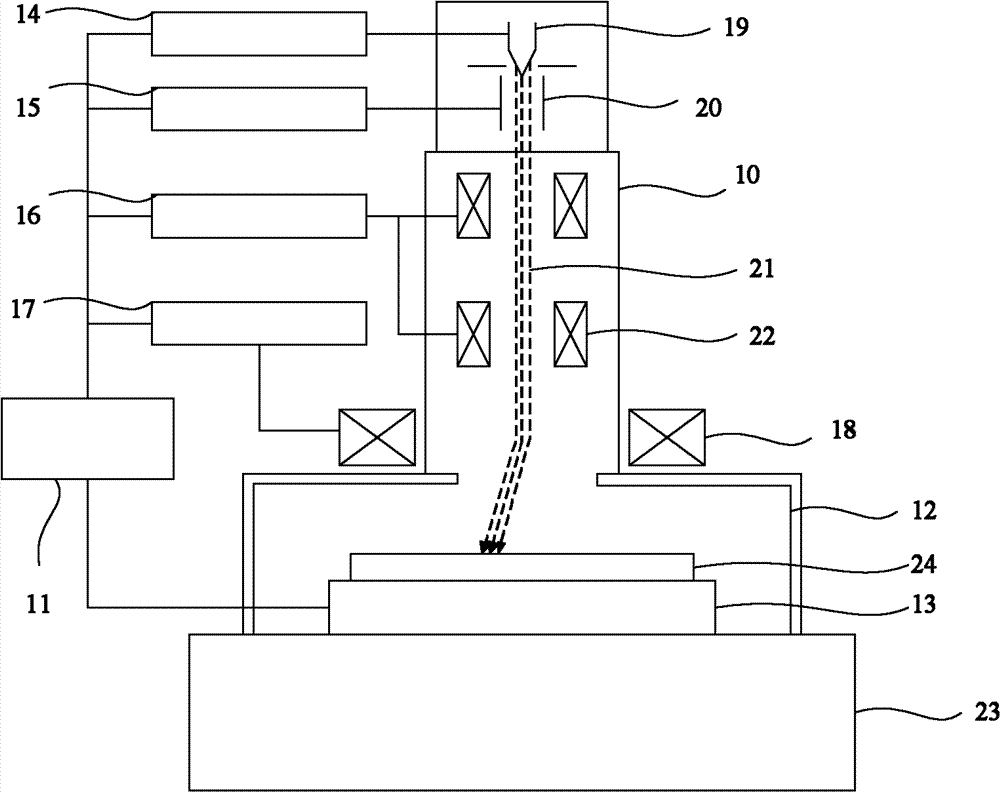

Crystallization of amorphous silicon film as well as manufacture method and device of poly-silicon film

ActiveCN101894747AEliminate lattice defectsReduce use costSemiconductor/solid-state device manufacturingControl electronicsAnode voltage

Owner:SHENZHEN DANBANG INVESTMENT GROUP

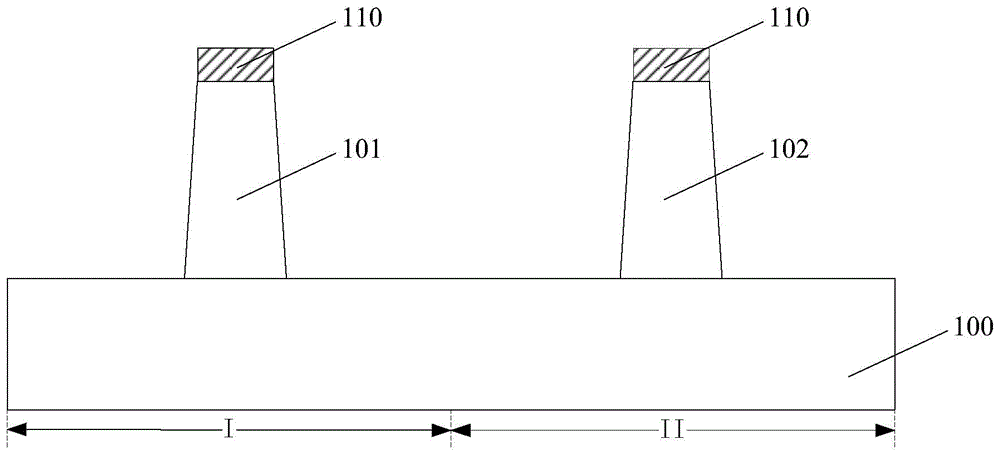

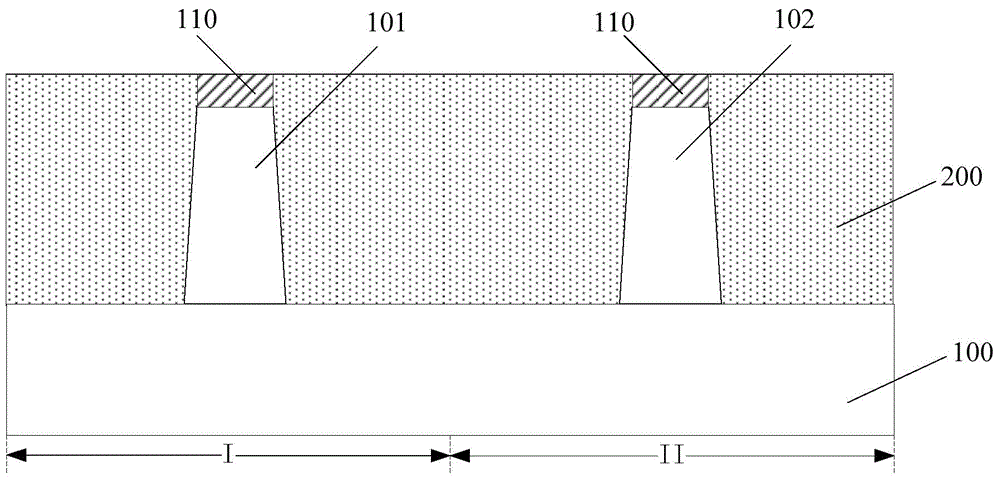

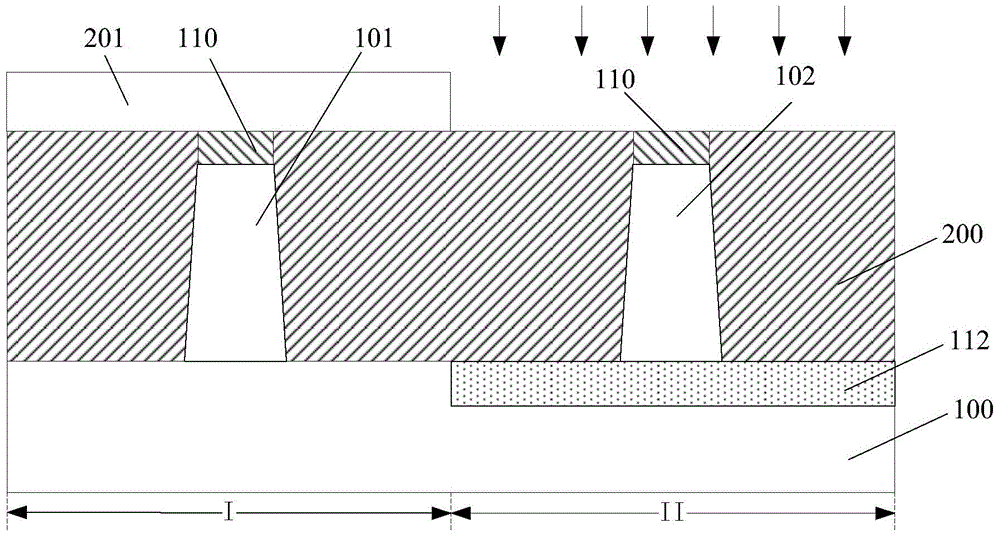

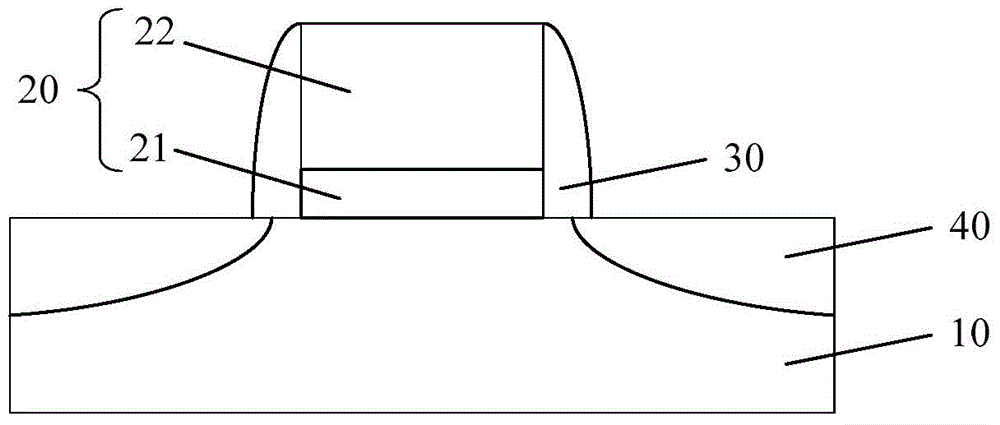

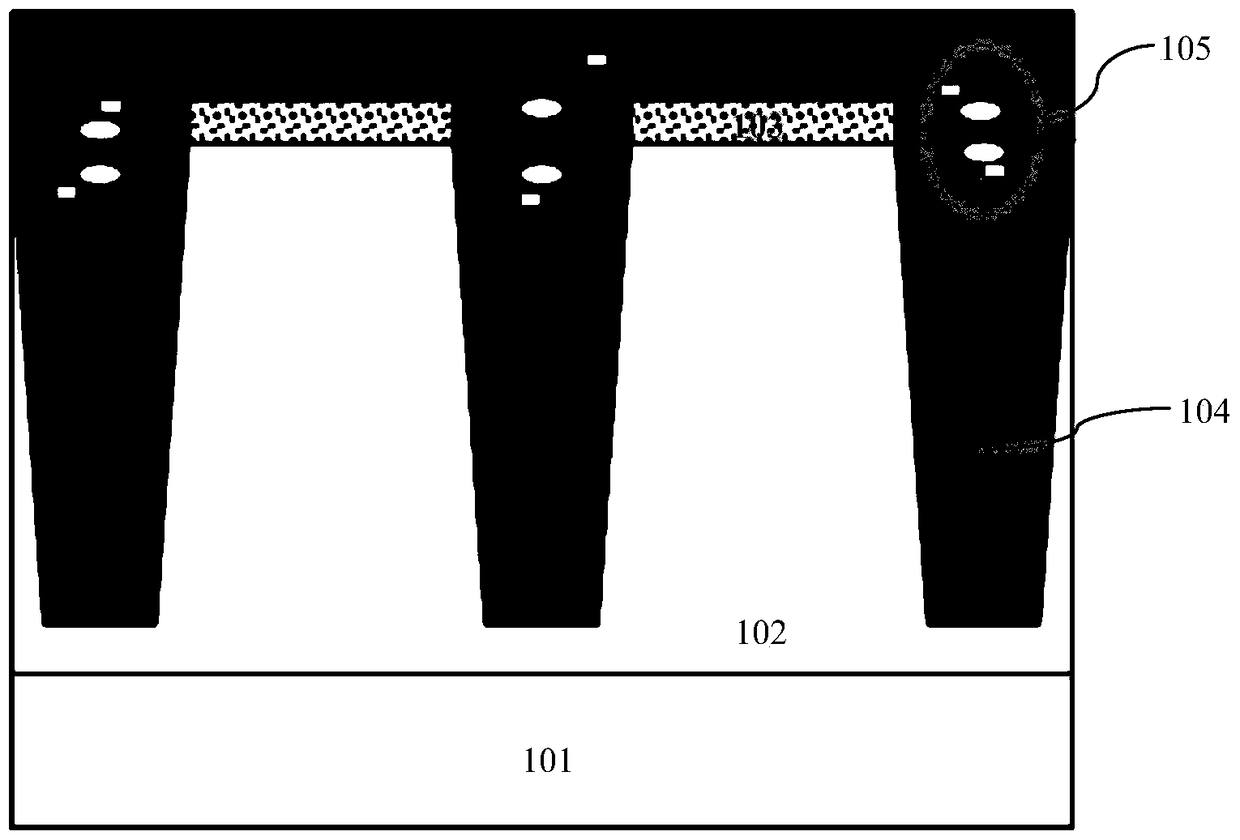

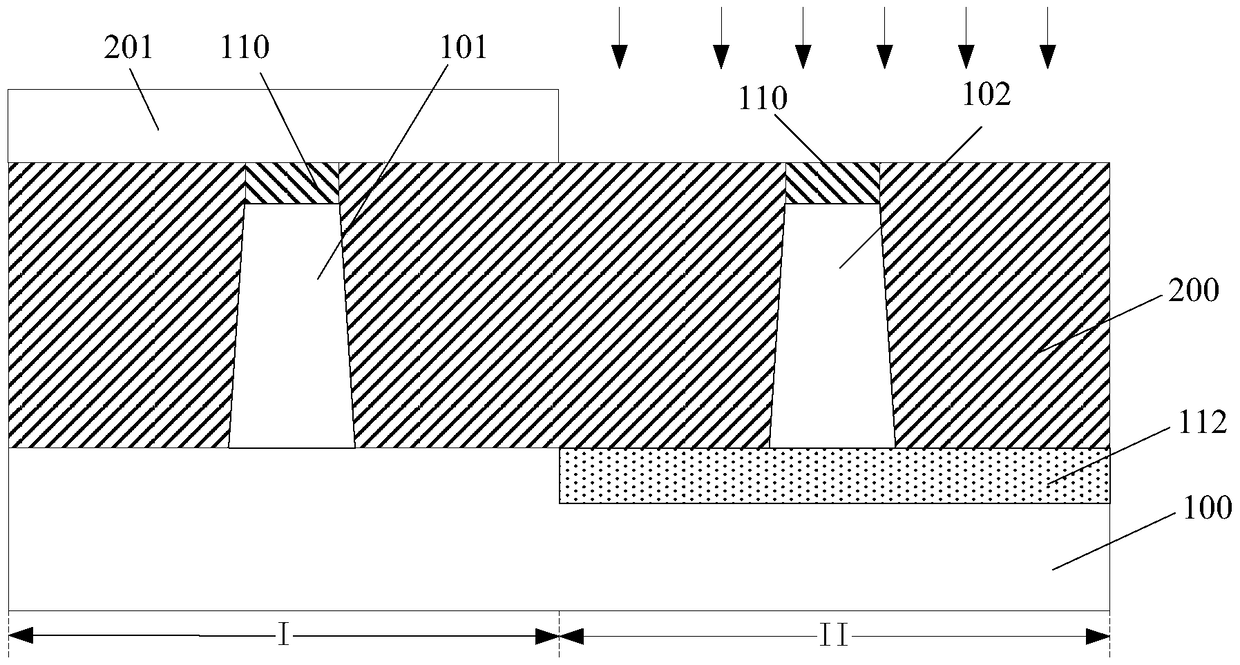

Fin field effect transistor and formation method thereof

ActiveCN105097511AImprove mobilityAvoid affecting electrical parametersSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerSingle crystal

The invention relates to a fin field effect transistor and a formation method thereof. The formation method of the fin field effect transistor comprises the steps of providing a semiconductor substrate; forming a first pin portion on the semiconductor substrate; forming an isolation material layer whose surface is flush with the top surface of the first fin portion on the semiconductor substrate; carrying out mobility enhancement ion implantation on the first fin portion, and forming an implantation region at the top end of the first fin portion; carrying out local recrystallization treatment on the implantation region, and enabling the implantation region to become a single crystal semiconductor layer containing implanted ions, wherein a hole mobility of the single crystal semiconductor layer is greater than the hole mobility of the first fin portion below the single crystal semiconductor layer; etching the isolation material layer, and forming an isolation layer whose surface is flush with the bottom surface of the single crystal semiconductor layer; and forming a first grid structure crossing the single crystal semiconductor layer. The method provided by the invention can improve the performance of the formed fin field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

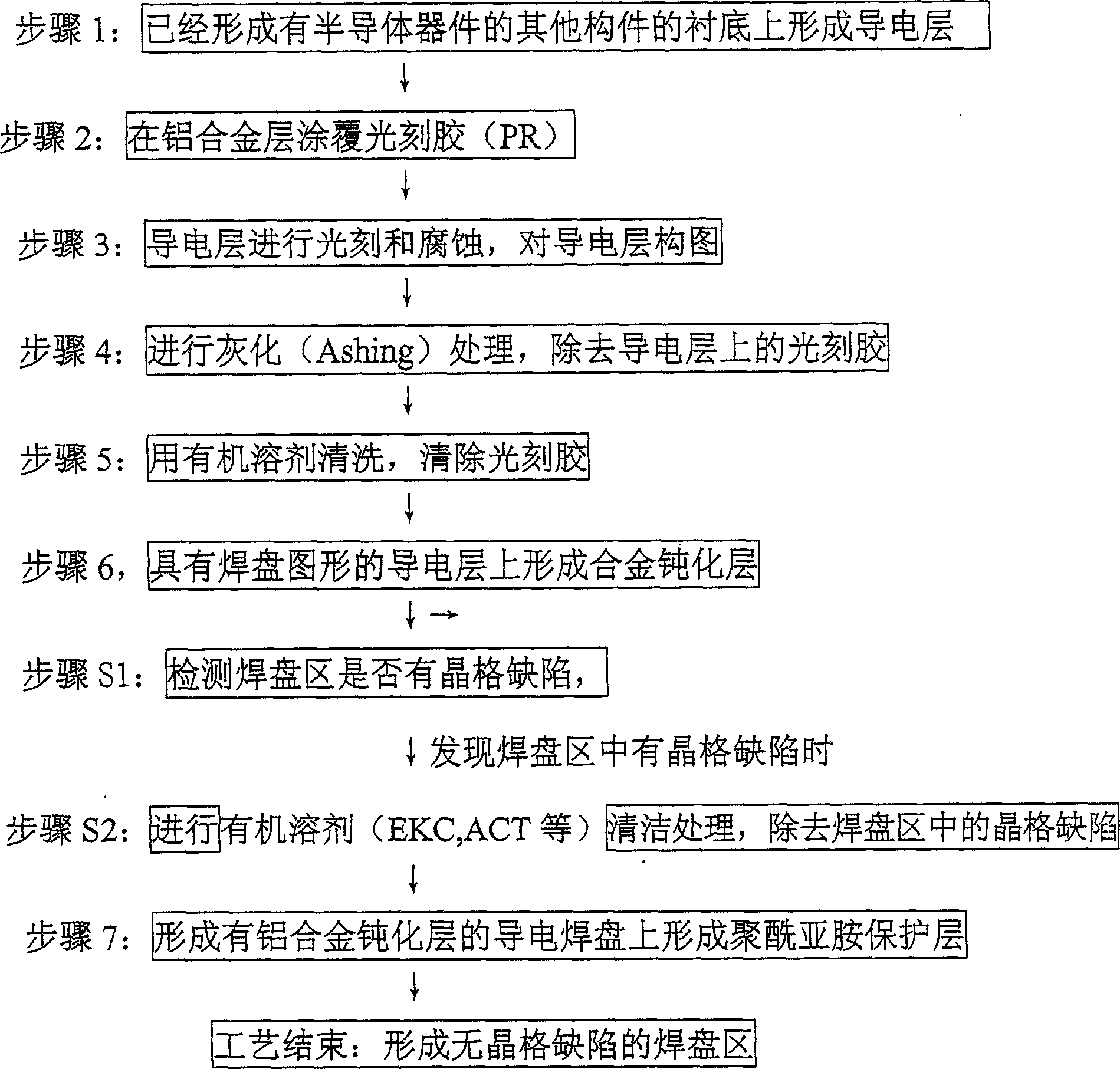

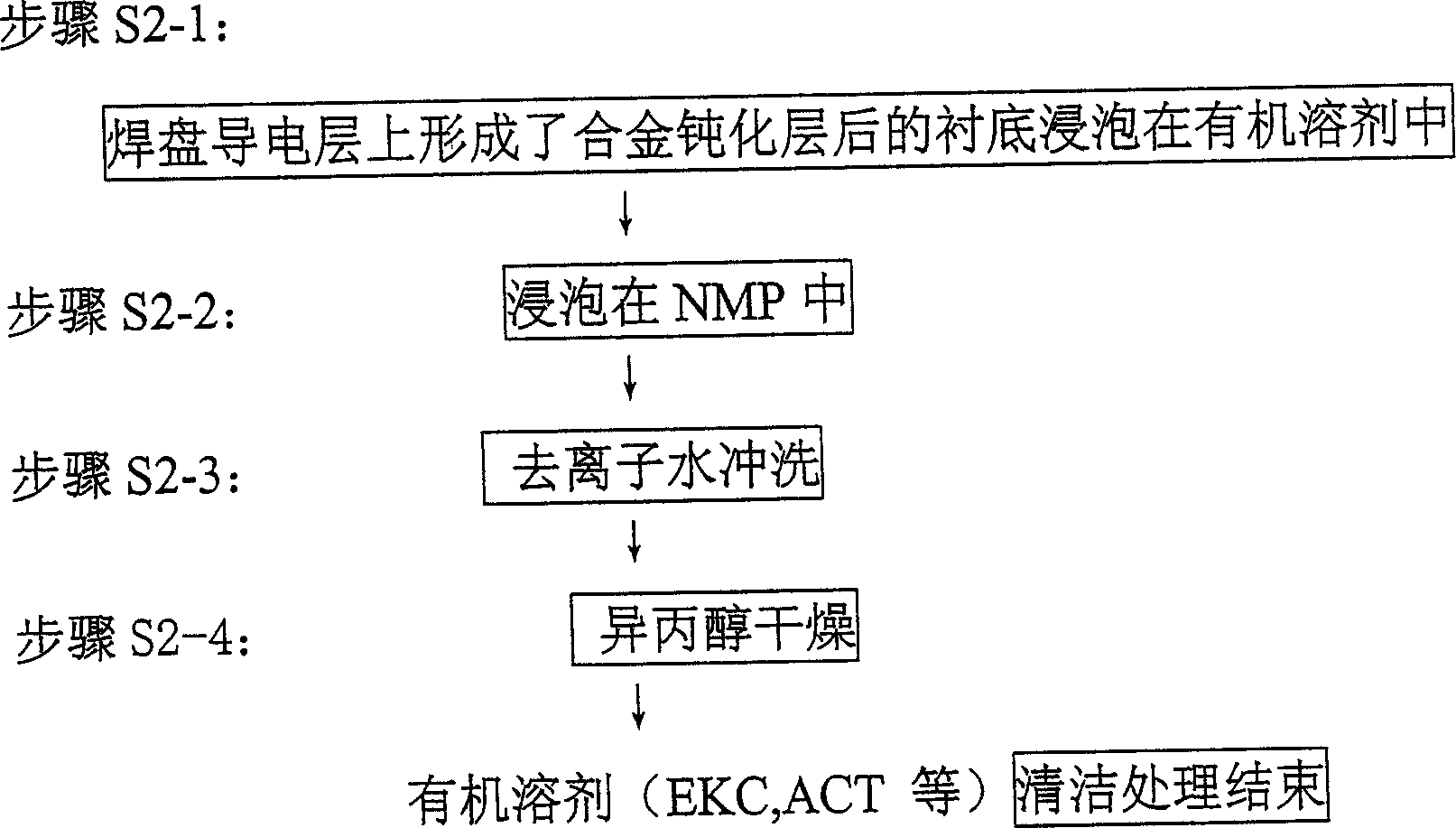

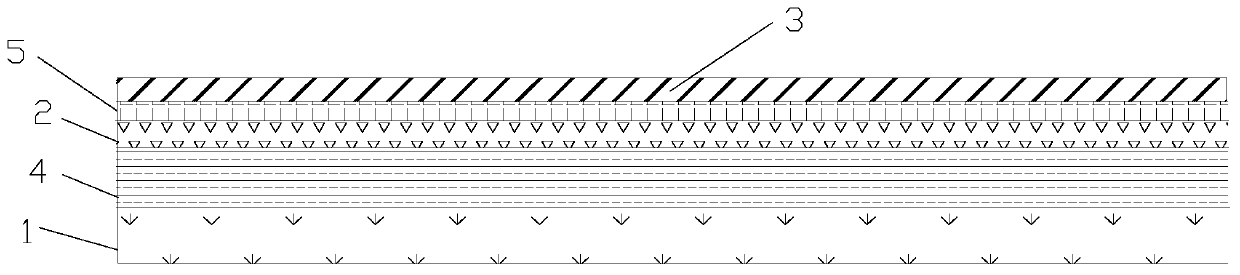

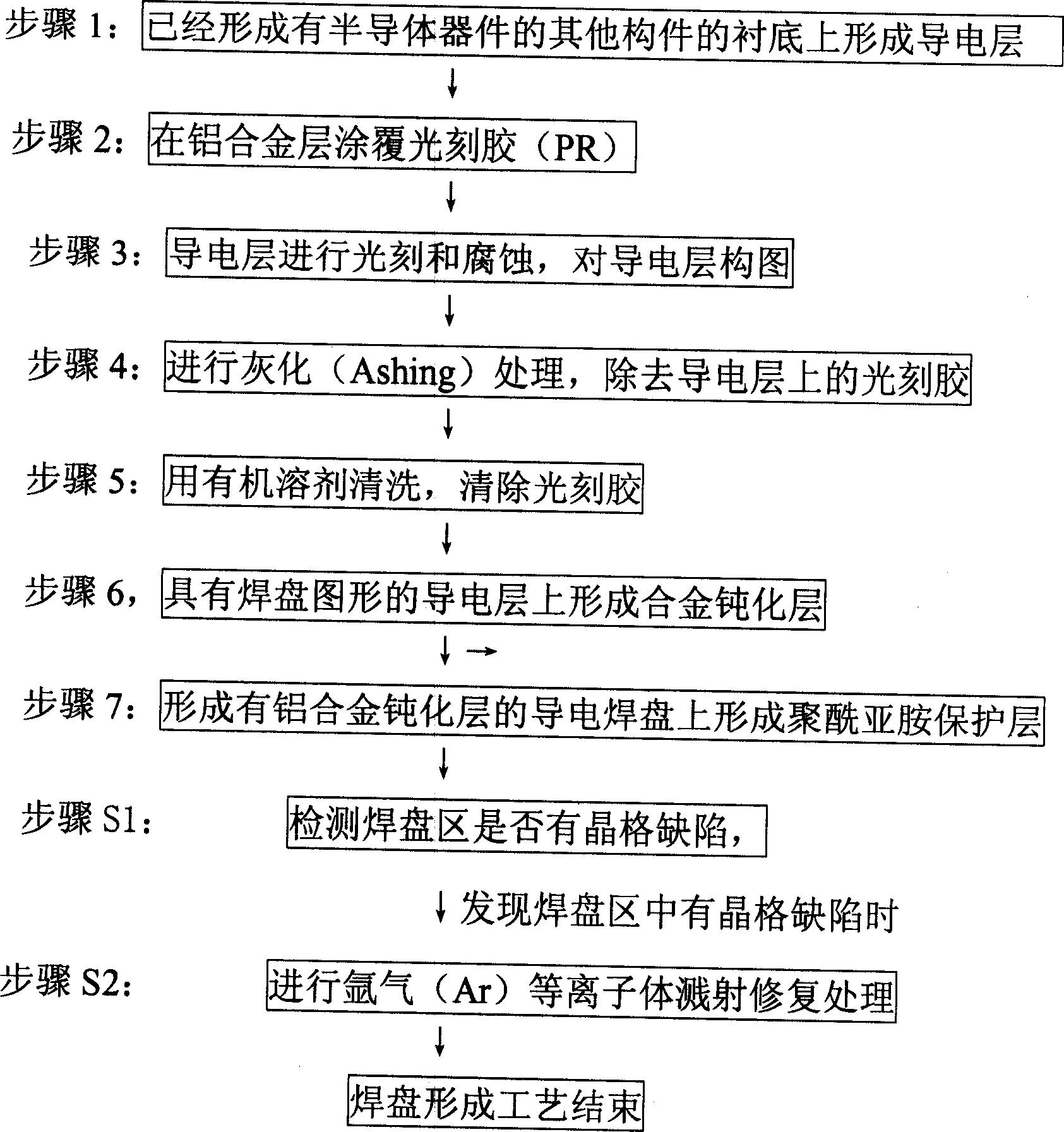

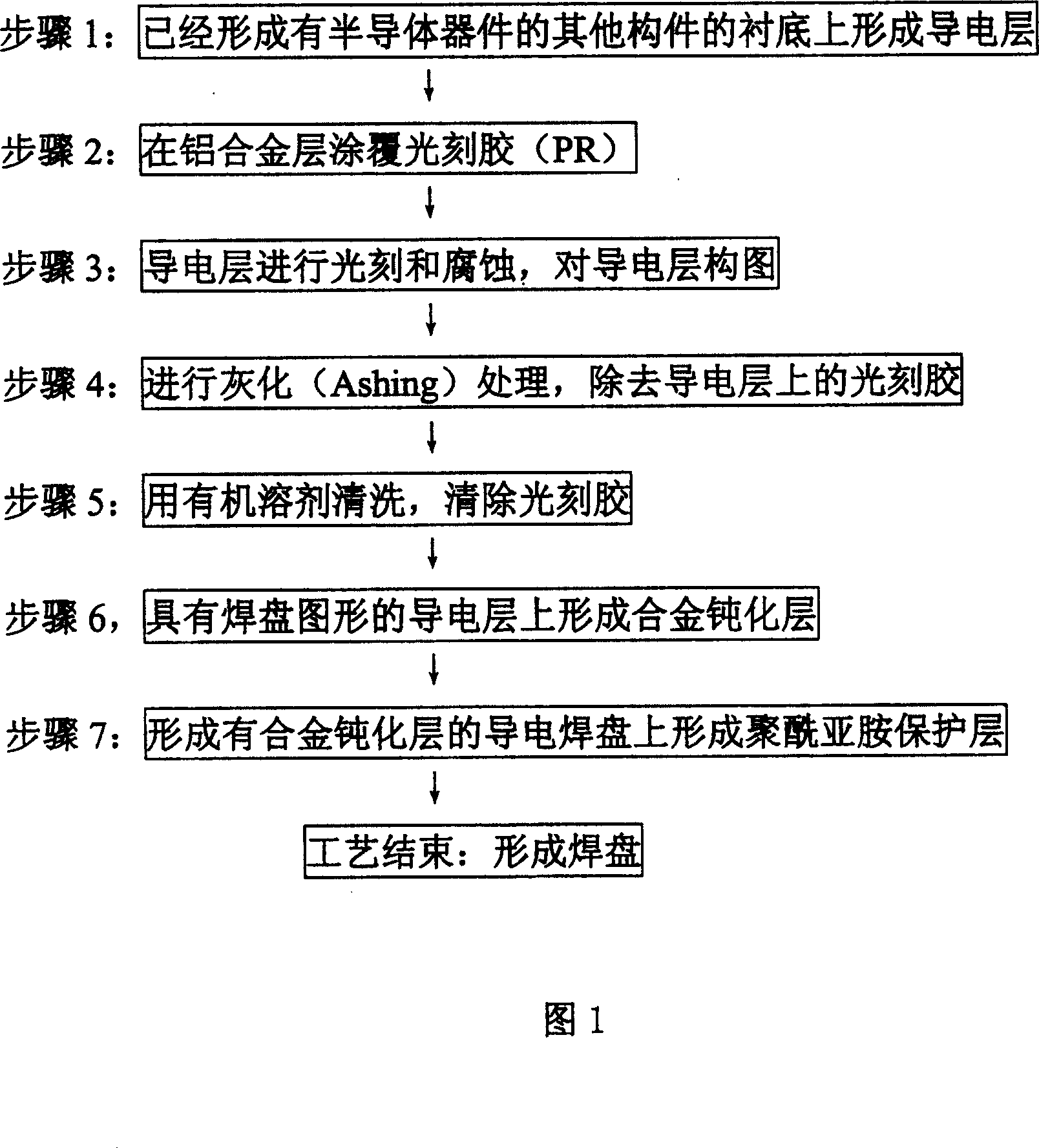

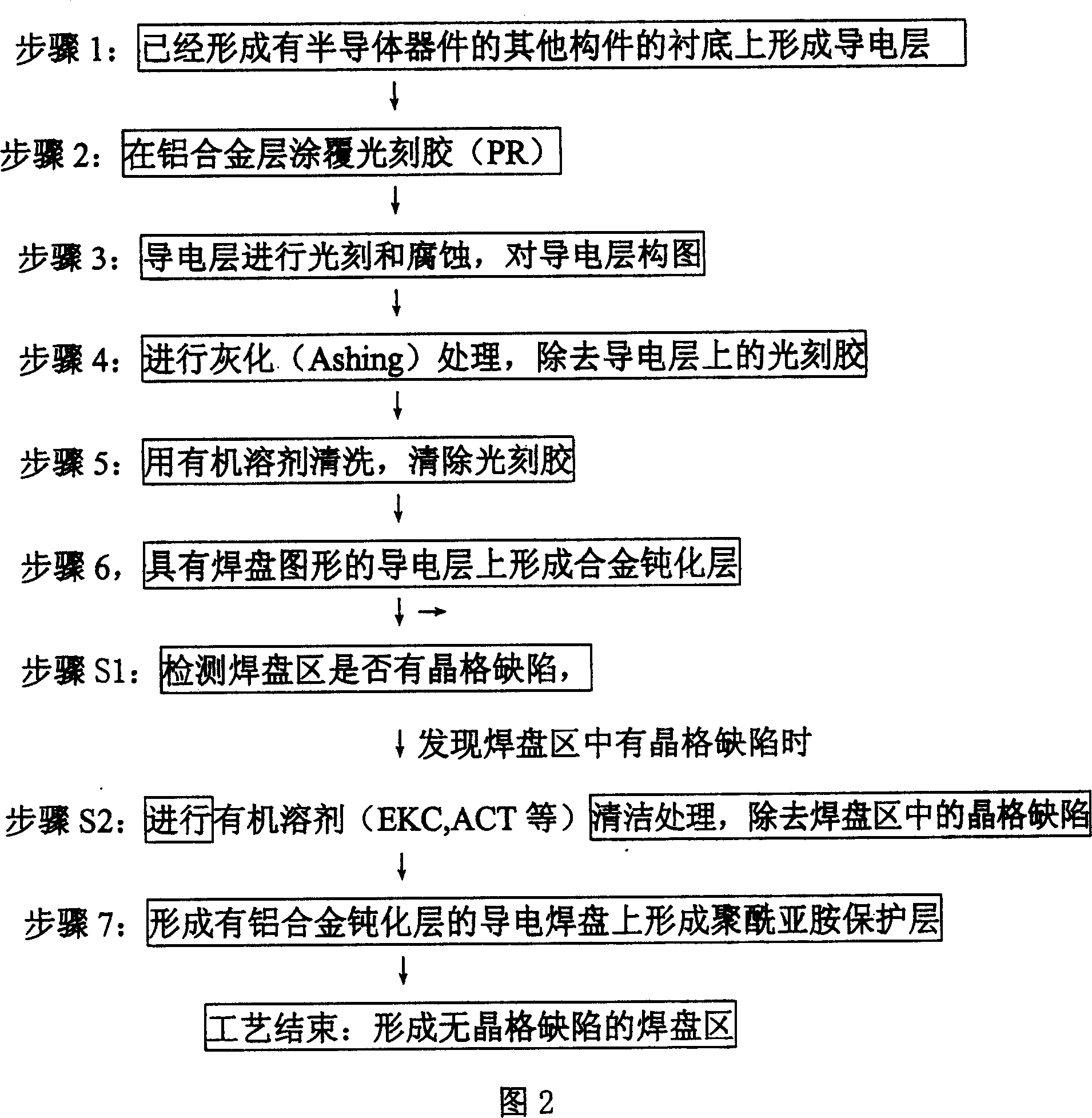

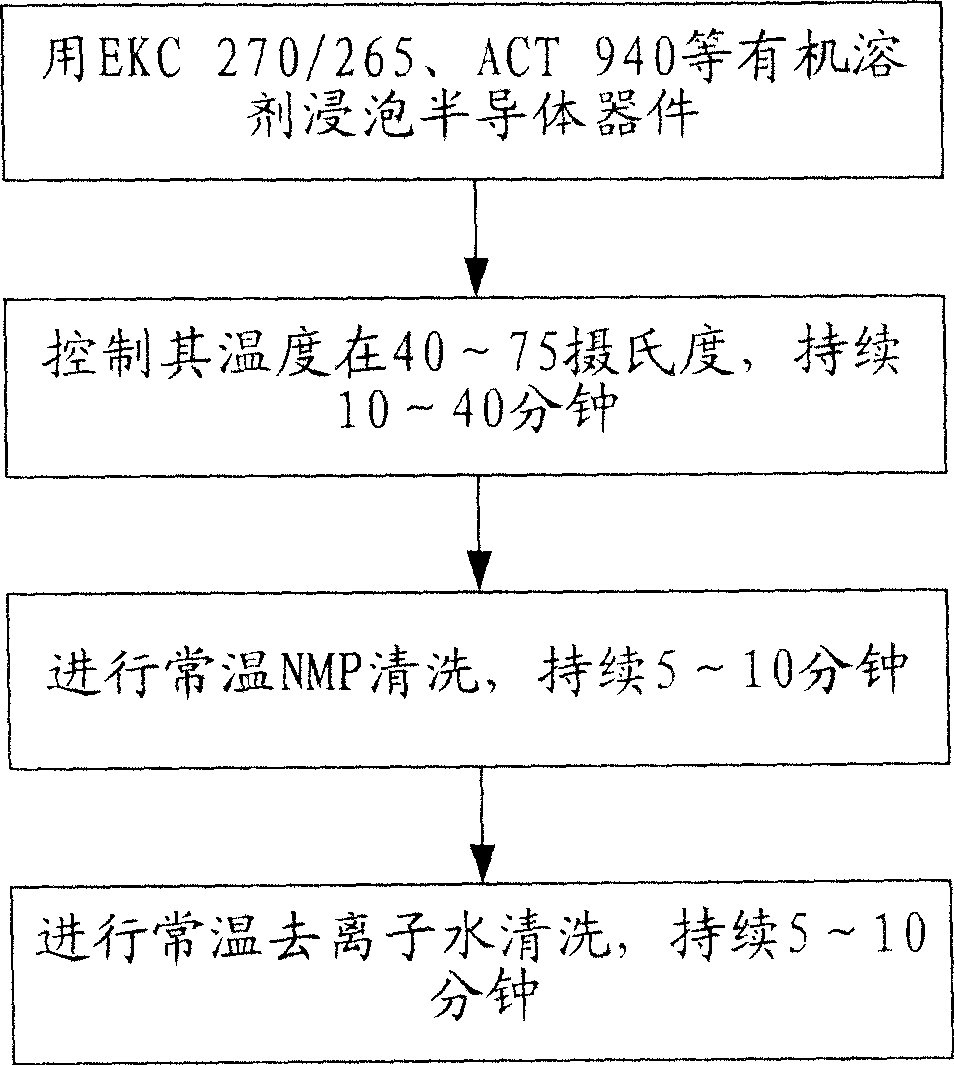

Method for removing lattice defect in pad area of semiconductor device

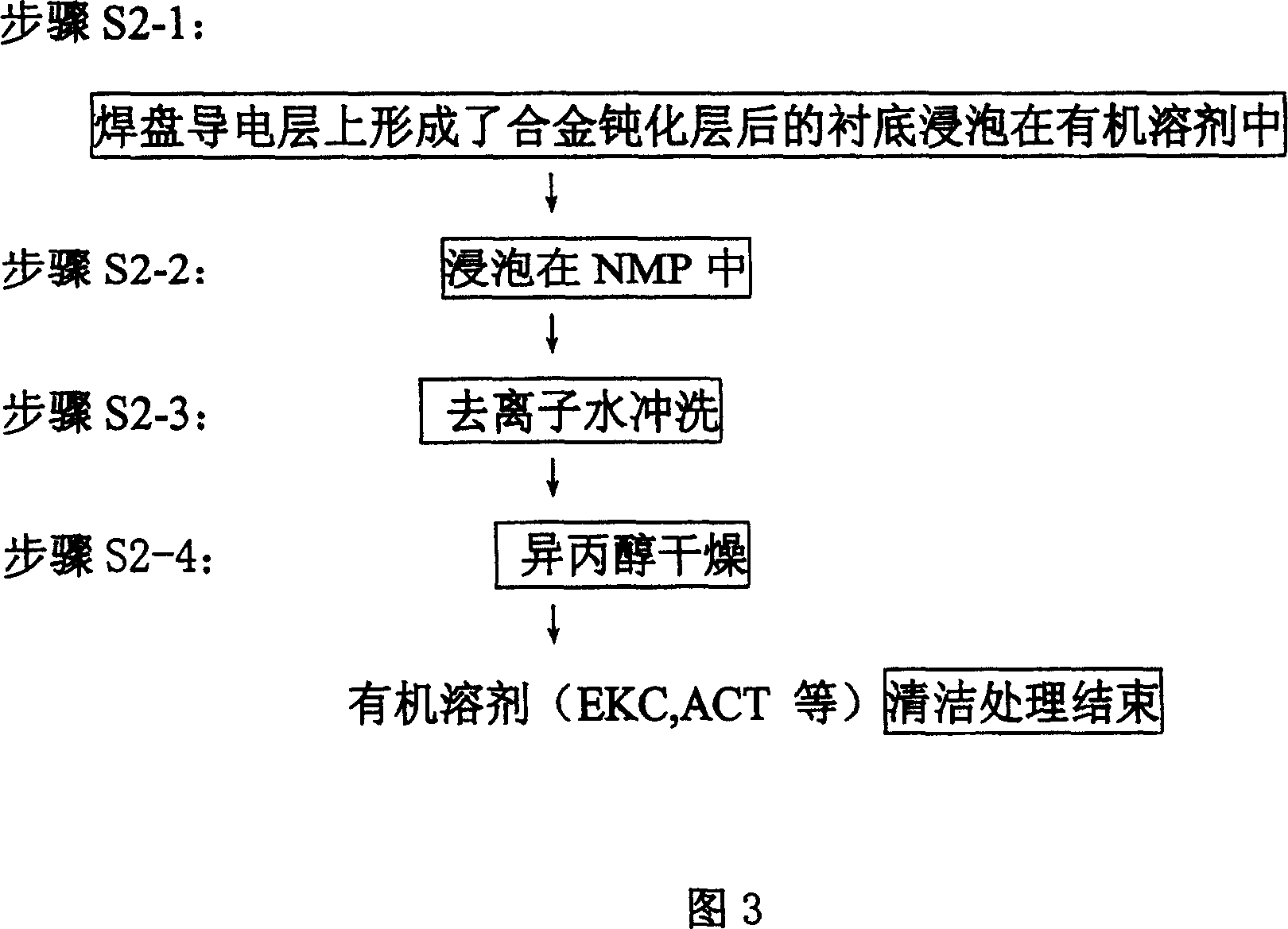

InactiveCN1725458AEliminate lattice defectsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingLattice defectsOrganic solvent

This invention discloses a method for removing lattice defect in the pad zone, after forming an Al alloy purification layer and before forming a polyimide protection layer on the pad, it is tested that if the lattice defect exists in the pad, if so, the organic solvent of EKC and ACT cleaning process is made to remove the lattice defect in the zone.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

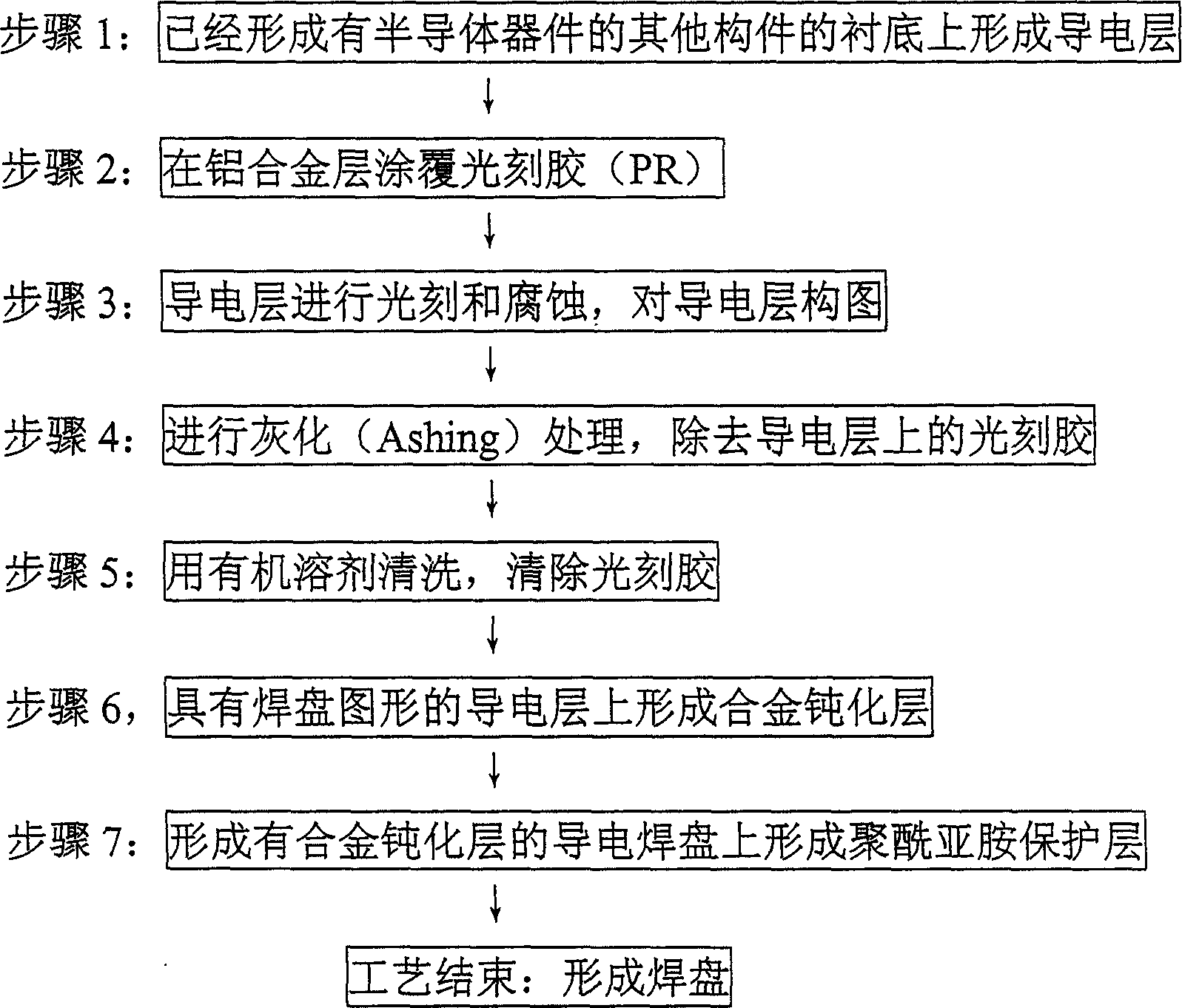

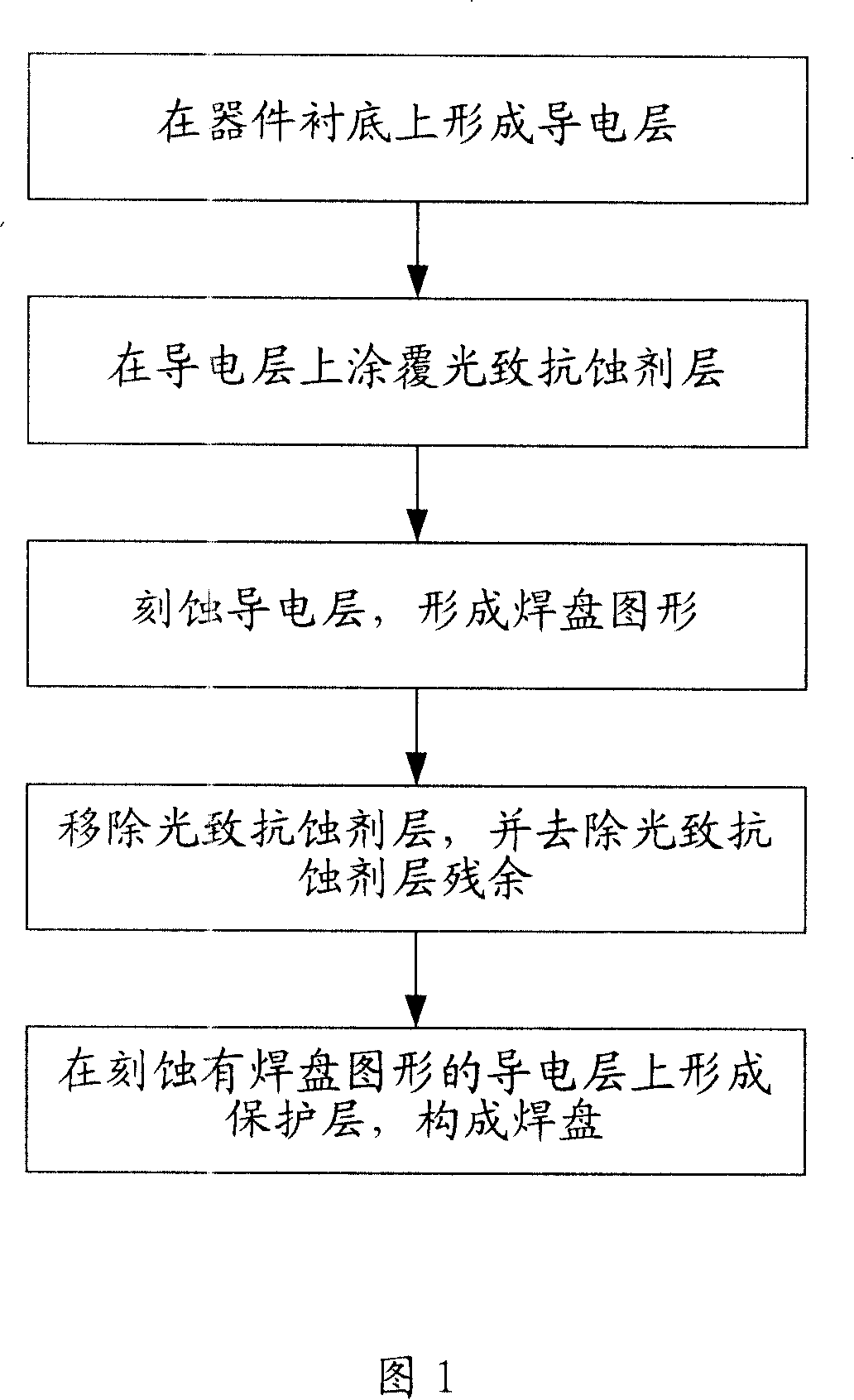

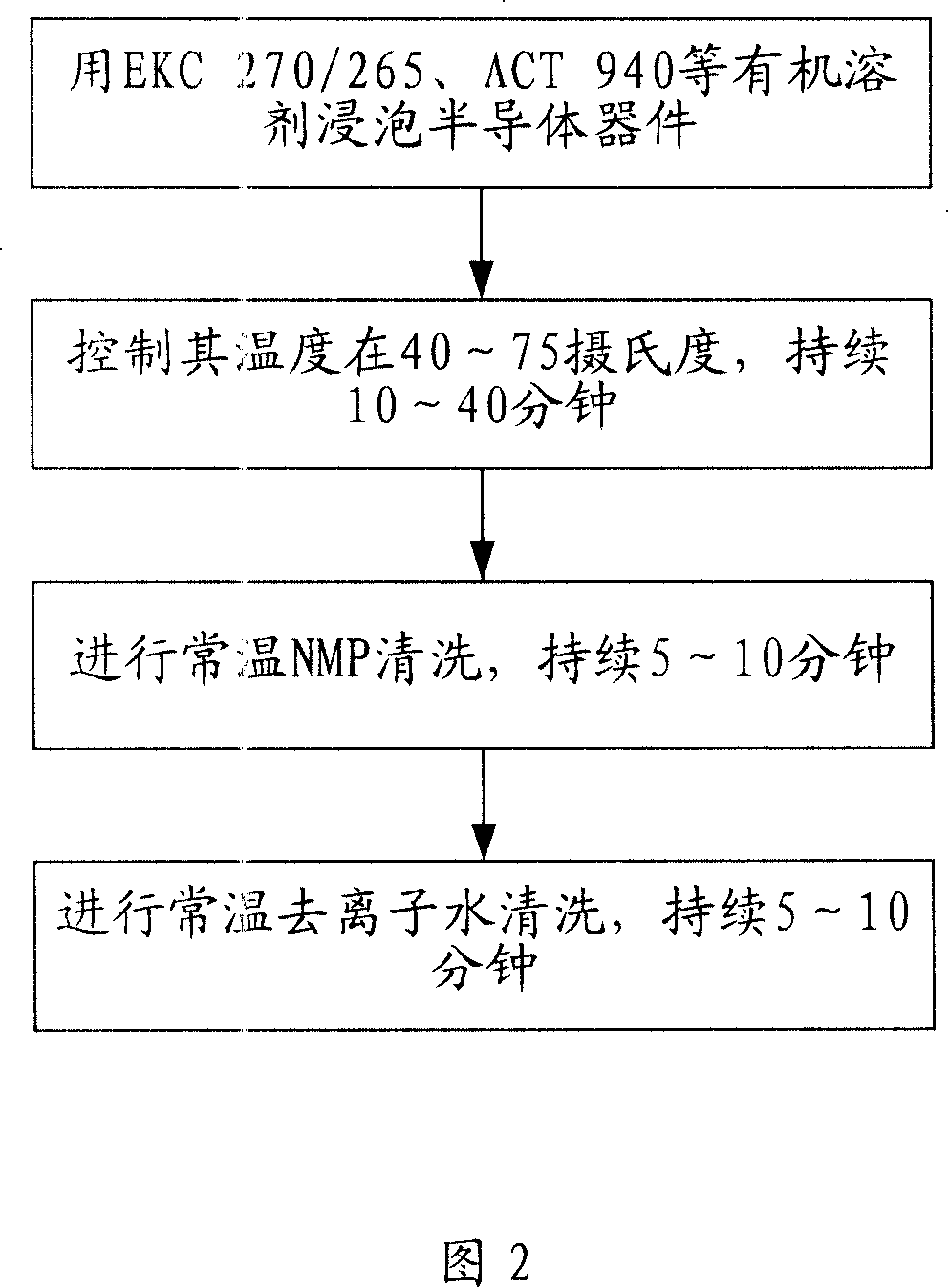

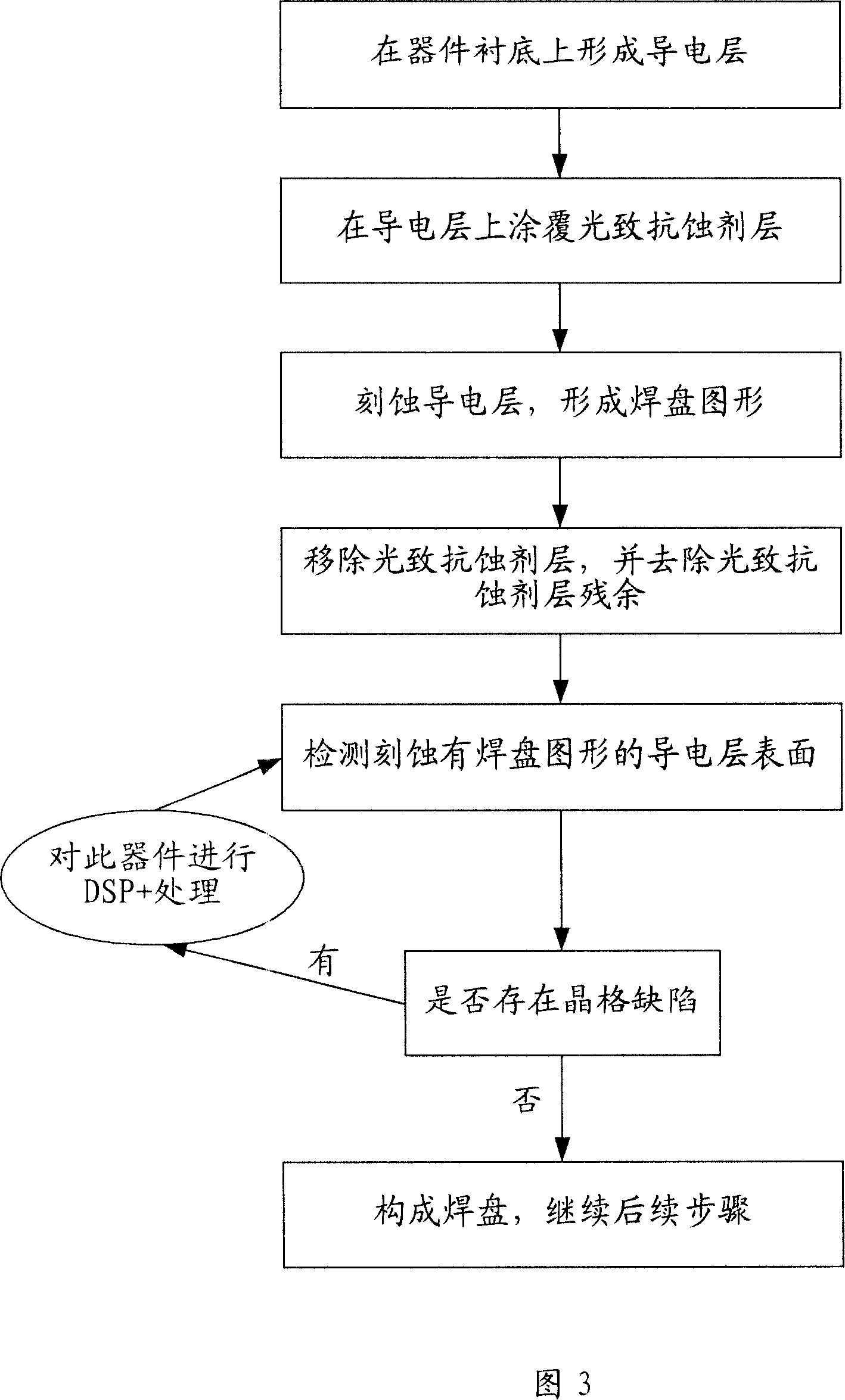

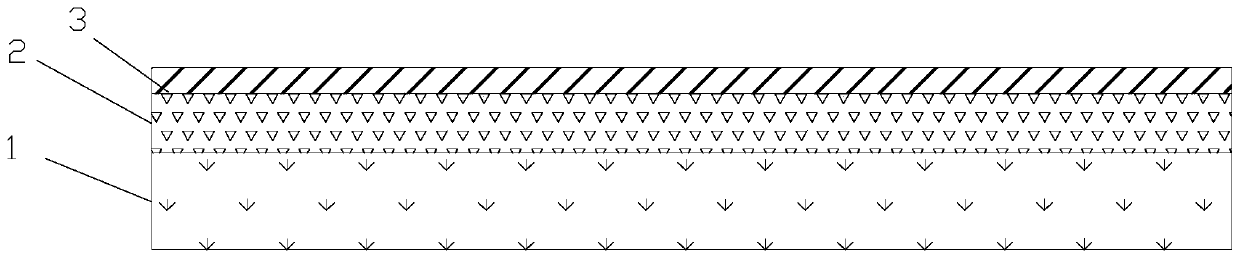

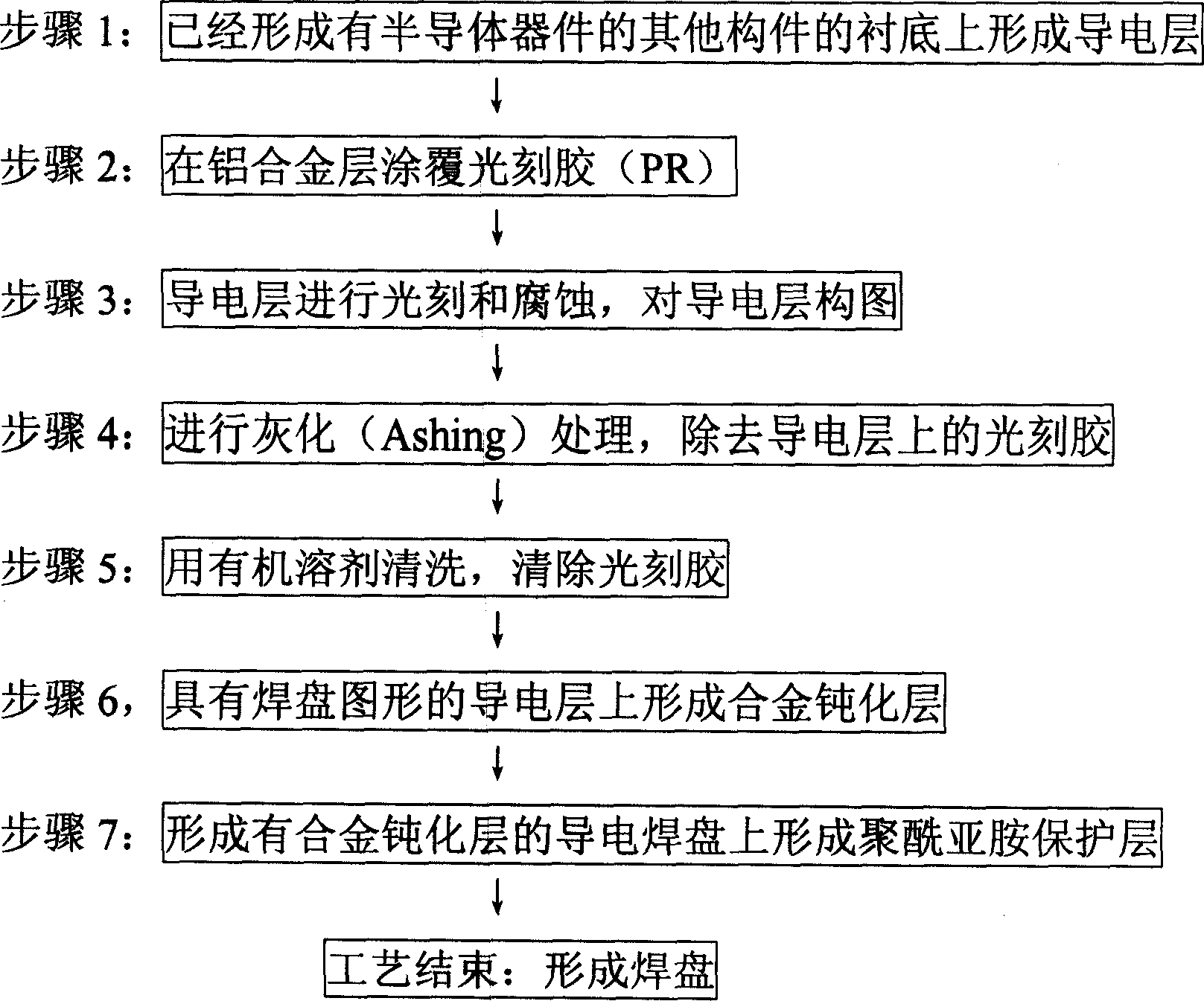

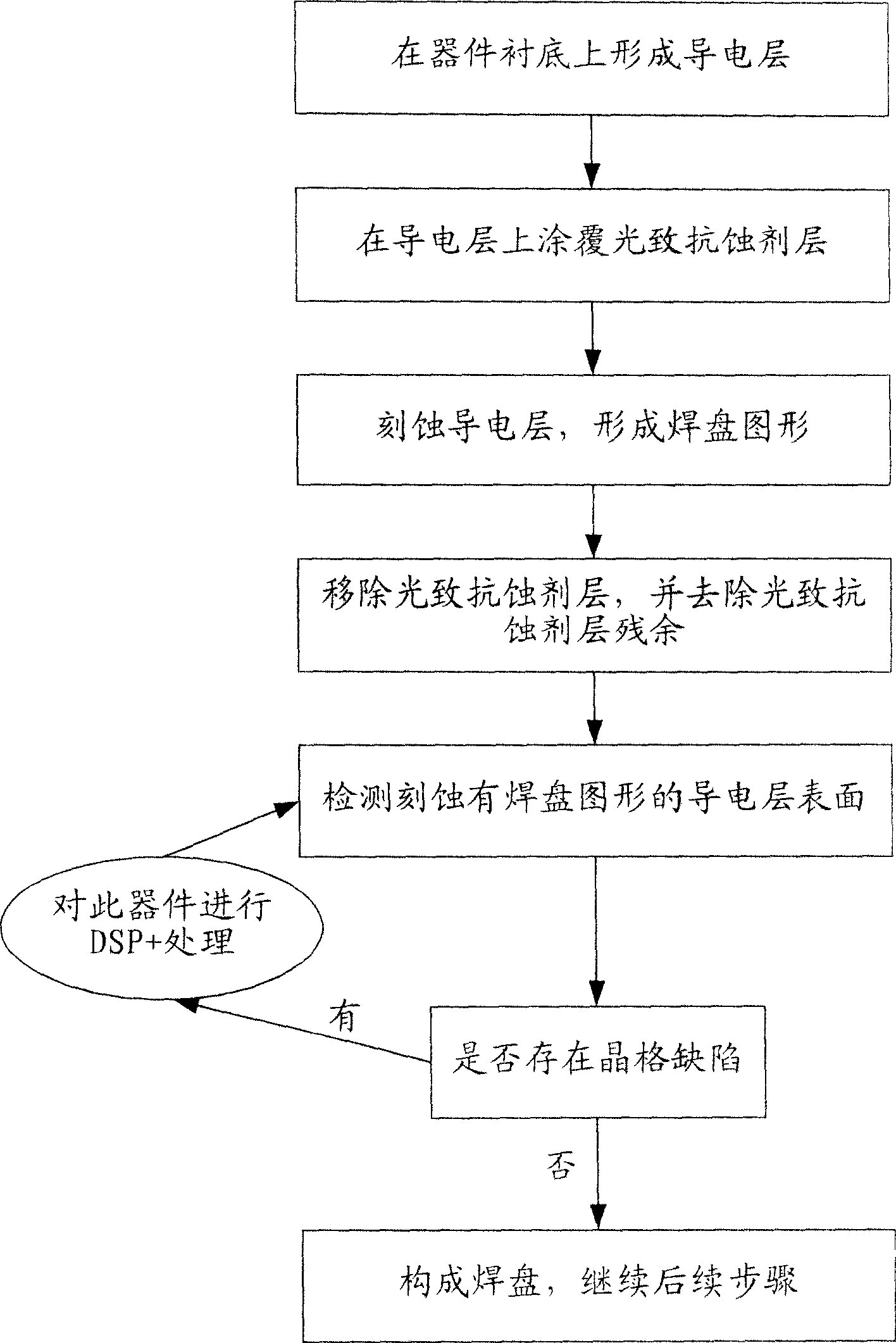

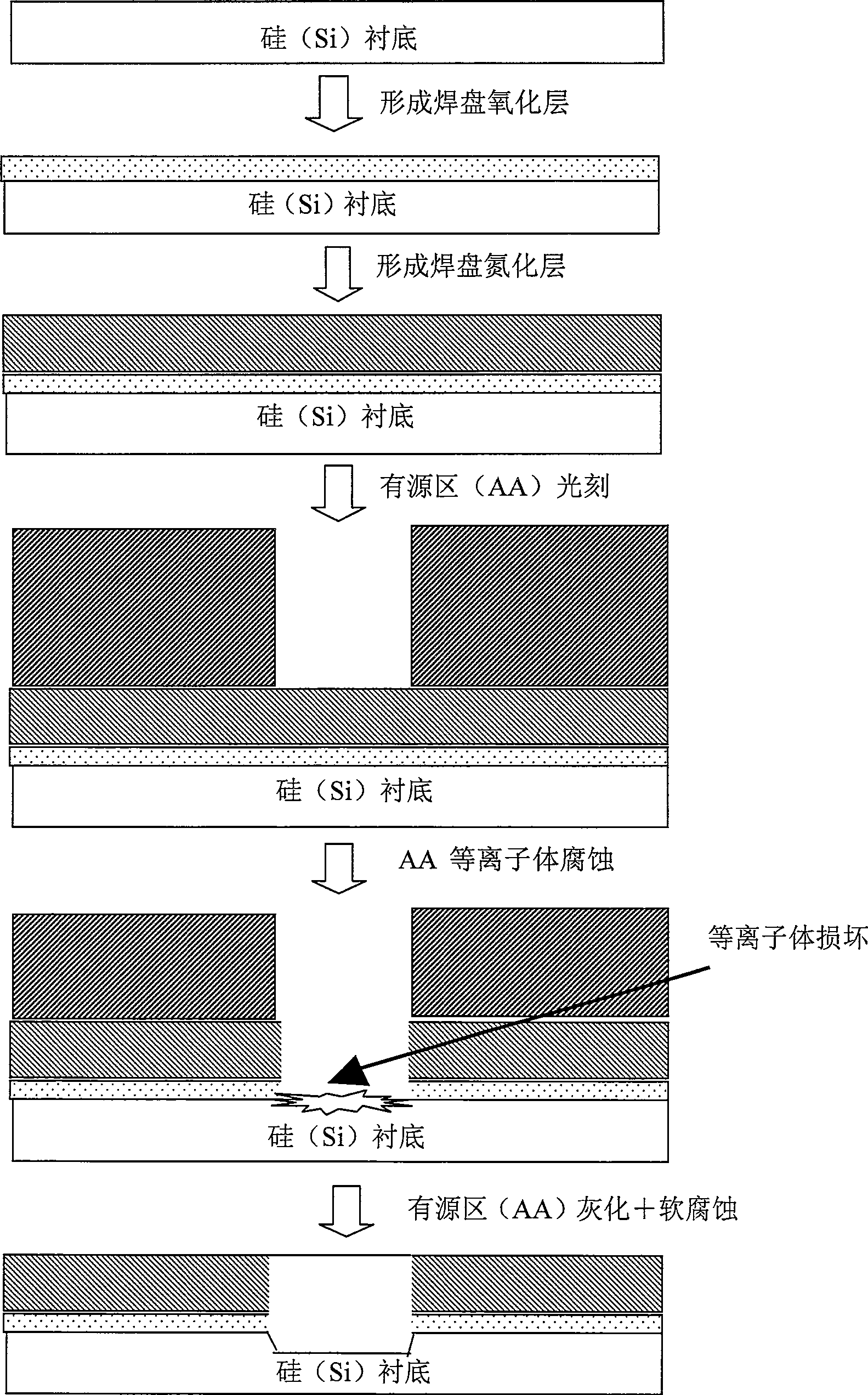

Method for forming solder pad of semiconductor device

InactiveCN101154603AEliminate lattice defectsPrevent electrochemical corrosionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingSolder pasteAqueous solution

A bonding pad forming method for semiconductor device comprises that: a current conducting layer is formed on a substrate of a semiconductor device; a bonding pad graph is etched on the current conducting layer; lattice defect detection is executed to the surface of the current conducting layer; diluted sulfur peroxide is utilized to process the lattice defects of the current conducting layer surface to form a bonding pad. The use of diluted sulfur peroxide which is a water-containing solution can remove the lattice defects of the bonding pad surface and simultaneously reduce the processing time of organic solvents, so as to improve productivity.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

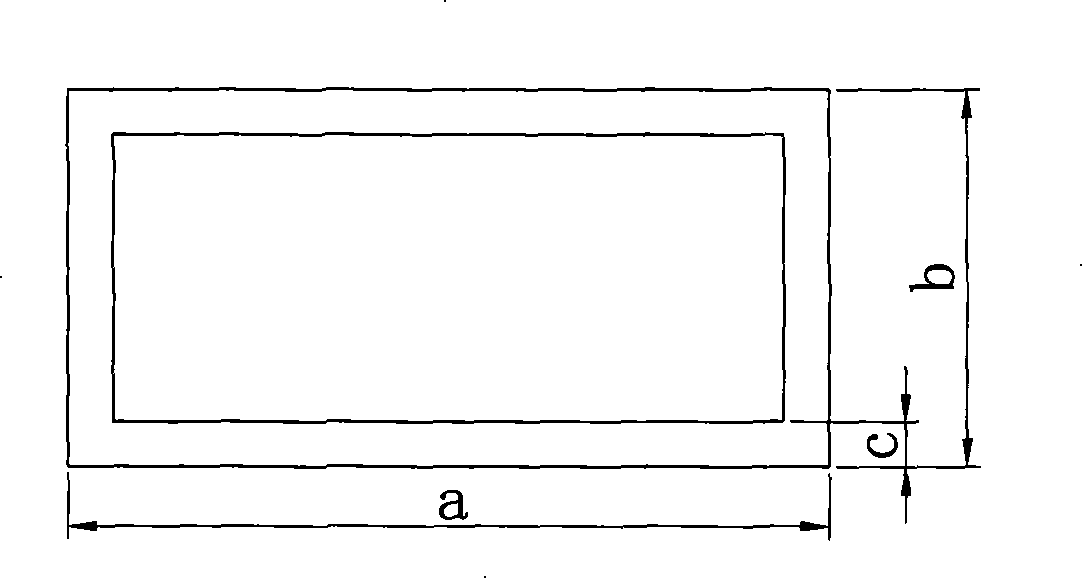

Method for processing austenite seamless stainless steel rectangular water pipe used for turbine generator

ActiveCN101245879AReduced intermediate annealingReduce cleaning effectRigid pipesRare-earth elementLanthanum

The invention relates to a processing method of an austenitic seamless stainless steel rectangle water pipe used for a turbo-generator, which sequentially has the processing steps of hot rolling round bar, continuous extruding round pipe, drawing an elliptic pipe with a non-core bar, drawing a rectangle pipe with a short core bar, and carrying out solution treatment and annealing to obtain the finished product. According to the mass percentage, the stainless steel which is adopted by the water pipe contains carbon less than or equal to 0.030%, silicon less than or equal to 1.0%, manganese less than or equal to 2.0%, sulphur less than or equal to 0.030 %, phosphorus less than or equal to 0.035%, chromium ranging from 18.00% to 20.00%, Ni ranging from 9.0% to 13.0%, rare earth element Re ranging from 0.002% to 0.008%, silver ranging from 0.001% to 0.005%, and iron and other impurities with the residual quantity; wherein, the rare earth element is a compound which consists of 40% to 45% of Ce, 40% to 45% of lanthanum and Yt with residual quantity according to the mass percentage. The processed water pipe has good toughness, strong corrosion resistance and low magnetic permeability, and is an ideal material used for the motor stator water pipes of 1000MW-class turbo-generators.

Owner:TAIXING SHENGDA COPPER IND CO LTD

High-quality polycrystalline diamond compact and preparation method thereof

InactiveCN110143021AImprove high temperature resistanceInhibit sheddingAdditive manufacturing apparatusIncreasing energy efficiencyPolycrystalline diamondCobalt

The invention relates to the technical field of super-hard composite materials, particularly to a high-quality polycrystalline diamond compact and a preparation method thereof. According to the invention, the high-quality polycrystalline diamond compact is manufactured by using double-beam 3D printing equipment which performs processing with high-power continuous beams and ultra-fast pulsed laserbeams alternately; and gradual transition layers are formed among layers, so bonding between a matrix and diamond and between the diamond and nickel is firm, and an interlayer interface is free of sudden changes in thermal and mechanical quantities. The polycrystalline diamond compact of the invention comprises, arranged from bottom to top, the matrix, a matrix-diamond gradual transition layer, adiamond layer, a diamond-nickel gradual transition layer, a nickel layer and a cobalt-free binder. The diamond-nickel gradual transition layer improves the heat dissipation performance of the polycrystalline diamond compact, prevents thermal stress corrosion from generating cracks on the surface of the diamond layer, and greatly improves the thermal stability of the polycrystalline diamond compact. Double-beam 3D printing technology used in the invention makes D-D bonding firm and ultra-high hardness to be obtained, so the polycrystalline diamond compact has high heat resistance, wear resistance and impact toughness, and thus has prolonged service life.

Owner:上海梁为科技发展有限公司

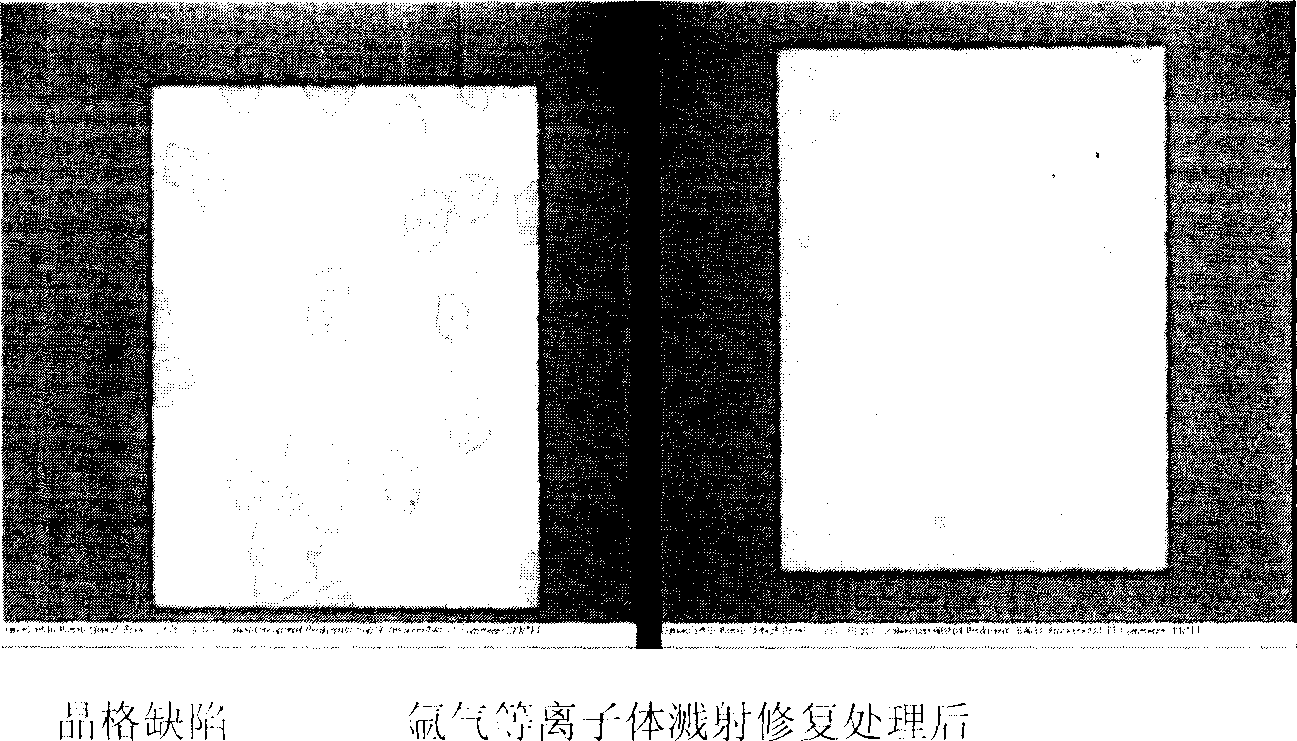

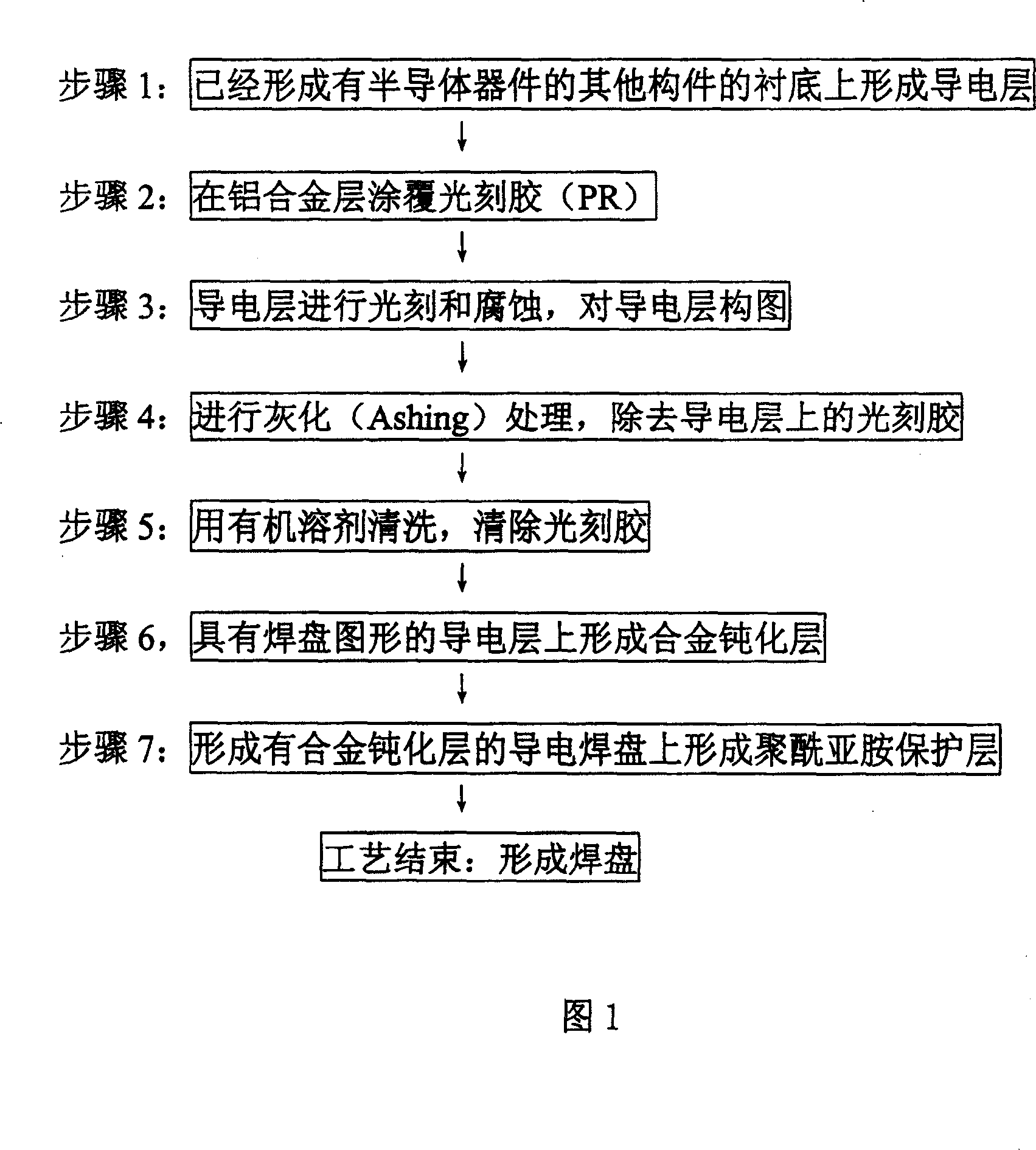

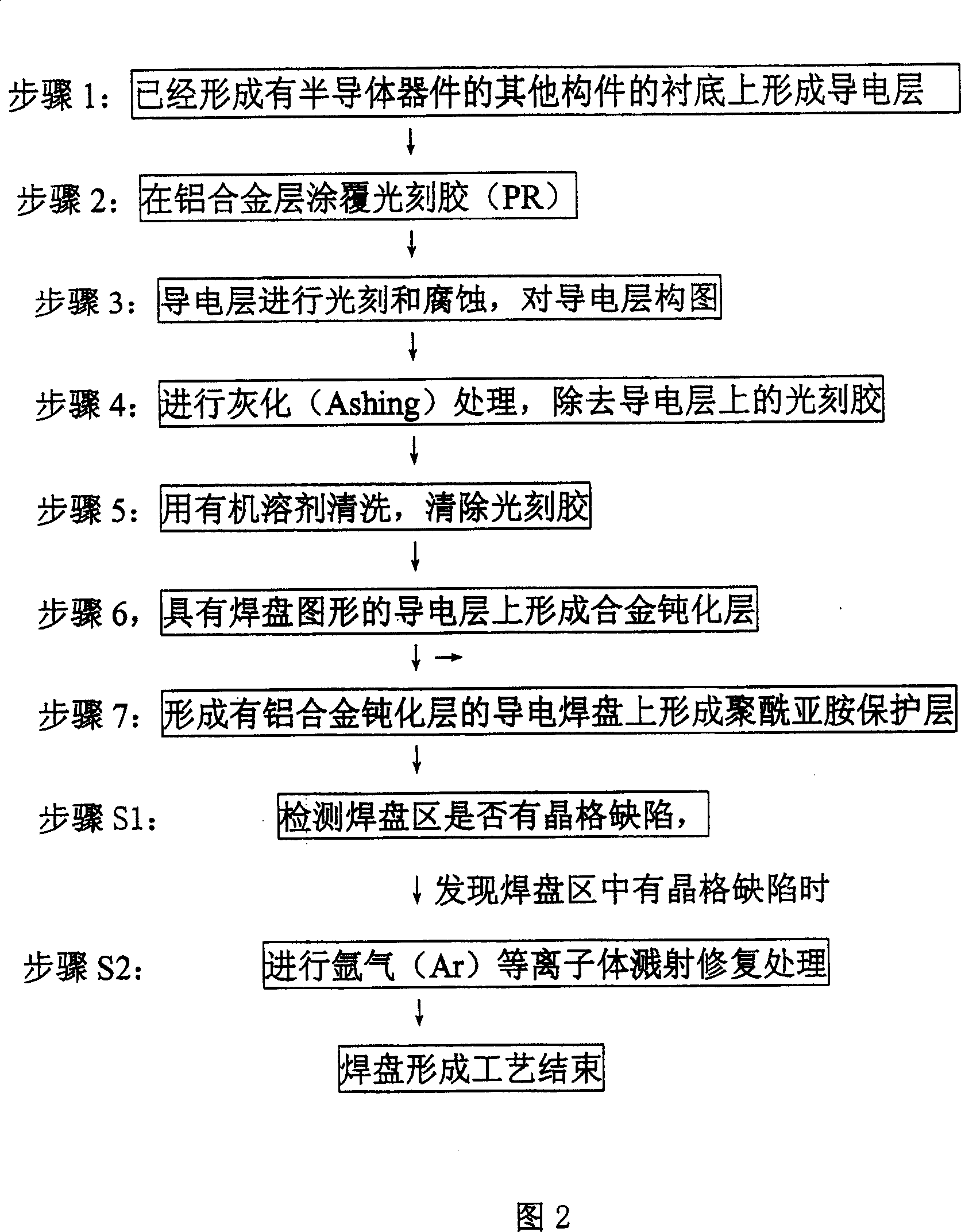

Method for removing lattice defect in pad area of semiconductor device

InactiveCN1725457AEliminate lattice defectsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingLattice defectsProtection layer

This invention discloses a method for removing lattice defect in the pad zone of a semiconductor device with Ar plasma sputter reparation which forms a polyimide protection layer then tests if lattice defect exists in the pad zone, if so, the Ar plasma sputter is made to repair and remove the lattice defect.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

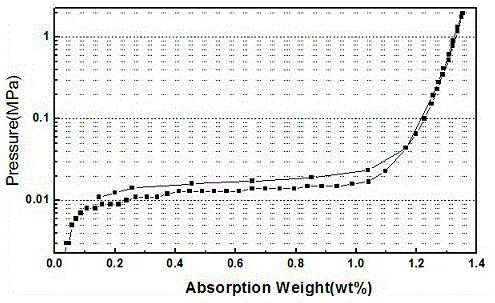

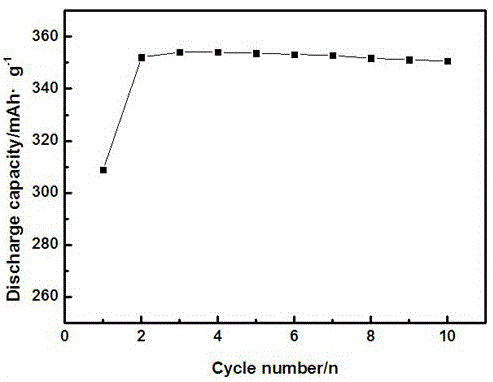

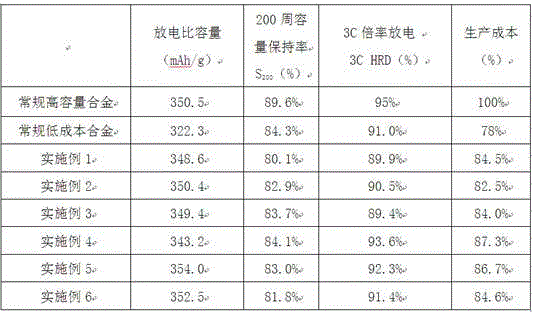

Hydrogen storage alloy for nickel-metal hydride battery and manufacturing method of hydrogen storage alloy

ActiveCN105463256AImprove performanceImprove discharge capacityCell electrodesImpurityNickel–metal hydride battery

The invention relates to hydrogen storage alloy for a nickel-metal hydride battery and a manufacturing method of the hydrogen storage alloy. The chemical formula of the hydrogen storage alloy is La1-x-yCexReyNi4.83-a-b-cCoaMnbAlcMd, x, y, a, b and c in the formula are atomic ratios, and the ranges of x, y, a, b and c satisfy the conditions that x=(0.175, 0.20, 0.30 and 0.35), y=(0.015, 0.02, 0.03 and 0.05), a=(0.15, 0.18, 0.20 and 0.25), b=(0.36, 0.42, 0.54 and 0.85), c=(0.15, 0.18 and 0.21), d=(0.25, 0.45 and 0.56), 0.19<=x+y<=0.4, and 0.9<=a+b+c+d<=1.4, wherein Re is one of Y, Zr and Gd, and M is at least one of Fe, Cr and Si. In the manufacturing process, gas and impurities in the alloy are removed in a film forming manner, raw materials are fully alloyed, annealing treatment is used as assistance, the composition segregation of the alloy can be remarkably reduced, and lattice imperfection and lattice stress are eliminated. The hydrogen storage alloy manufactured through the method has the beneficial effects of being high in discharge capacity and anti-pulverization capacity, low in production cost and the like, and the requirements of the Ni-MH battery for production cost and the performance can be met.

Owner:INNER MONGOLIA XIAOKE HYDROGEN STORAGE ALLOY CO LTD

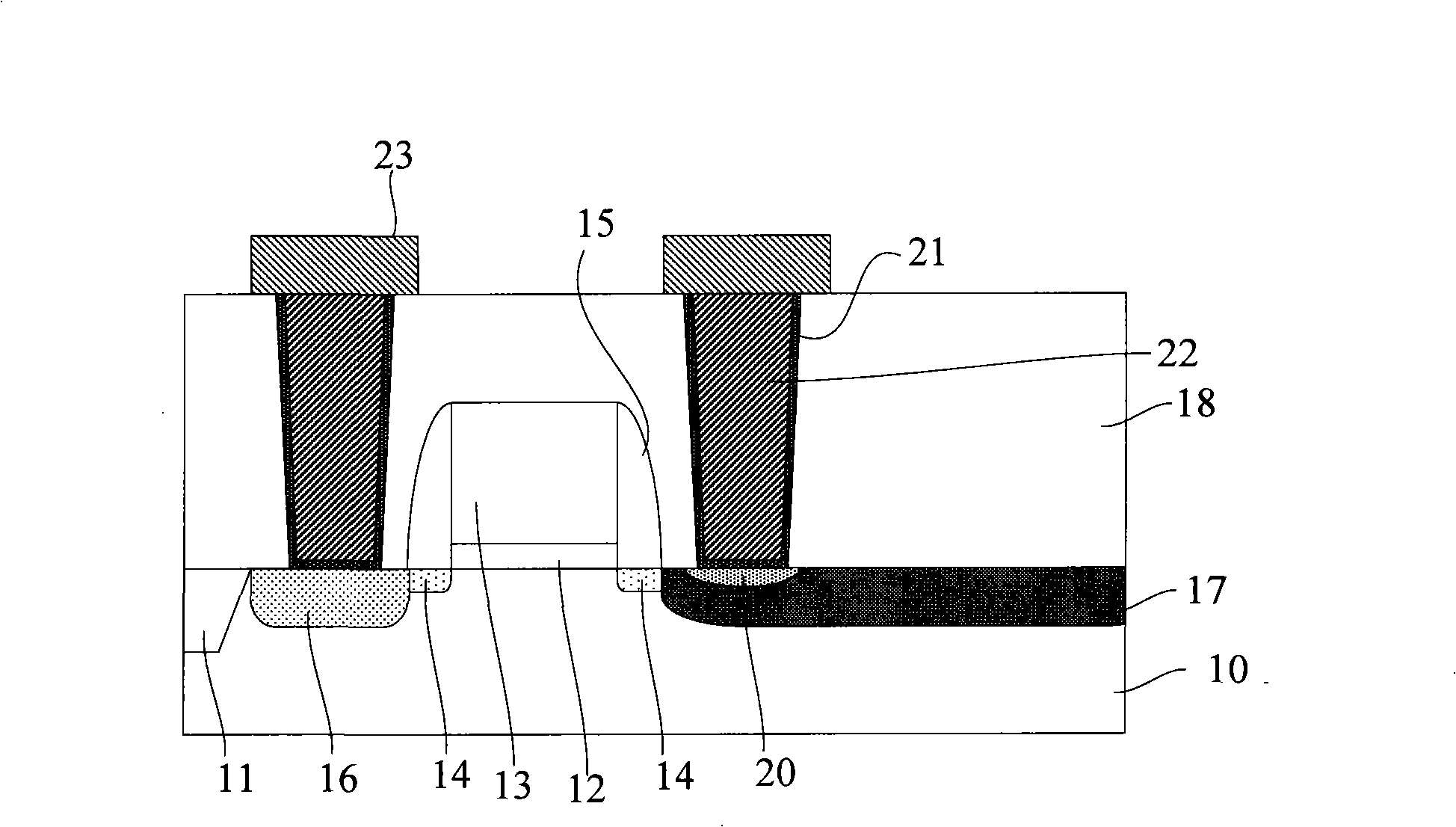

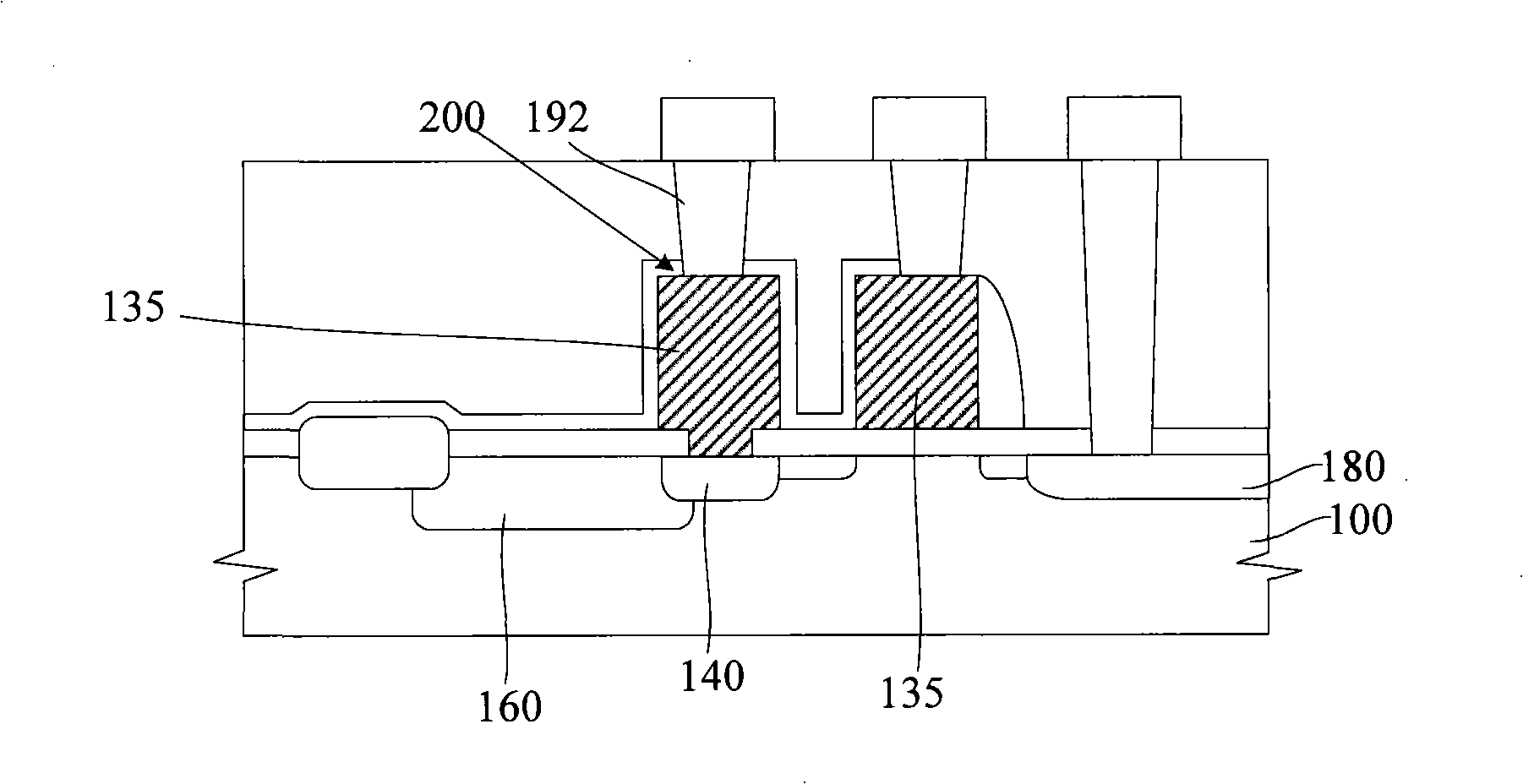

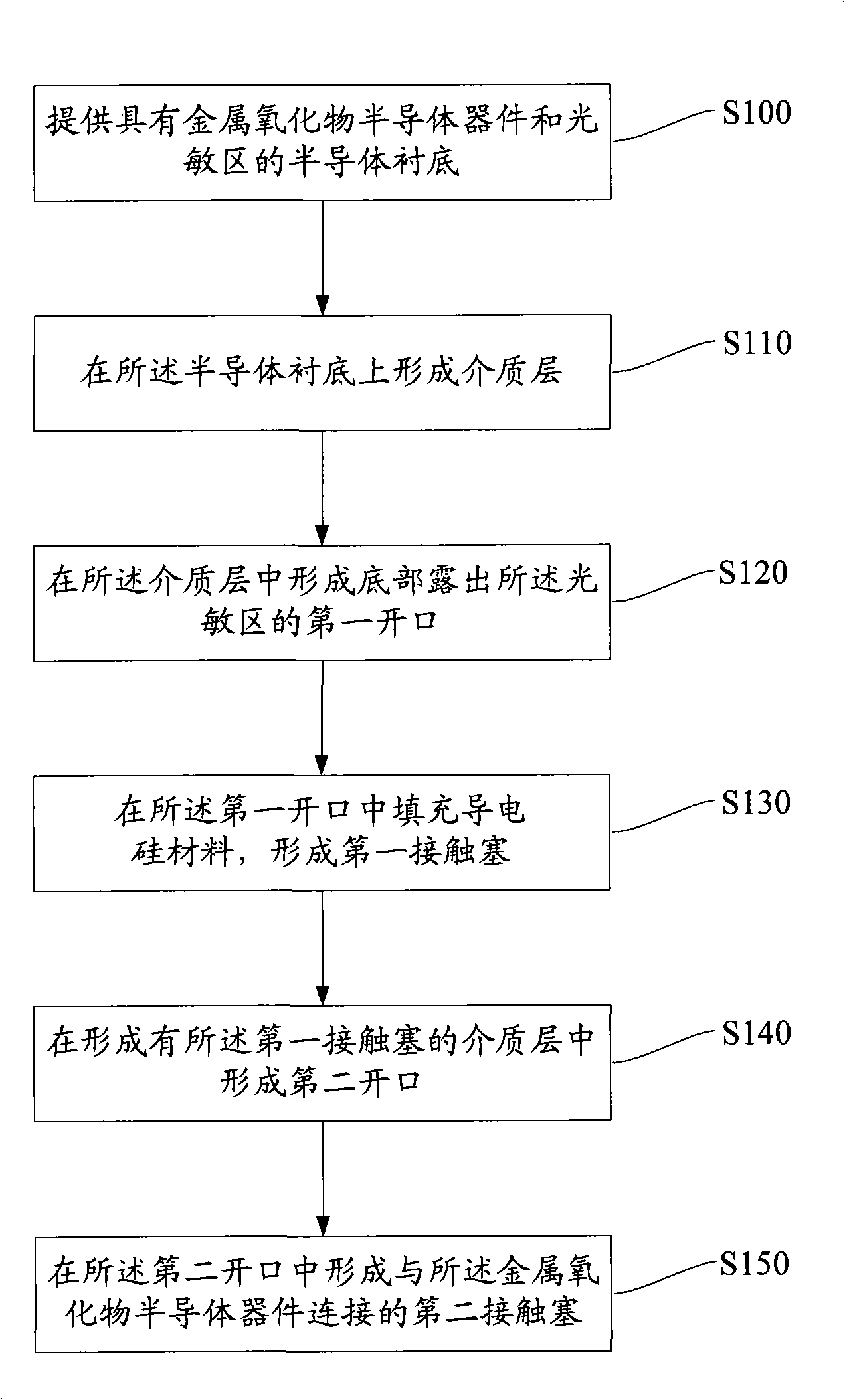

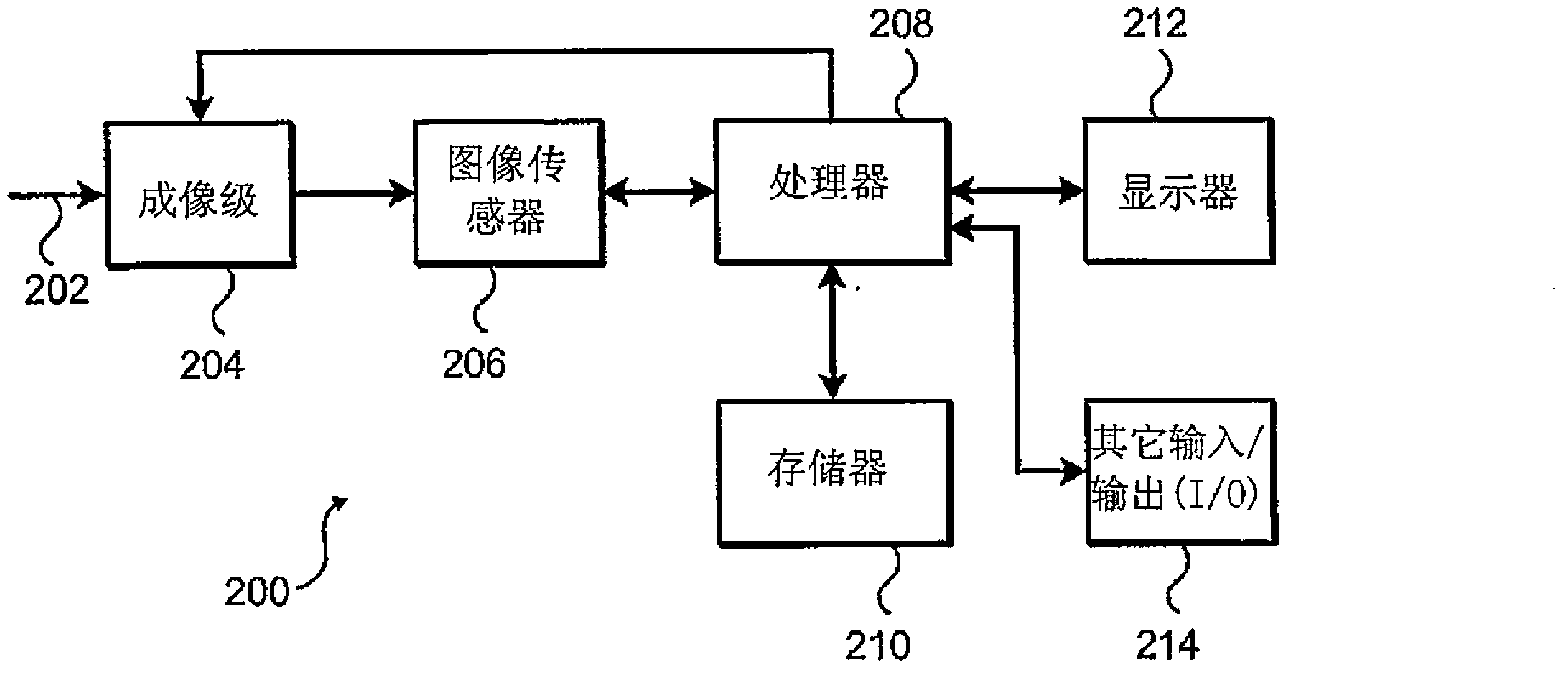

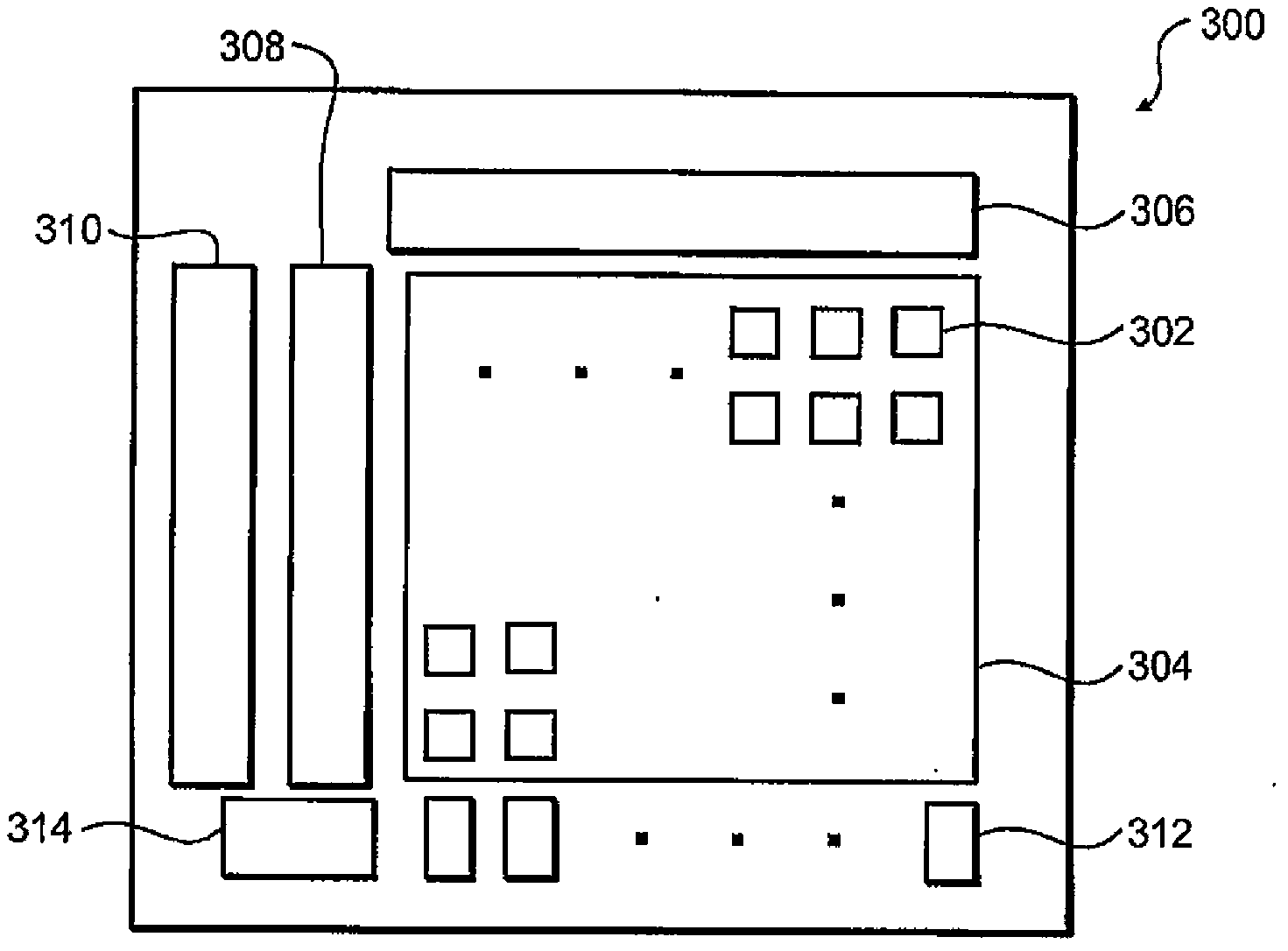

Compensating metal oxide semiconductor image sensor and manufacturing method thereof

InactiveCN101330050AReduce dark currentEliminate leakage currentSemiconductor/solid-state device detailsSolid-state devicesMedia layerSemiconductor

The invention relates to a method for producing a complementary metal oxide semiconductor image sensor, which comprises the following steps of: providing a semiconductor substrate which is provided with a metallic oxide semiconductor device and a photosensitive area; forming a medium layer on the semiconductor substrate; forming a first opening in the medium layer, wherein, the bottom part of the first opening protrudes from the photosensitive area; forming a first contact stopper by filling a conductive silicon material in the first opening; forming a second opening in the medium layer where the first contact stopper is formed; and forming a second contact stopper connected with the metallic oxide semiconductor device in the second opening. The invention also provides the complementary metal oxide semiconductor image sensor. The invention can reduce the leakage current of the complementary metal oxide semiconductor image sensor and enhance the performance of the device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

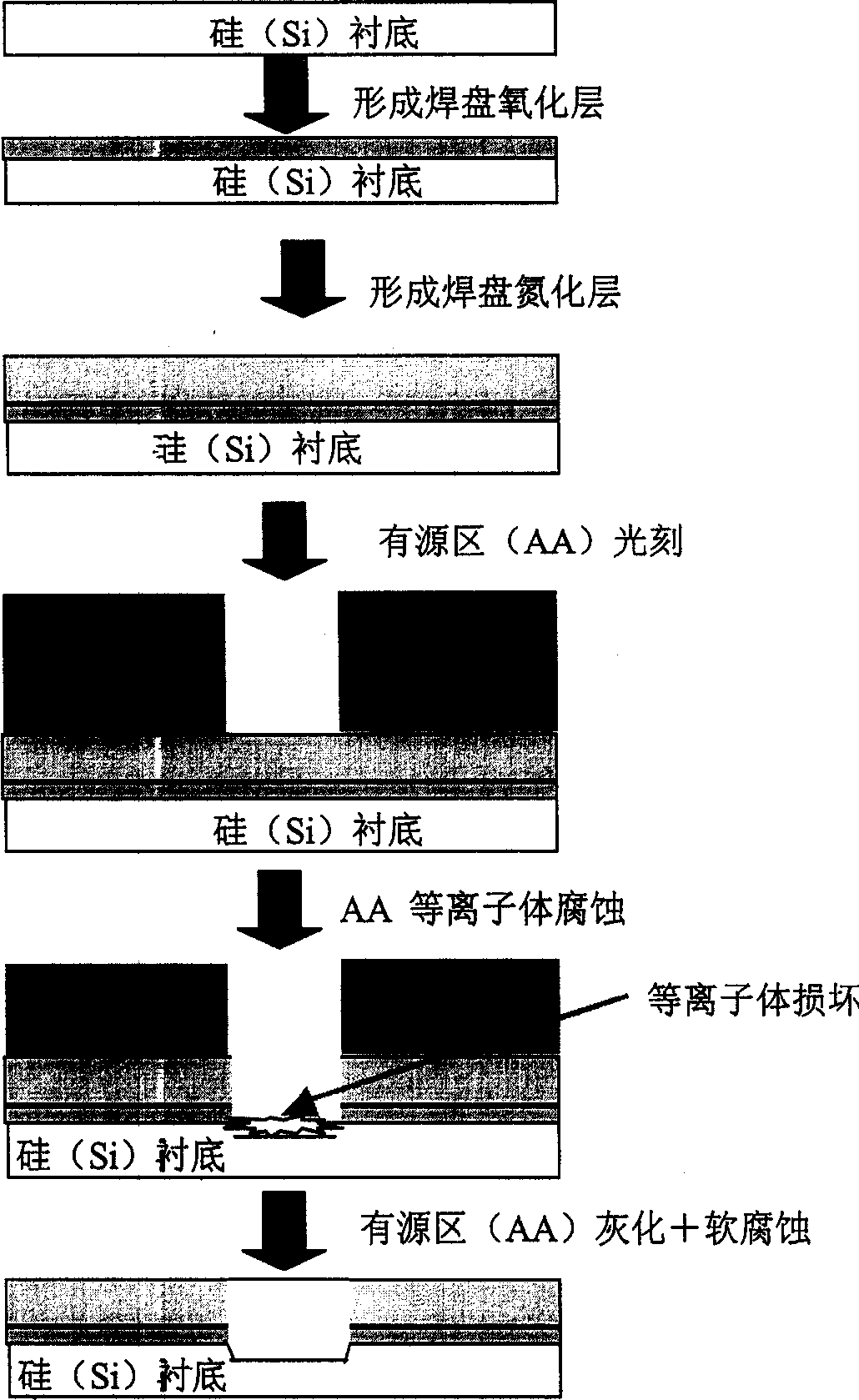

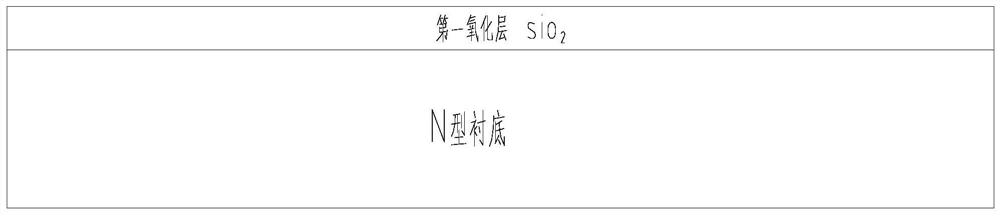

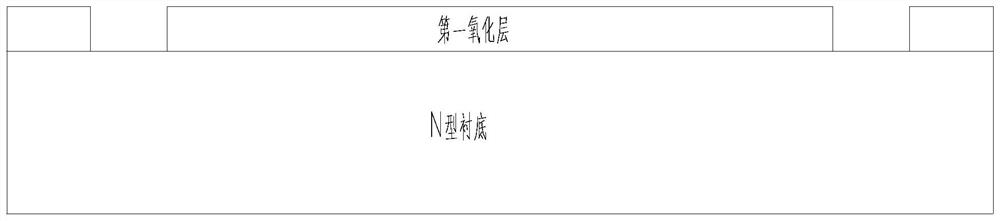

Manufacturing method of semiconductor

InactiveCN1725465AEliminate lattice defectsImprove refresh timeSemiconductor/solid-state device manufacturingLattice defectsInsulation layer

This invention puts forward a manufacturing method for semiconductor devices, especially DRAM, which adds an attached soft corrosion process to the source trap insulation layer after being corroded and takes a mixed gas of CE4 / O2 as the corroding gas under the microwave state with the frequency of 2.45GHz to eliminate the lattice defect caused by the harm of plasmas on a silicon substrate surface by the chemical reaction of corroding gas on the silicon substrate surface so as to ensure to constitute DRAM products with qualified electric property.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Positive grid and preparation method thereof

ActiveCN108933263AImprove conductivityHigh strengthElectrode carriers/collectorsElectrical conductorInternal resistance

The invention discloses a positive grid and a preparation method thereof. The positive grid comprises following components in percentage by weight: 1.0 to 2.0% of Sn, 0.04 to 0.09% of Ca, 0.002 to 0.004% of Al, 0.001 to 0.004% of Ag, 0.02 to 0.04% of Na, and the balance being Pb. The positive grid has the advantages that Sn and oxides of Sn and lead are good conductors, the conductivity of contactlayer is improved; Ca can enhance the strength of lead, the compatibility between Ag and lead is good, the corrosion resistant performance of alloy is enhanced; Na can remove harmful substances suchas Cu, Sb, and the like in the alloy; the density of Al is low, Al is distributed on the upper layer of the alloy and protects other main components from being burned; a demoulding agent effectively strengthens the bonding force between the grid and lead paste; the grid defects are eliminated through high temperature age hardening, the grid strength is enhanced, at the same time, the grid grains are refined, the corrosion resistant performance and creep resistant performance are both strengthened, a battery prepared from the positive grid has the advantages of little internal resistance and long deep cycle life, and the capacity fade in the primary period is avoided.

Owner:江苏海宝电池科技有限公司

Forming method of PMOS (P-channel metal oxide semiconductor) transistor

InactiveCN104681436AImprove mobilityImprove performanceSemiconductor/solid-state device manufacturingCharge carrier mobilityDielectric layer

The invention provides a forming method of a PMOS (P-channel metal oxide semiconductor) transistor. The method comprises the following steps that a semiconductor substrate is provided; a pseudo grid dielectric material layer and a pseudo grid electrode positioned on the surface of the pseudo grid dielectric layer are formed on the semiconductor substrate, and the pseudo grid electrode covers the partial pseudo grid dielectric material layer; a dielectric layer is formed on the semiconductor substrate, the surface of the dielectric layer is flush with the surface of the pseudo grid electrode, the pseudo grid electrode and a partial pseudo grid dielectric layer positioned under the pseudo grid electrode are removed, and a first groove is formed; the bottom of the first groove is subjected to plasma injection for forming an injection region, and the migration rate of carriers can be enhanced through plasmas; the injection region is subjected to recrystallization processing, and the defects in the injection region are eliminated, so that the injection region can become a channel region; a grid electrode structure is formed in the first groove, and the grid electrode structure comprises a grid dielectric layer positioned at the surface of the inner wall of the first groove and a grid electrode positioned on the surface of the grid dielectric layer. When the method is adopted, the migration rate of the carriers of the PMOS transistor can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for prolonging endurance life of diamond compact and diamond compact

The invention relates to the technical field of super-hard composite materials, in particular to a method for prolonging the endurance life of a diamond compact and the diamond compact. The method forprolonging the endurance life of the diamond compact includes the steps: irradiating an interface between a substrate and a diamond layer and the surface of the diamond layer by ultra-fast pulse laser beams; polishing the surface of the diamond layer. The diamond compact is manufactured by the ultra-fast pulse laser beams, a gradient transition layer is generated between layers, so that the substrate and the diamond layer are firmly combined, and sudden change of a thermal quantity and a mechanical quantity on the interlayer interface is avoided. The surface (cold annealing) of the diamond layer is irradiated by the ultra-fast pulse laser beams, thermal stress concentration and lattice defects of the diamond layer can be eliminated, D-D bonds on the surface of the diamond layer can be firmly bonded, cobalt atoms are 'extruded' to the surface of the diamond layer, a rich cobalt layer is removed by polishing, ultra-high surface smoothness is realized, the high-temperature resistance ofthe diamond compact is improved, and the service life of the diamond compact is prolonged.

Owner:上海梁为科技发展有限公司

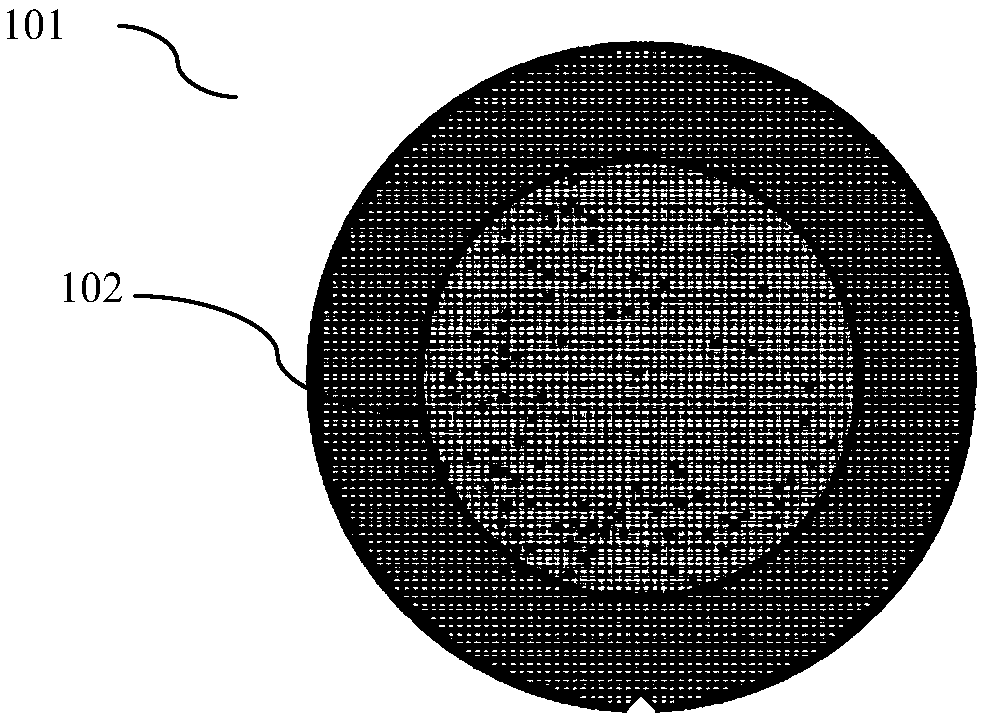

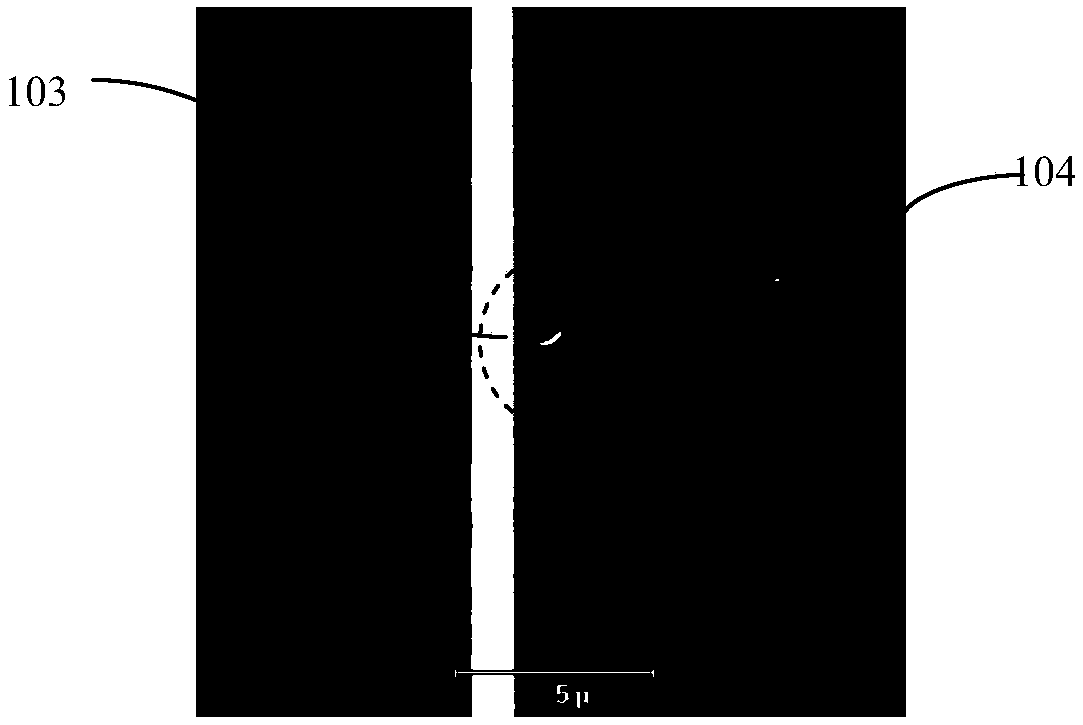

Crystallization of amorphous silicon film as well as manufacture method and device of poly-silicon film

InactiveCN101894747BHigh electron mobilityEliminate lattice defectsSemiconductor/solid-state device manufacturingAtmospheric airHigh energy

The invention relates to the crystallization of amorphous silicon films as well as manufacture method and device of poly-silicon films. In the method, electron beams of high energy density are used to act on amorphous silicon films to control the electron beams to accelerate anode voltage and beam flow so that amorphous silicon melt layers and glass base plates keep in extremely high temperature gradient. After the electron beams are stopped, the amorphous silicon melt layers are gradually cooled and crystallized. The device mainly comprises an electron-optical system, a computer control system, a workpiece chamber and a workpiece control table placed in the workpice chamber. A cathode is placed in a negative high voltage end, amorphous silicon is grounded, the electron beams scan line byline, the repetition rate on scanning the last line and the next line by the electron beams can reach above 99%, the electron beams are cut off after one round is scanned, the workpiece control tableis moved for the next round of scanning, and the process is thus repeated. The workpiece chamber can be a vacuum chamber or is in an atmosphere condition or a certain atmosphere. If in the atmosphereor inert gas environment, an electron beam leading window is arranged between the workpiece chamber and the electron-optical system.

Owner:SHENZHEN DANBANG INVESTMENT GROUP

Physical vapor deposition device and method

InactiveCN108018536ASmall temperature differenceEliminate lattice defectsVacuum evaporation coatingSputtering coatingEngineeringDeposition process

The invention discloses a physical vapor deposition device. The physical vapor deposition device is characterized in that a vapor deposition process chamber comprises a wafer base, wherein a cooling water channel for controlling wafer cooling is arranged in the wafer base and divided into a plurality of independent circulating areas; each independent circulating area is used for correspondingly cooling the rear surface, in the corresponding area, of the wafer; the cooling rate of each independent circulating area is independently adjusted, so that the cooling rate of each area is kept consistent when the wafer is in the working process, and the temperature difference between the areas can be reduced when the wafer is in the working process, and moreover, the temperature difference is reduced to reach the level that metal lattice defects are not caused. The invention also discloses a physical vapor deposition method. With the adoption of the device and the method, the temperature difference among the areas can be controlled when the wafer is in the working process, and the temperature difference is reduced, so that the metal lattice defects caused by the temperature difference occurring in the working process of the wafer can be removed, and as a result, the product yield is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

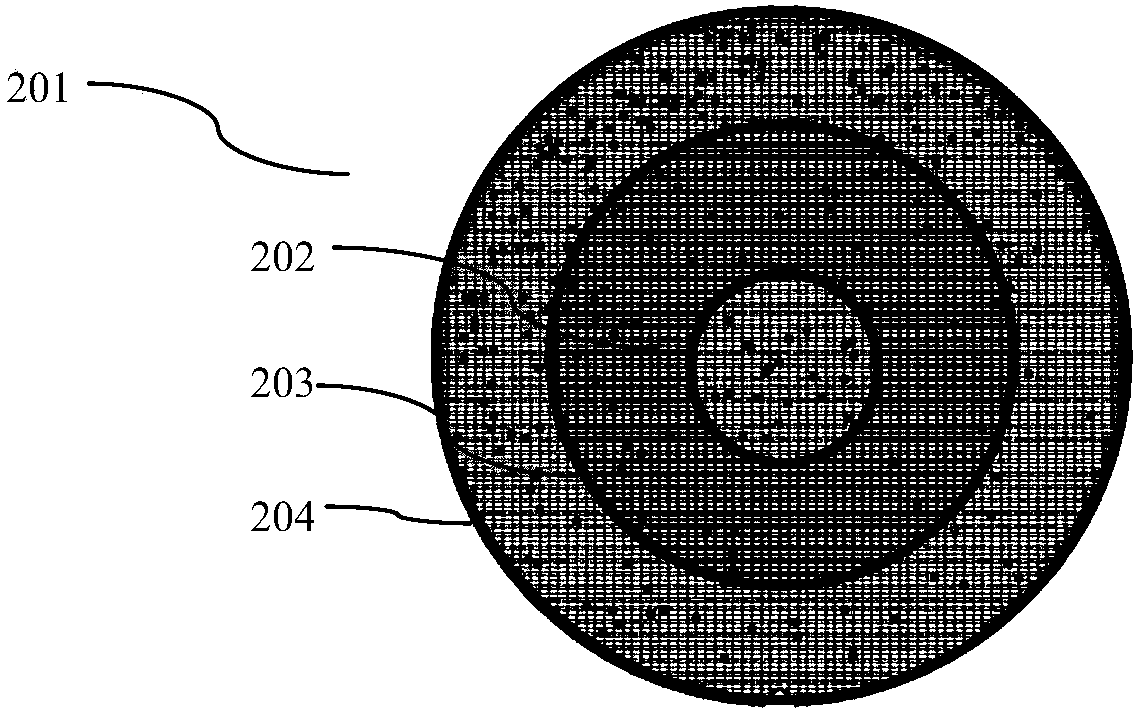

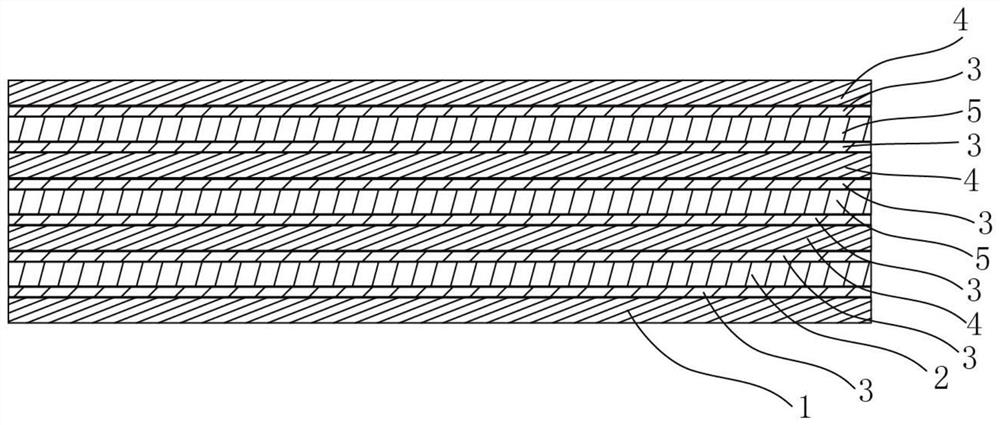

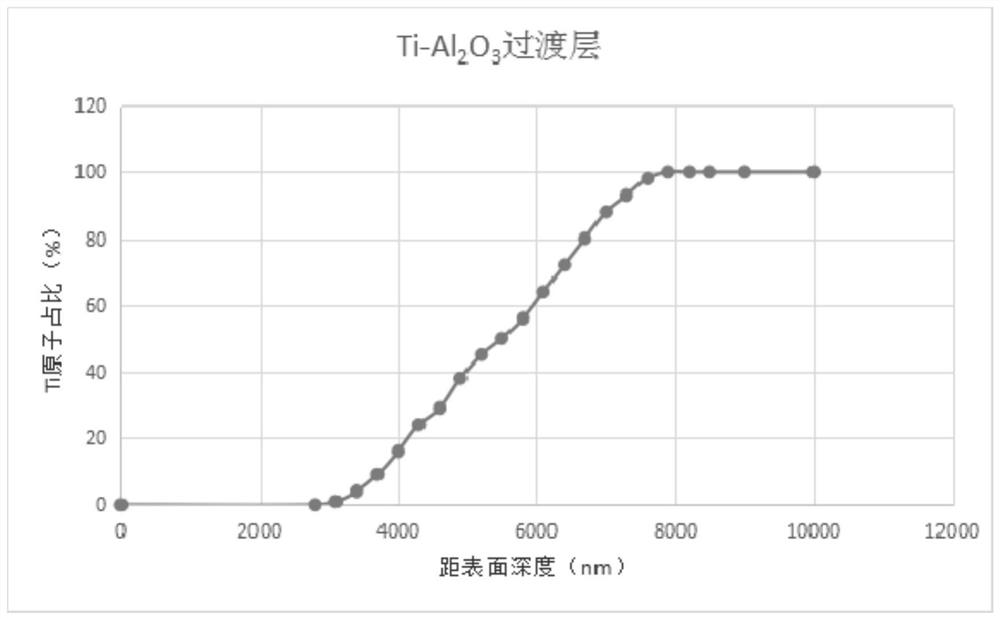

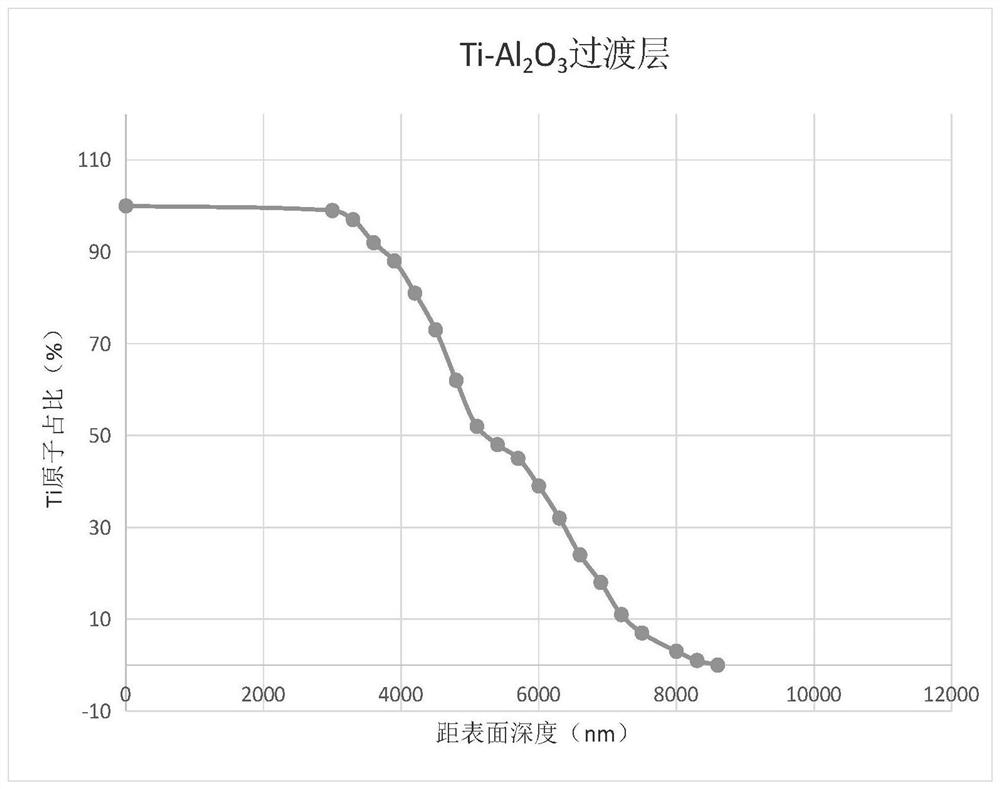

Ti/X metal ceramic with laminated structure and preparation method of Ti/X metal ceramic

ActiveCN112077320AImprove ductilityImprove heat resistanceAdditive manufacturing apparatusIncreasing energy efficiencyChemical compatibilityTitanium

The invention provides Ti / X metal ceramic with a laminated structure and a preparation method of the Ti / X metal ceramic. The Ti / X metal ceramic with the laminated structure sequentially comprises a Tilayer, a Ti-X transition layer, an X layer, a Ti-X transition layer, a Ti layer... a Ti-X transition layer, an X layer, a Ti-X transition layer and a Ti layer from bottom to top. The Ti / X metal ceramic with the laminated structure has the characteristics of toughness of titanium, hardness of an X nano material and the like, and has good ductility, heat resistance, wear resistance and impact resistance. According to the Ti / X metal ceramic with the laminated structure and the preparation method of the Ti / X metal ceramic, printing is carried out layer by layer through 3D printing equipment according to the stacking sequence of the Ti layer-X layer-Ti layer-X layer-Ti layer, an interface between the Ti layers and the X layers is subjected to rapid cold processing treatment through ultra-strong pulse energy beams or particle beams, and the Ti-X transition layers combining the Ti layers and the X layers are formed; and the problems of poor chemical compatibility and wettability of a titanium nano material and the X nano material can be solved, compounding of the Ti nano material and the X nano material can be well achieved, and then the Ti / X metal ceramic which is high in interface bonding and has the laminated structure is formed.

Owner:上海梁为科技发展有限公司

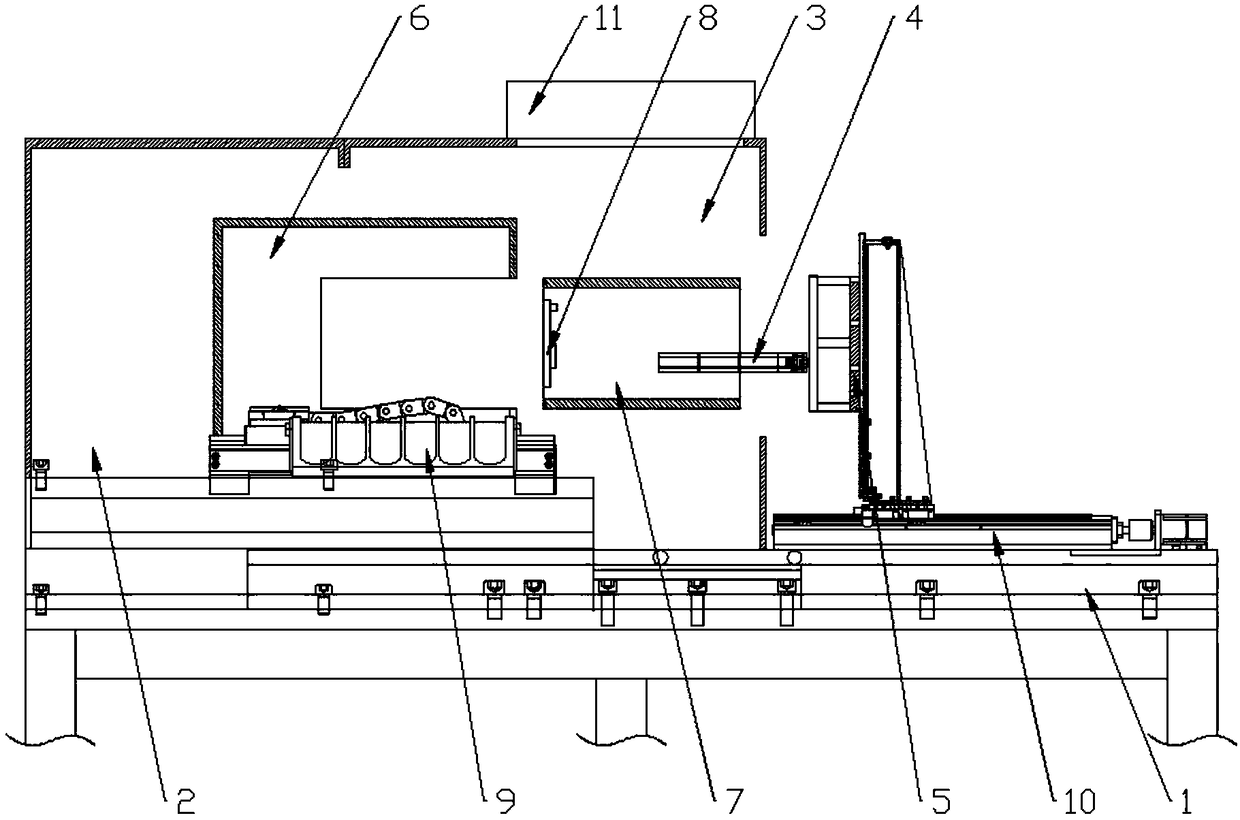

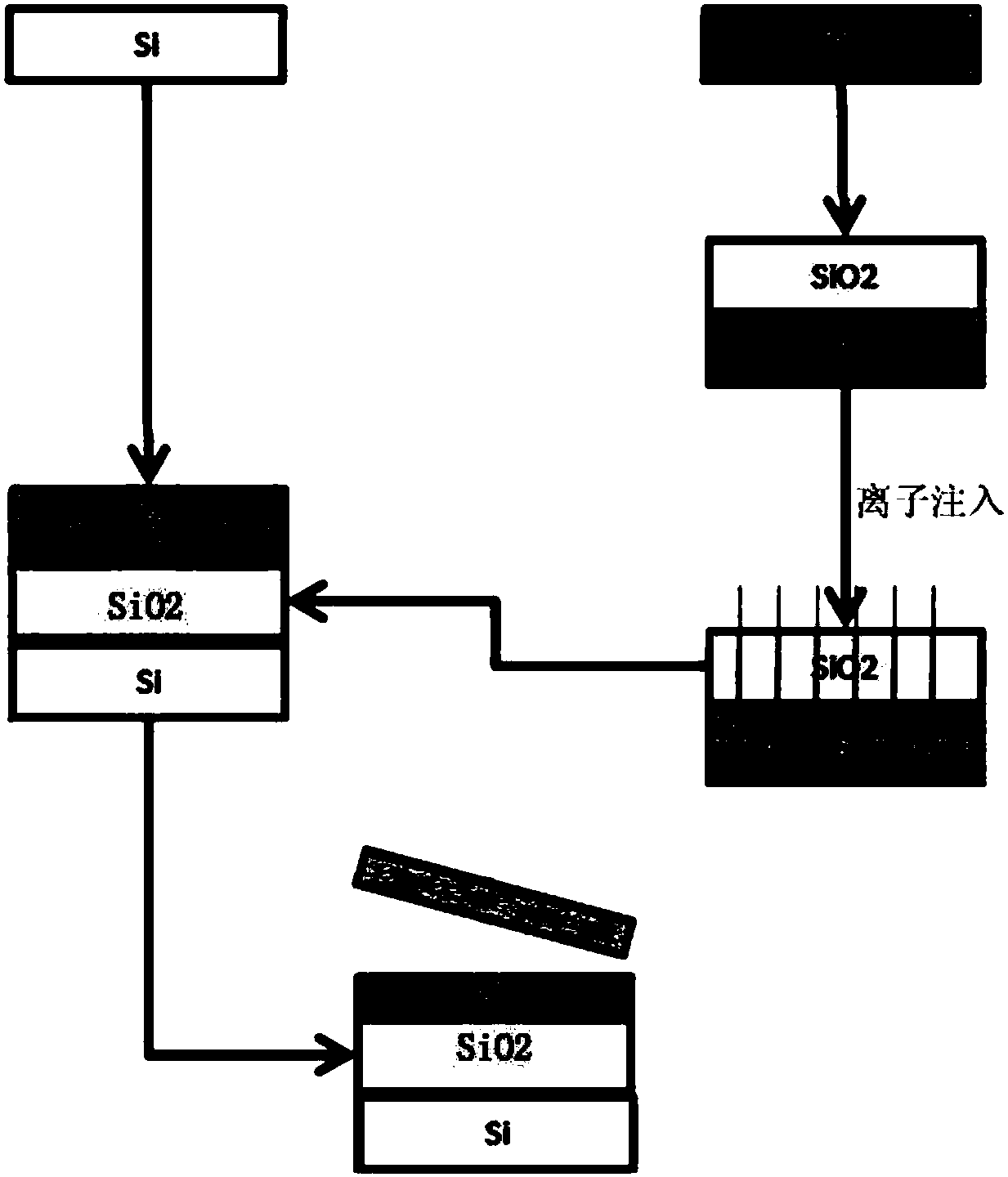

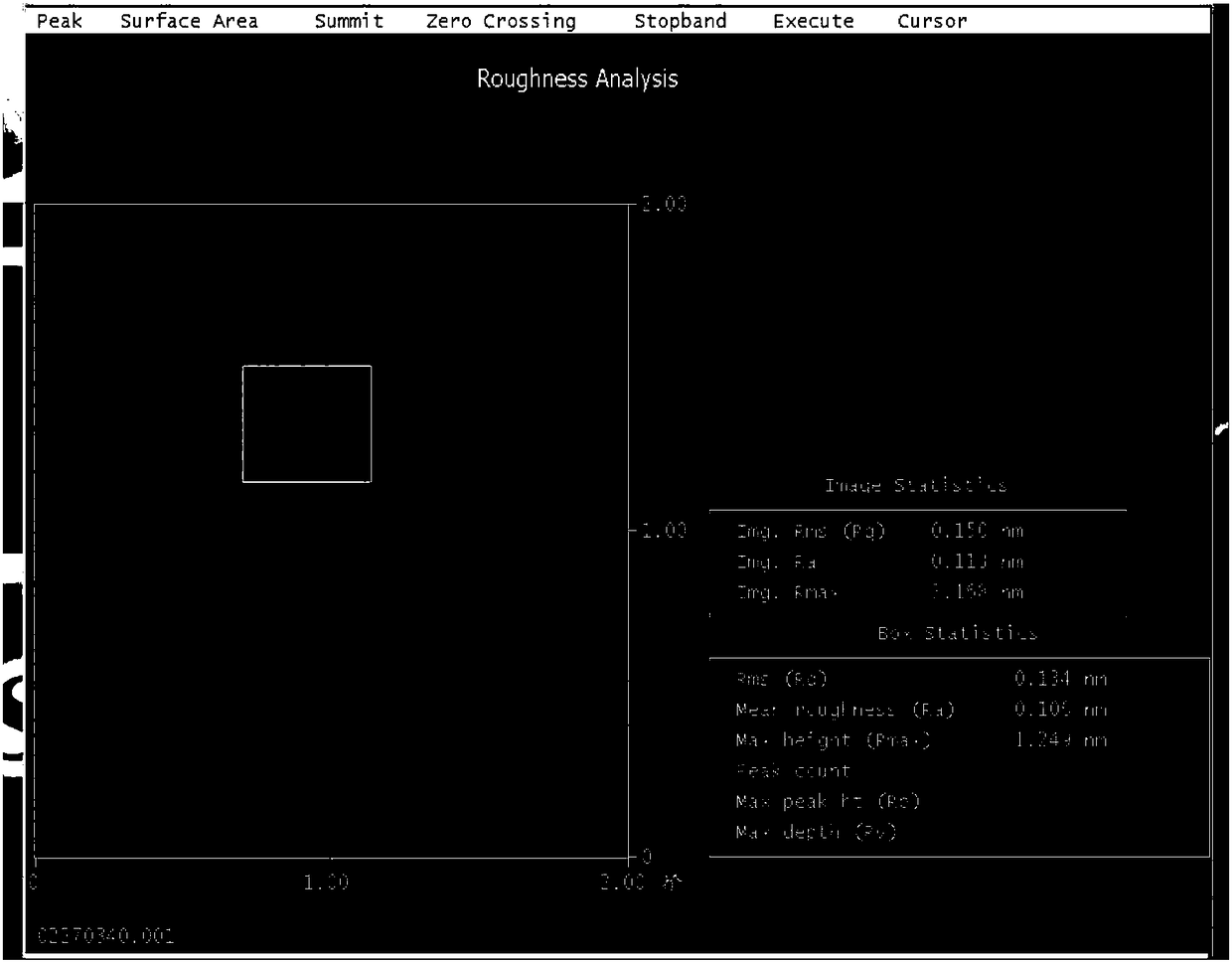

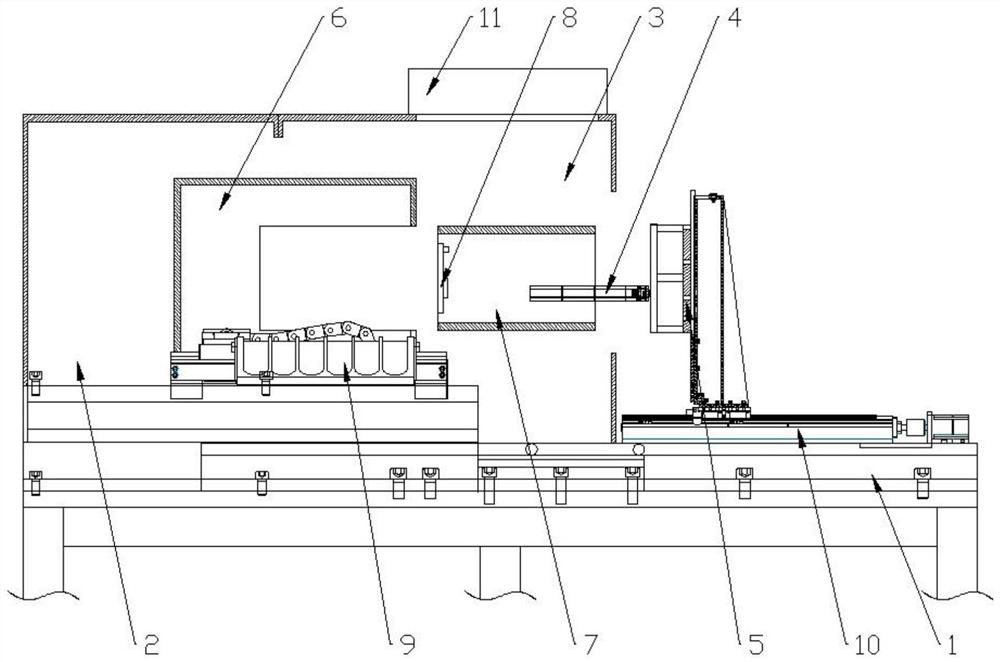

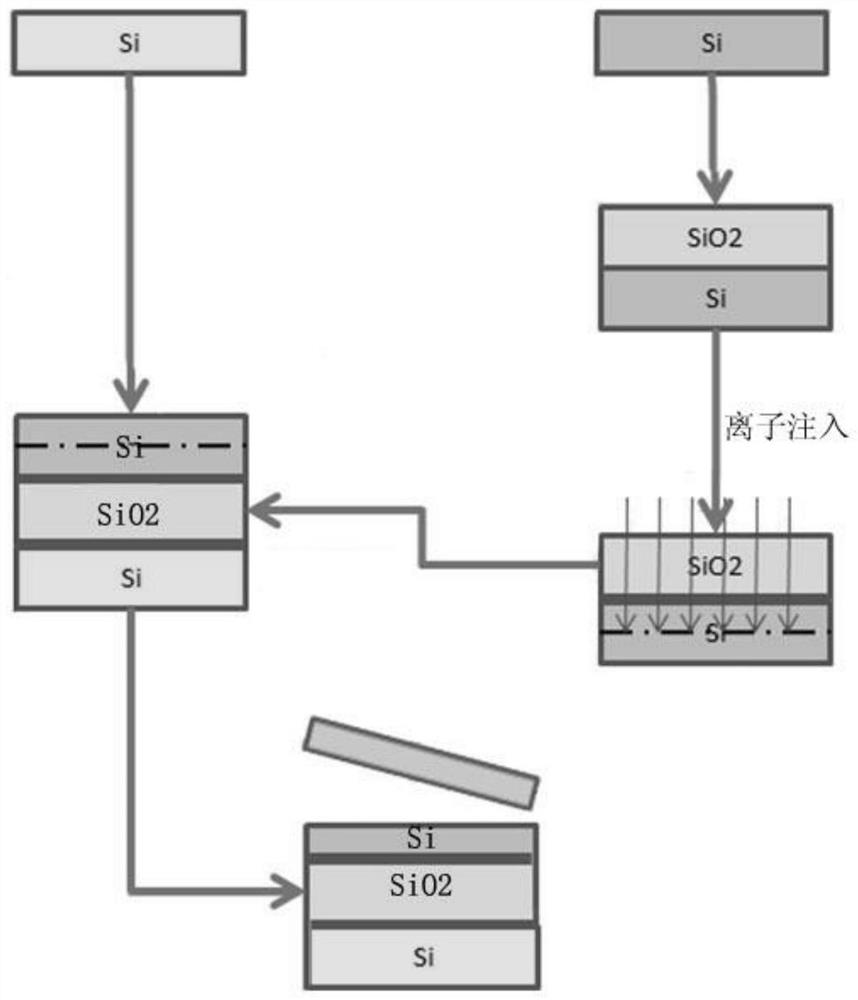

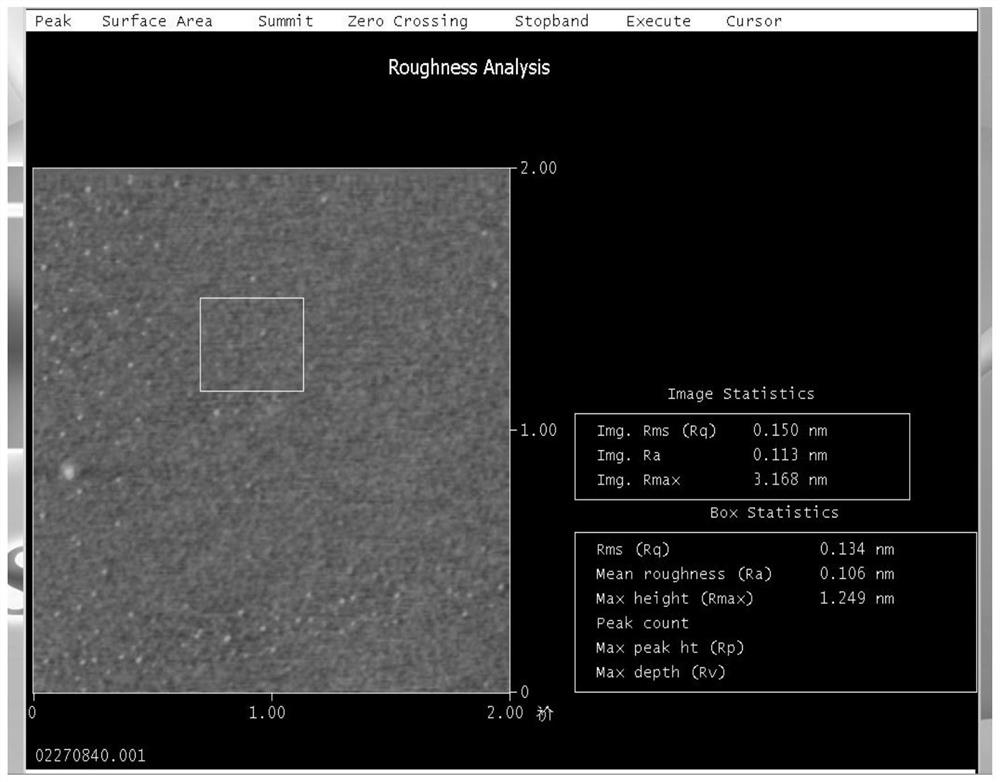

A machine for preparing SOI silicon wafers by laser fragmentation technology

ActiveCN109148317AEliminate lattice defectsRemove inclusionsSemiconductor/solid-state device manufacturingEngineeringHydrogen ion

A machine for preparing SOI silicon wafers by laser fragmentation technology comprises a base, wherein a split box, a heating box and a crystal disk are arranged on the base in sequence from left to right, the crystal disk is fixed on the feeding disk, an insulating tube is installed in the heating box, a furnace tube is sleeved in the insulating tube, a laser emitting head is fixed at the left end of the furnace tube, and a cooling device is installed at the top end of the heating box. The machine has the advantages that by using the laser heating method for fragmentation, the crystal latticedefect caused by hydrogen ion implantation layer can be eliminated, the metal inclusion can be eliminated, the surface adsorption substance can be removed, the surface roughness can be improved, andthe production efficiency can be high.

Owner:SHENYANG SILICON TECH

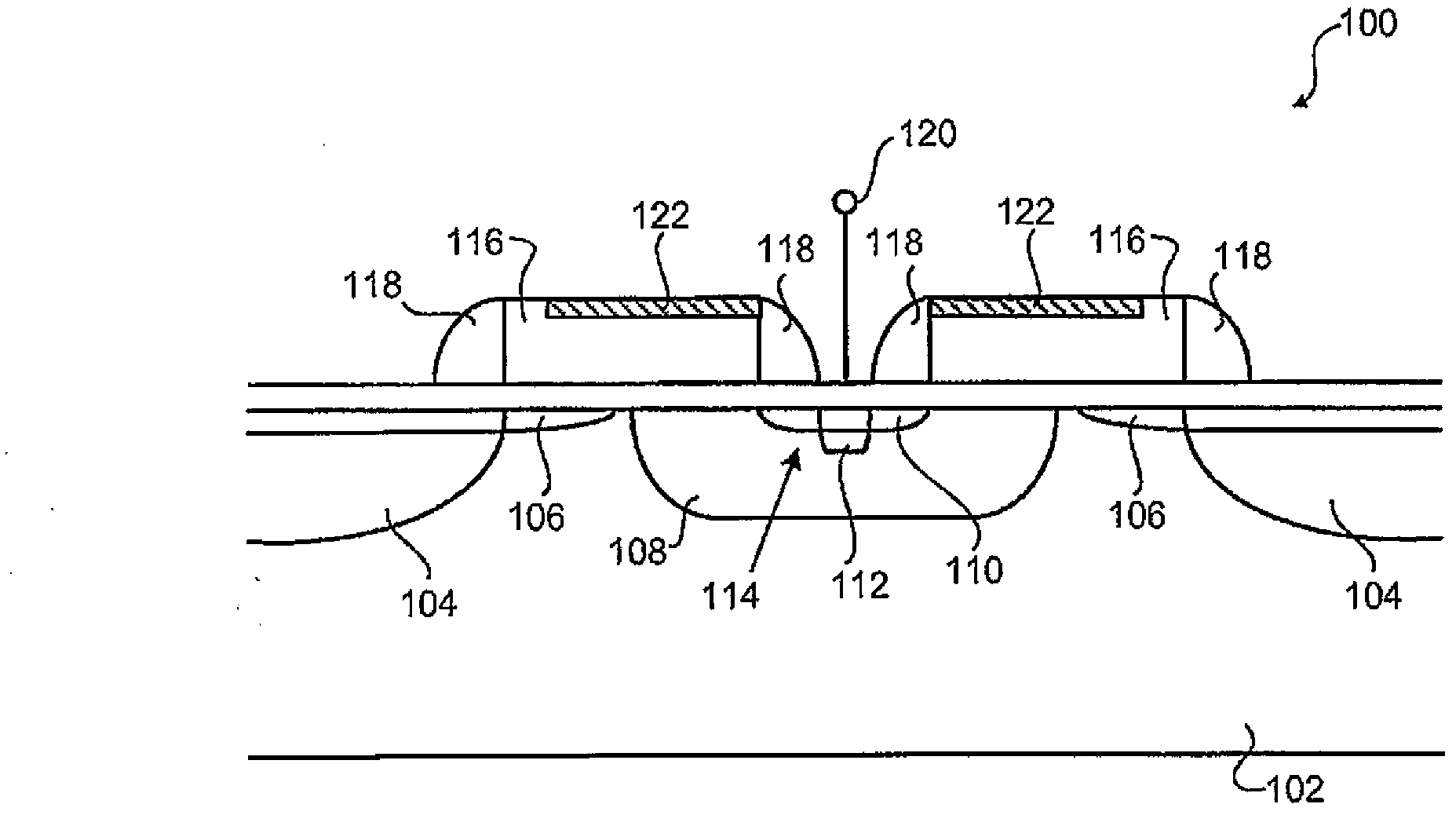

Image sensor with doped transfer gate

ActiveCN102906876AImprove conversion gainIncreased sensitivityTransistorSolid-state devicesDopantPhotodetector

An image sensor includes an array of pixels, with at least one pixel including a photodetector formed in a substrate layer and a transfer gate disposed adjacent to the photodetector. The substrate layer further includes multiple charge-to-voltage conversion regions. A single photodetector can transfer collected charge to a single charge-to-voltage conversion region, or alternatively multiple photodetectors can transfer collected charge to a common charge-to- voltage conversion region shared by the photodetectors. An implant region formed when dopants are implanted into the substrate layer to form source / drain implant regions is disposed in only a portion of each transfer gate while each charge-to-voltage conversion region is substantially devoid of the implant region.

Owner:OMNIVISION TECH INC

Method for removing lattice defect in pad area of semiconductor device

InactiveCN100347836CEliminate lattice defectsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingLattice defectsOrganic solvent

This invention discloses a method for removing lattice defect in the pad zone, after forming an Al alloy purification layer and before forming a polyimide protection layer on the pad, it is tested that if the lattice defect exists in the pad, if so, the organic solvent of EKC and ACT cleaning process is made to remove the lattice defect in the zone.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for removing lattice defect in pad area of semiconductor device

InactiveCN100362638CEliminate lattice defectsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingLattice defectsProtection layer

This invention discloses a method for removing lattice defect in the pad zone of a semiconductor device with Ar plasma sputter reparation which forms a polyimide protection layer then tests if lattice defect exists in the pad zone, if so, the Ar plasma sputter is made to repair and remove the lattice defect.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

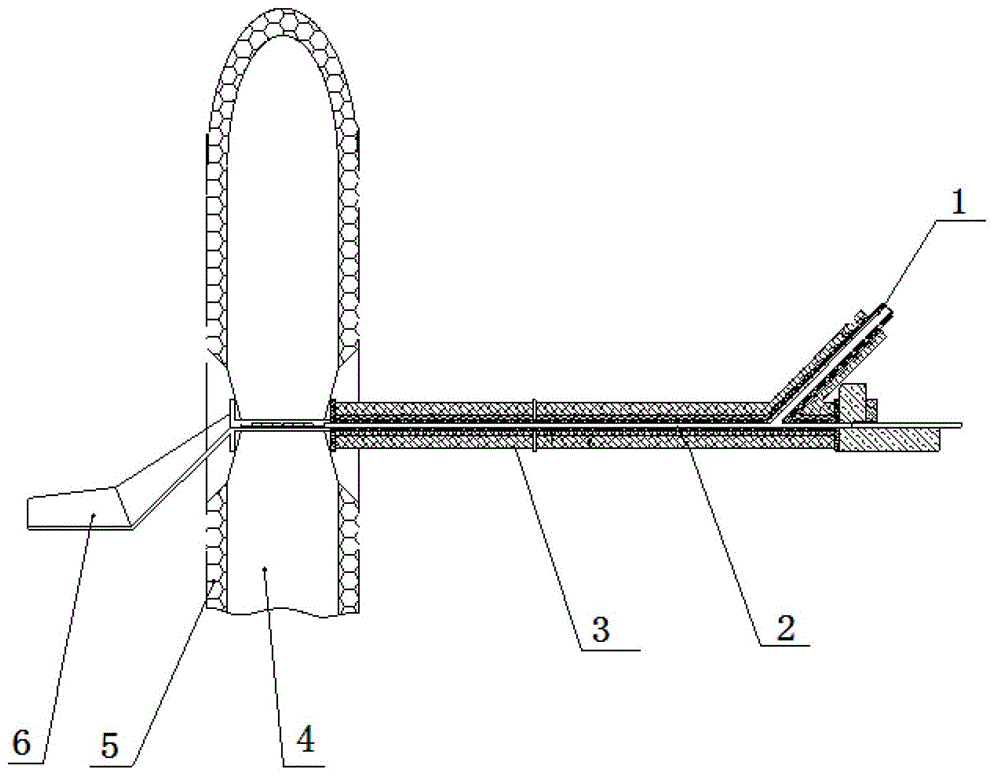

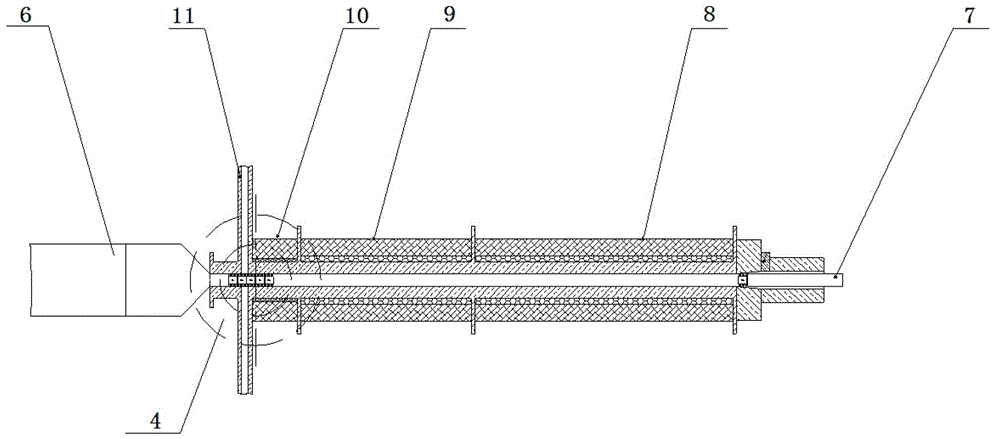

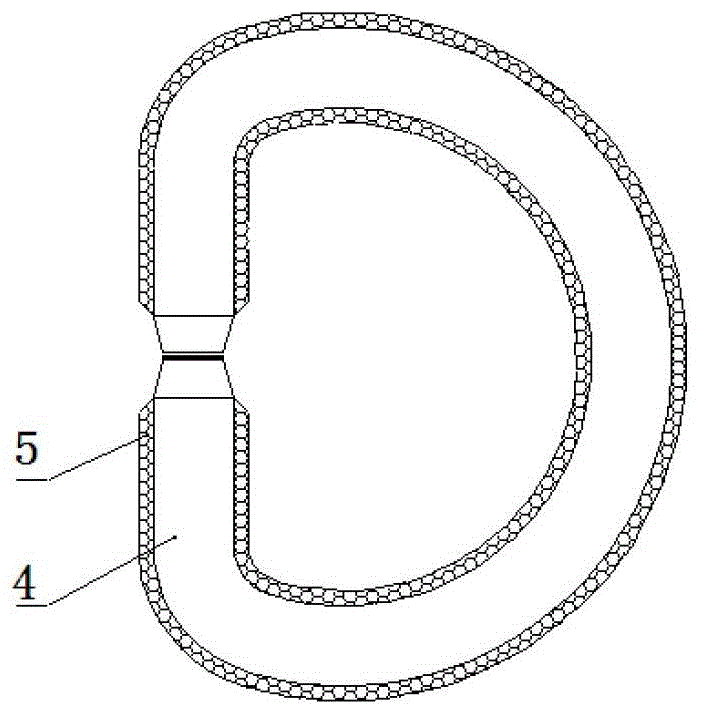

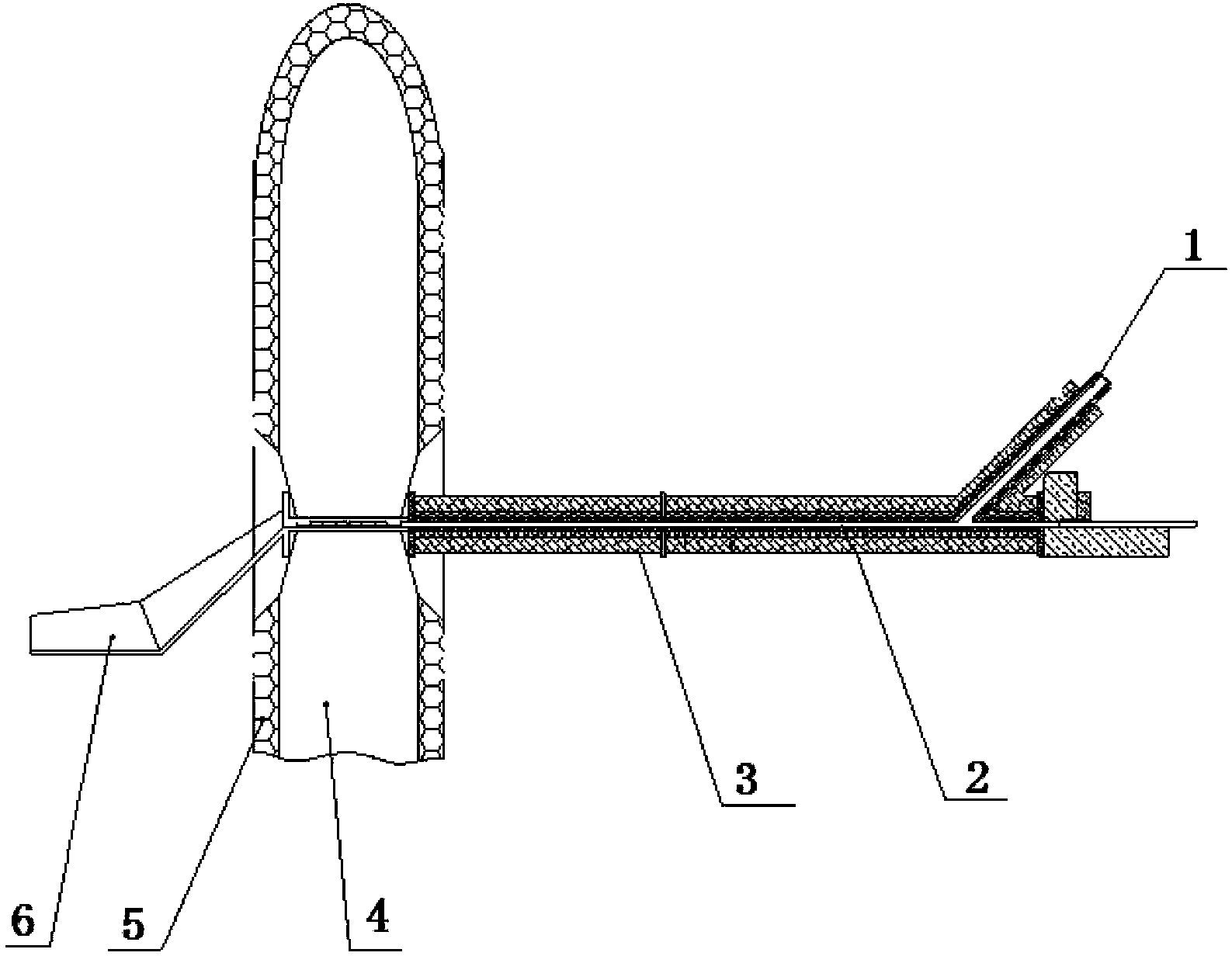

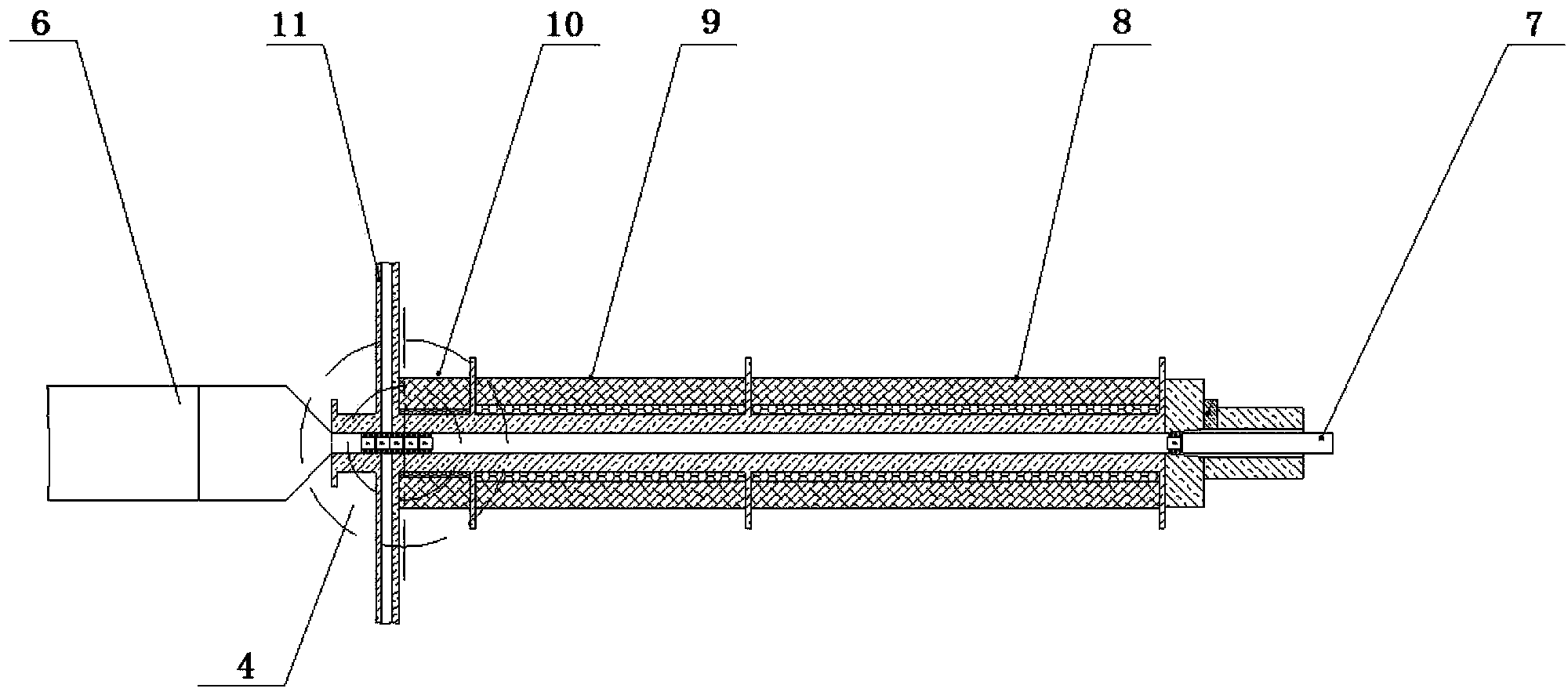

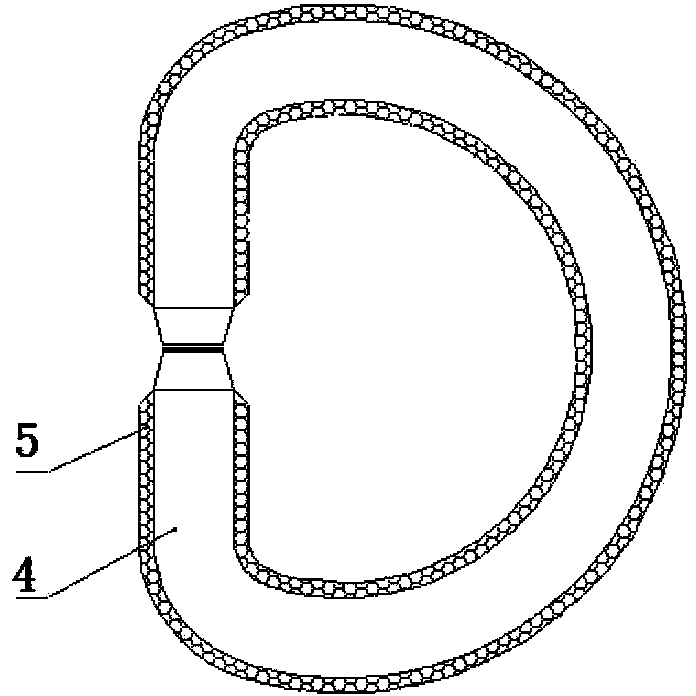

Thermomagnetic treatment device and method for magneto-resistive elements of spin valves

InactiveCN102943153AImprove stabilityHigh sensitivityFurnace typesHeat treatment furnacesSoft magnetMagnetic reluctance

The invention relates to a thermomagnetic treatment device and method for magneto-resistive elements of spin valves. The thermomagnetic treatment device comprises an element guiding device, a heater, a D-shaped soft magnet, an annular magnetic field coil and a collector. The method comprises the following steps that: the magneto-resistive elements of the spin valves are pushed into a preheating region and then sequentially passes through a high-temperature heating region and a high-temperature stabilizing region to be heated; then the elements enter a horizontal clearance in the middle part of the straight flange of the D-shaped soft magnet to be subjected to low-frequency strong-magnetism processing; and along with the continuous pushing of the elements, the processed elements continuously slip into the element collector. According to the method, the lattice imperfection of a shielding material layer of each magneto-resistive element can be eliminated, and the discrete region, which corresponds to the original point of a coordinate system of output of a magnetic field, of the geometric center of a magnetic-lag region as well as the discreteness of differential permeability is reduced, and thus the stability and sensitivity of the elements are improved.

Owner:710TH RES INST OF CHINA SHIPBUILDING IND CORP

Method for forming solder pad of semiconductor device

InactiveCN100468676CEliminate lattice defectsPrevent electrochemical corrosionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOrganic solventLattice defects

A bonding pad forming method for semiconductor device comprises that: a current conducting layer is formed on a substrate of a semiconductor device; a bonding pad graph is etched on the current conducting layer; lattice defect detection is executed to the surface of the current conducting layer; diluted sulfur peroxide is utilized to process the lattice defects of the current conducting layer surface to form a bonding pad. The use of diluted sulfur peroxide which is a water-containing solution can remove the lattice defects of the bonding pad surface and simultaneously reduce the processing time of organic solvents, so as to improve productivity.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A positive electrode grid and its preparation method

ActiveCN108933263BImprove conductivityHigh strengthElectrode carriers/collectorsElectrical conductorElectrical battery

The invention discloses a positive electrode grid and a preparation method thereof. Ag, 0.02‑0.04% Na, balance Pb. The advantages of the present invention are: Sn and its oxide formed with lead are good conductors, which can improve the conductivity of the contact layer; Ca can increase the strength of lead, and Ag and lead have better phase solubility, which can improve the corrosion resistance of the alloy Na can remove harmful impurities such as Cu and Sb in the alloy; Al has a low density and is distributed on the upper layer of the alloy, which can effectively protect other main components and avoid burning; the release agent can effectively improve the bonding force between the grid and the lead paste; high temperature Age hardening can eliminate lattice defects, improve the strength of the grid, and at the same time refine the grid grains, improve corrosion resistance and creep resistance; the battery prepared with it has small internal resistance and long deep cycle life, effectively avoiding solve the problem of initial capacity fading.

Owner:江苏海宝电池科技有限公司

Thermomagnetic treatment device and method for magneto-resistive elements of spin valves

InactiveCN102943153BImprove stabilityHigh sensitivityFurnace typesHeat treatment furnacesSoft magnetSpins

The invention relates to a thermomagnetic treatment device and method for magneto-resistive elements of spin valves. The thermomagnetic treatment device comprises an element guiding device, a heater, a D-shaped soft magnet, an annular magnetic field coil and a collector. The method comprises the following steps that: the magneto-resistive elements of the spin valves are pushed into a preheating region and then sequentially passes through a high-temperature heating region and a high-temperature stabilizing region to be heated; then the elements enter a horizontal clearance in the middle part of the straight flange of the D-shaped soft magnet to be subjected to low-frequency strong-magnetism processing; and along with the continuous pushing of the elements, the processed elements continuously slip into the element collector. According to the method, the lattice imperfection of a shielding material layer of each magneto-resistive element can be eliminated, and the discrete region, which corresponds to the original point of a coordinate system of output of a magnetic field, of the geometric center of a magnetic-lag region as well as the discreteness of differential permeability is reduced, and thus the stability and sensitivity of the elements are improved.

Owner:710TH RES INST OF CHINA SHIPBUILDING IND CORP

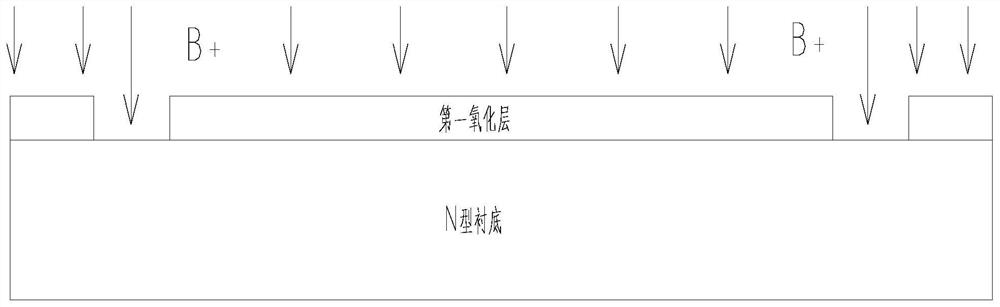

Method for improving ESD failure of protection ring region of planar Schottky product

ActiveCN112635304AIncrease the radius of curvatureImprove antistatic performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical field strengthPhysical chemistry

The invention discloses a method for improving an ESD failure of a protection ring region of a planar Schottky product. The method relates to a semiconductor diffusion process. According to the method for improving the ESD failure of the protection ring region of the planar Schottky product, the electric field intensity of the protection ring region is dispersed, so that the anti-static capability of the protection ring region is improved. By increasing the junction depth of a protection ring and increasing the curvature radius of a depletion layer at the edge of the protection ring, the electric field intensity of the ring region is dispersed, so that the antistatic capacity of the protection ring region is improved, and the purpose of increasing the junction depth of the protection ring is achieved by optimizing the oxidation time and temperature of high-temperature diffusion. The method has the advantages of improving the anti-static capability of the protection ring region and the like.

Owner:YANGZHOU YANGJIE ELECTRONIC TECH CO LTD

Manufacturing method of semiconductor

InactiveCN100466218CEliminate lattice defectsImprove refresh timeSemiconductor/solid-state device manufacturingLattice defectsInsulation layer

This invention puts forward a manufacturing method for semiconductor devices, especially DRAM, which adds an attached soft corrosion process to the source trap insulation layer after being corroded and takes a mixed gas of CE4 / O2 as the corroding gas under the microwave state with the frequency of 2.45GHz to eliminate the lattice defect caused by the harm of plasmas on a silicon substrate surface by the chemical reaction of corroding gas on the silicon substrate surface so as to ensure to constitute DRAM products with qualified electric property.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A machine for preparing soi silicon wafers by laser splitting technology

ActiveCN109148317BEliminate lattice defectsRemove inclusionsSemiconductor/solid-state device manufacturingSusceptorPhysical chemistry

Owner:SHENYANG SILICON TECH

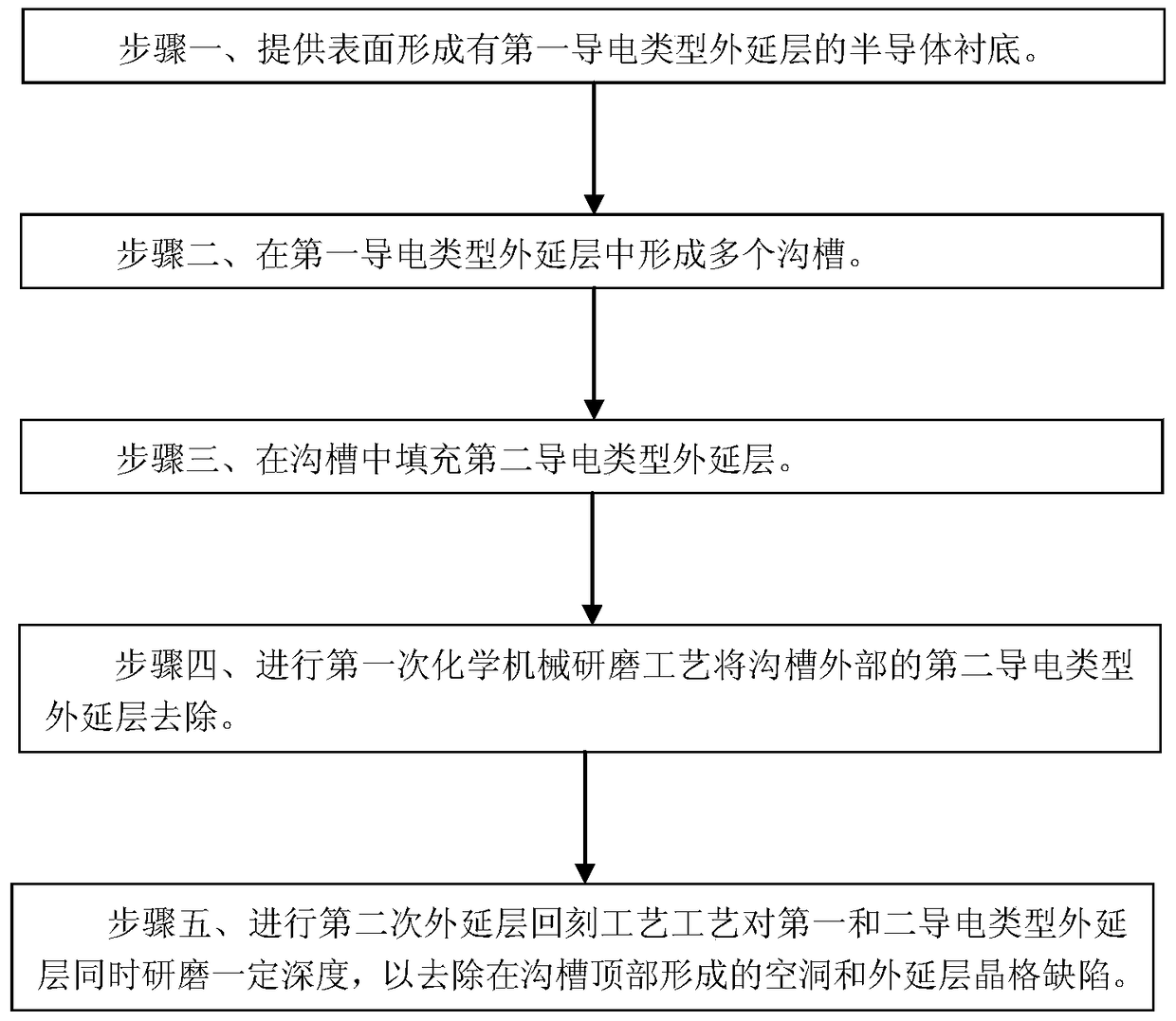

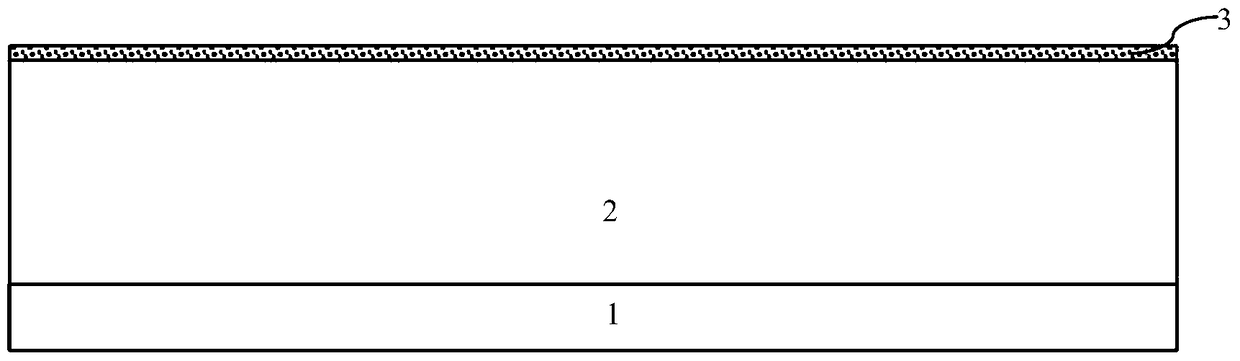

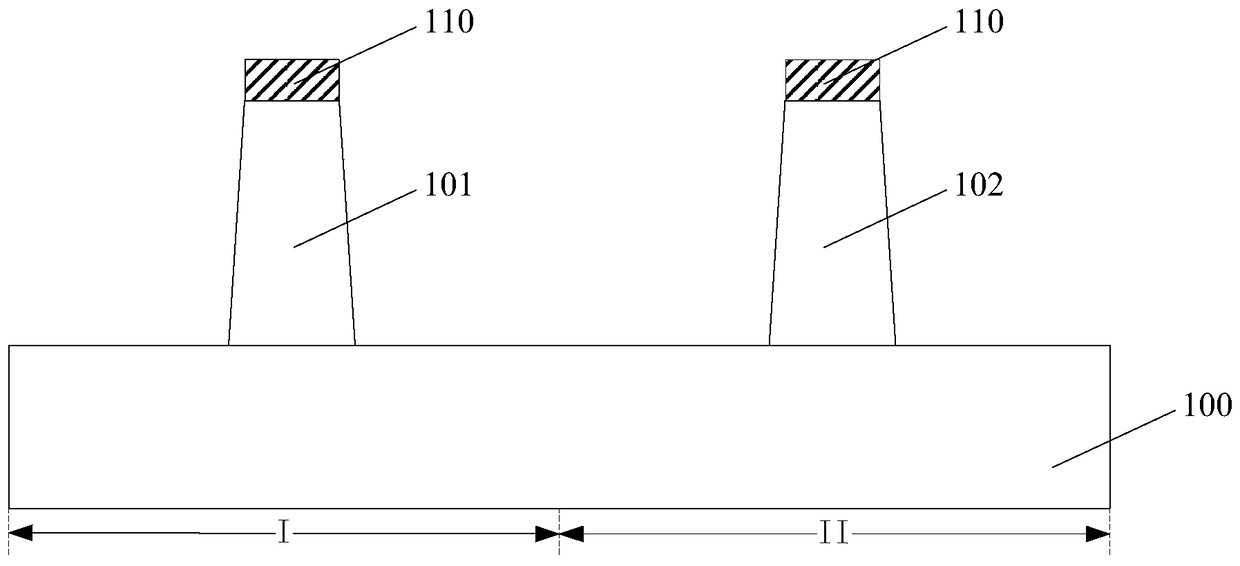

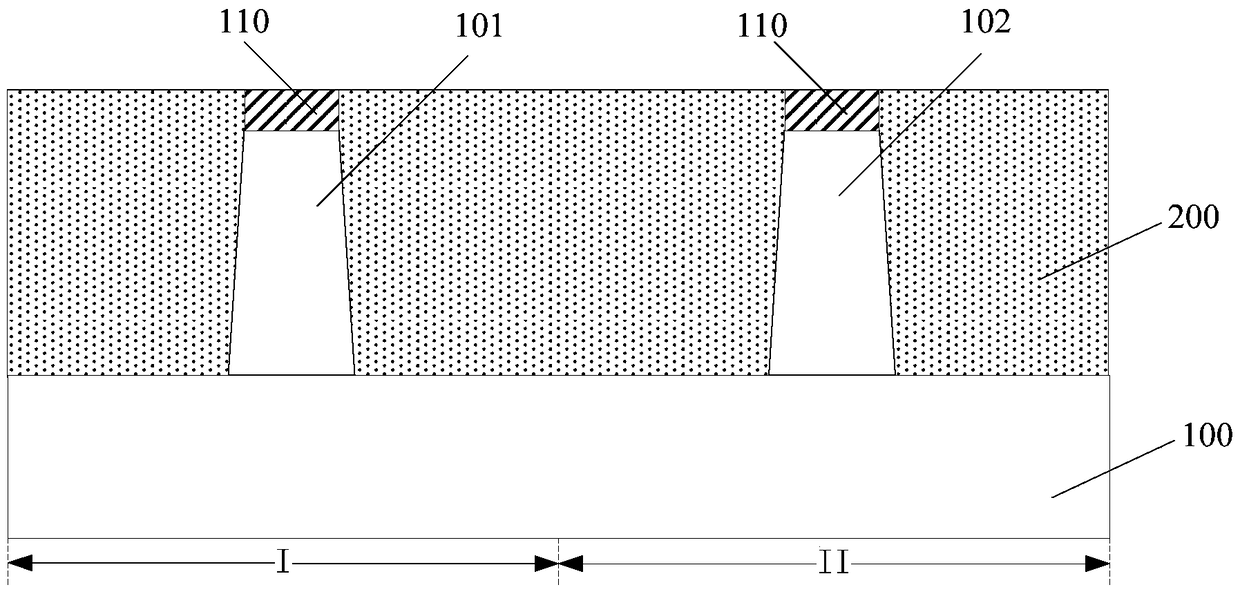

Trench-type super junction manufacturing method

ActiveCN105551966BImprove integrityImprove production yieldSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringReverse leakage current

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Fin field effect transistor and method of forming the same

ActiveCN105097511BImprove mobilityAvoid affecting electrical parametersSemiconductor/solid-state device manufacturingSemiconductor devicesField effectSingle crystal

The invention relates to a fin field effect transistor and a formation method thereof. The formation method of the fin field effect transistor comprises the steps of providing a semiconductor substrate; forming a first pin portion on the semiconductor substrate; forming an isolation material layer whose surface is flush with the top surface of the first fin portion on the semiconductor substrate; carrying out mobility enhancement ion implantation on the first fin portion, and forming an implantation region at the top end of the first fin portion; carrying out local recrystallization treatment on the implantation region, and enabling the implantation region to become a single crystal semiconductor layer containing implanted ions, wherein a hole mobility of the single crystal semiconductor layer is greater than the hole mobility of the first fin portion below the single crystal semiconductor layer; etching the isolation material layer, and forming an isolation layer whose surface is flush with the bottom surface of the single crystal semiconductor layer; and forming a first grid structure crossing the single crystal semiconductor layer. The method provided by the invention can improve the performance of the formed fin field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

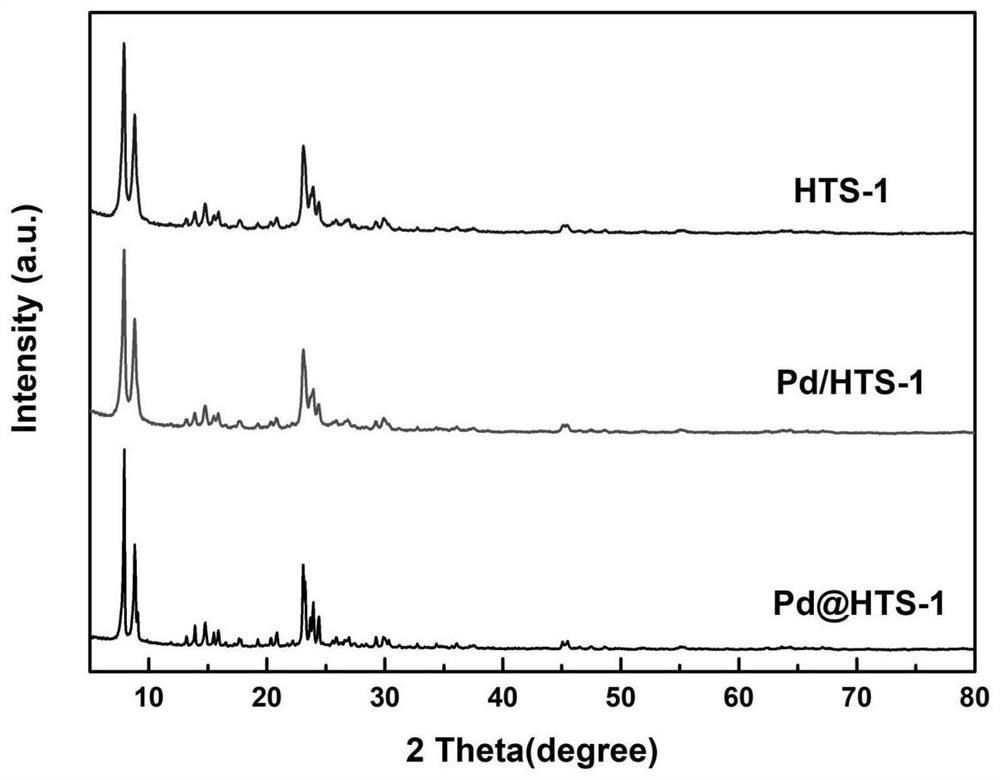

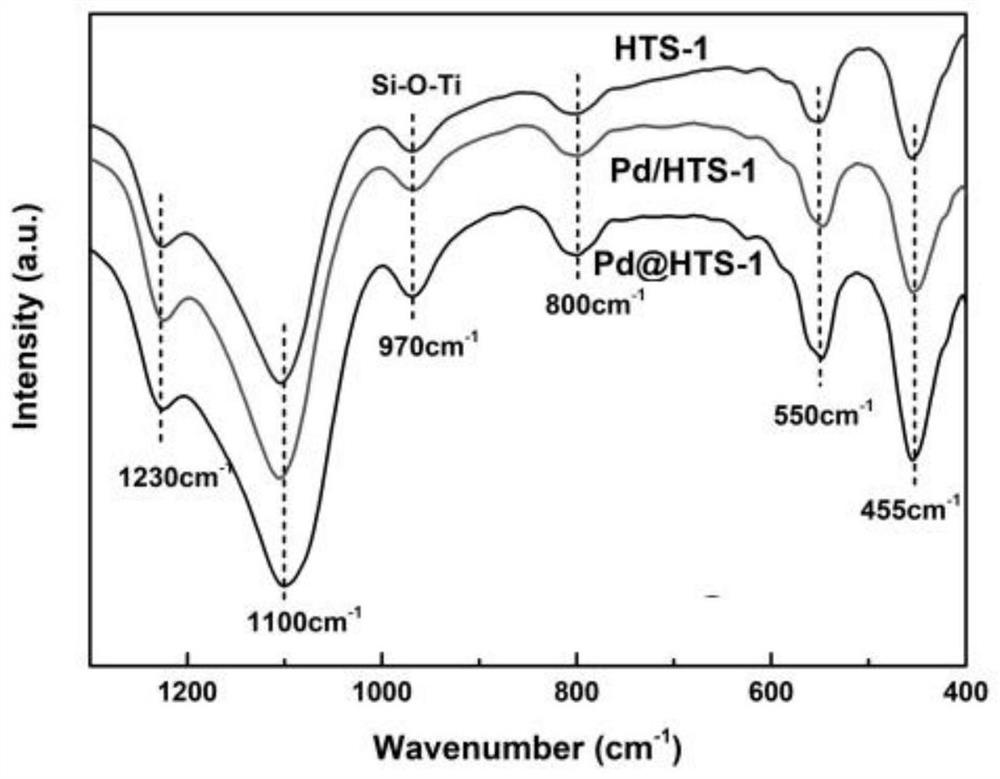

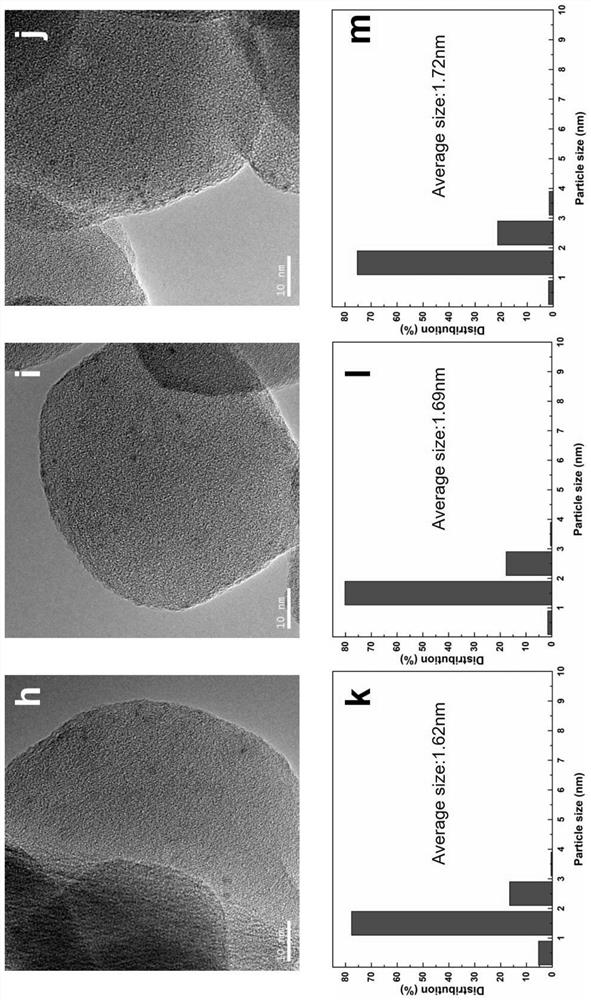

Encapsulated platinum-group subnano metal-supported porous titanium-silicon molecular sieve catalyst and its preparation and application

ActiveCN109999902BSmall sizeIncrease profitMolecular sieve catalystsPeroxides/peroxyhydrates/peroxyacids/superoxides/ozonidesPtru catalystMetal particle

The invention discloses an encapsulated platinum group subnano metal-loaded porous grade titanium-silicon molecular sieve catalyst and its preparation and application. The catalyst is that the subnano platinum group metal particles are evenly encapsulated in the pores of the porous grade HTS-1 molecular sieve, and the surface of the subnano platinum group metal particles has a metal oxide protective film; the platinum group metal is Pd, At least one of Pt, Ru, Au, in the catalyst, the silicon-titanium molar ratio of the porous grade HTS-1 molecular sieve is 20-2000, and the mass ratio of the subnanometer platinum group metal particles to the porous grade HTS-1 molecular sieve is 1 :100‑1:1000. The catalyst provided by the invention has strong sintering resistance, small metal size and uniform distribution, high metal utilization rate and eliminates lattice defects on the surface of metal particles. The invention provides the application of the encapsulated subnanometer platinum group metal particle-loaded porous titanium-silicon molecular sieve catalyst in the direct synthesis of hydrogen peroxide from hydrogen and oxygen, which can significantly increase the yield of hydrogen peroxide and realize the efficient utilization of precious metals , saving economic costs.

Owner:ZHEJIANG UNIV OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com