Fin field effect transistor and method of forming the same

A fin field effect and transistor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of low saturation current and low mobility of PMOS transistors, and improve hole carrier mobility. , high mobility, and the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

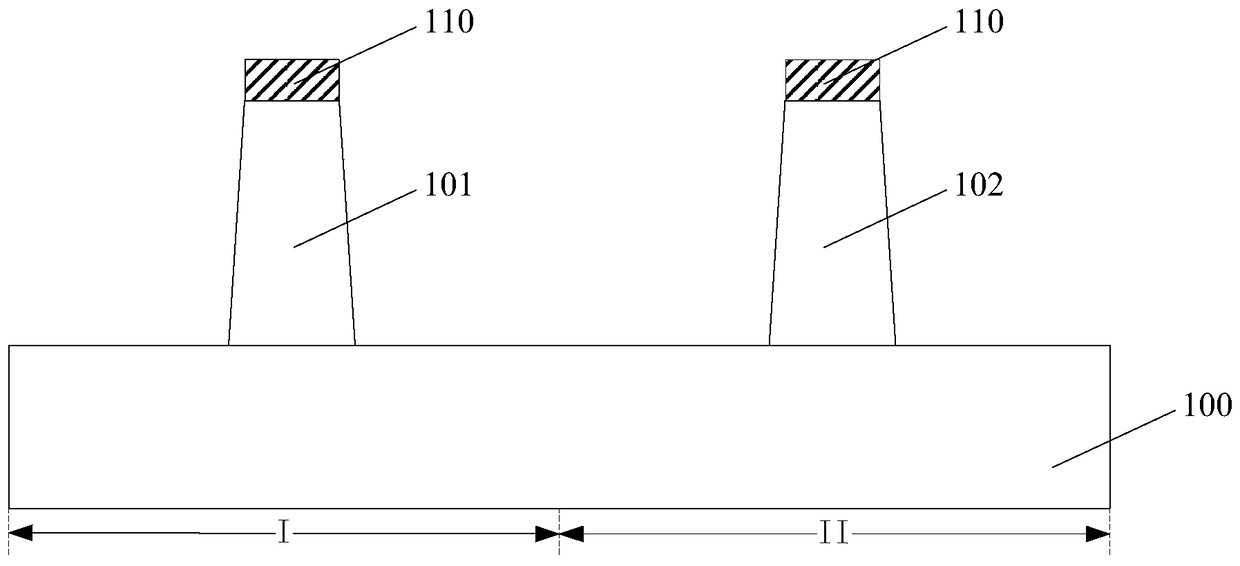

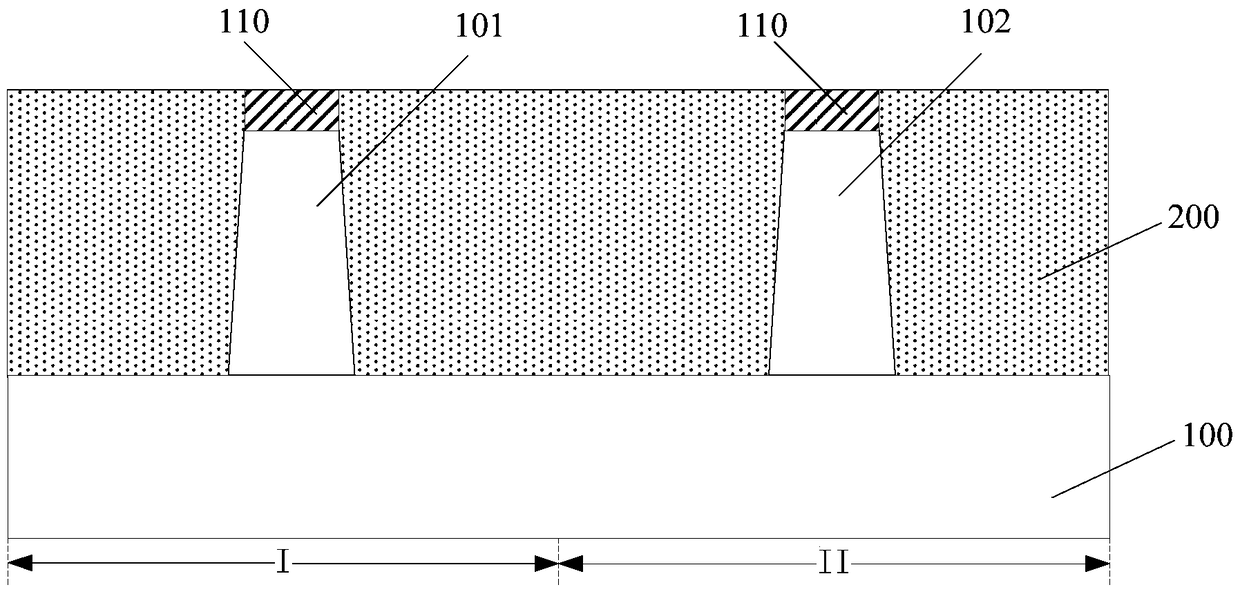

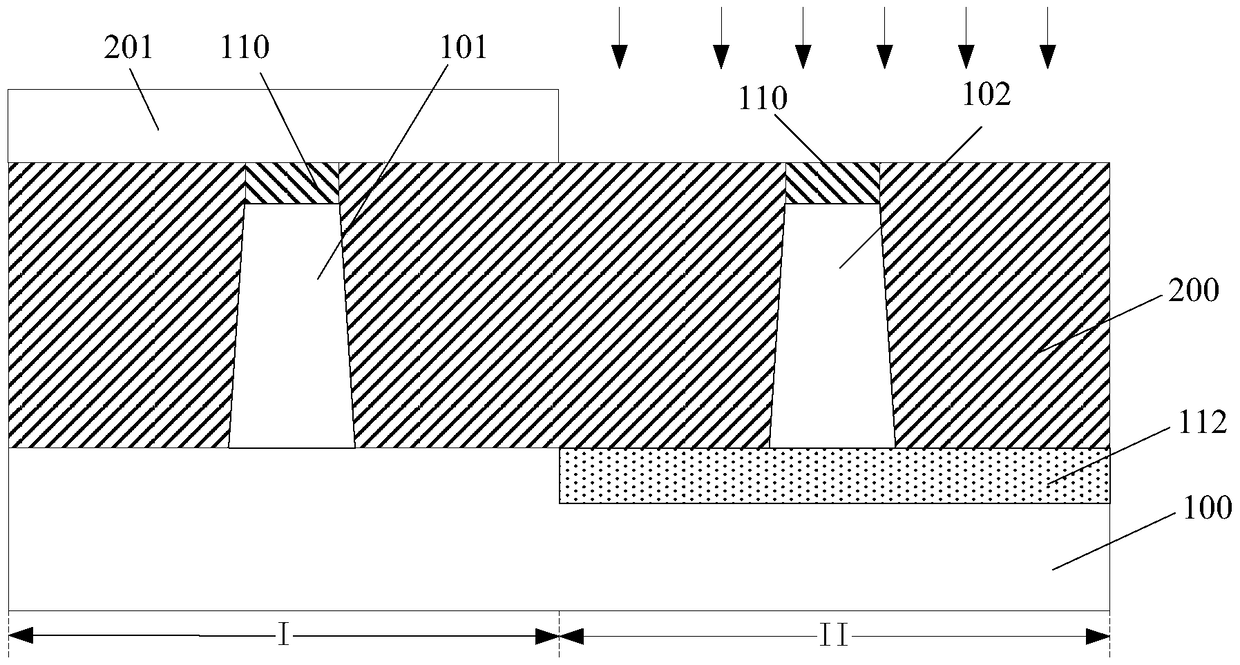

[0033] As mentioned in the background art, the performance of the P-type fin field effect transistor formed in the prior art needs to be further improved.

[0034] Studies have found that the migration rate of hole carriers in germanium or germanium-silicon materials in P-type fin field effect transistors is greater than that in silicon, and using germanium or germanium-silicon materials as fin materials can improve the performance of P-type fin field effect transistors. The hole mobility of the P-type fin field effect transistor, thereby improving the performance of the P-type fin field effect transistor. In one embodiment, a germanium layer or a silicon germanium layer may be formed by epitaxy on a substrate, and then the germanium layer or silicon germanium layer may be etched to serve as the channel region of the P-type fin field effect transistor. However, the yield of the single-crystal germanium layer formed by the epitaxial process is low and the cost is high, and ther...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More