Method for reducing internal storage consumption inedge enhancement for multi-output pixed device

An edge enhancement and multi-output technology, which is applied in the field of reducing memory consumption when performing edge enhancement on a multi-output pixel device, can solve the problems of memory storage capacity consumption, multi-hardware cost, cost, etc., to achieve reduced consumption, good output effect, and fast The effect of print speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

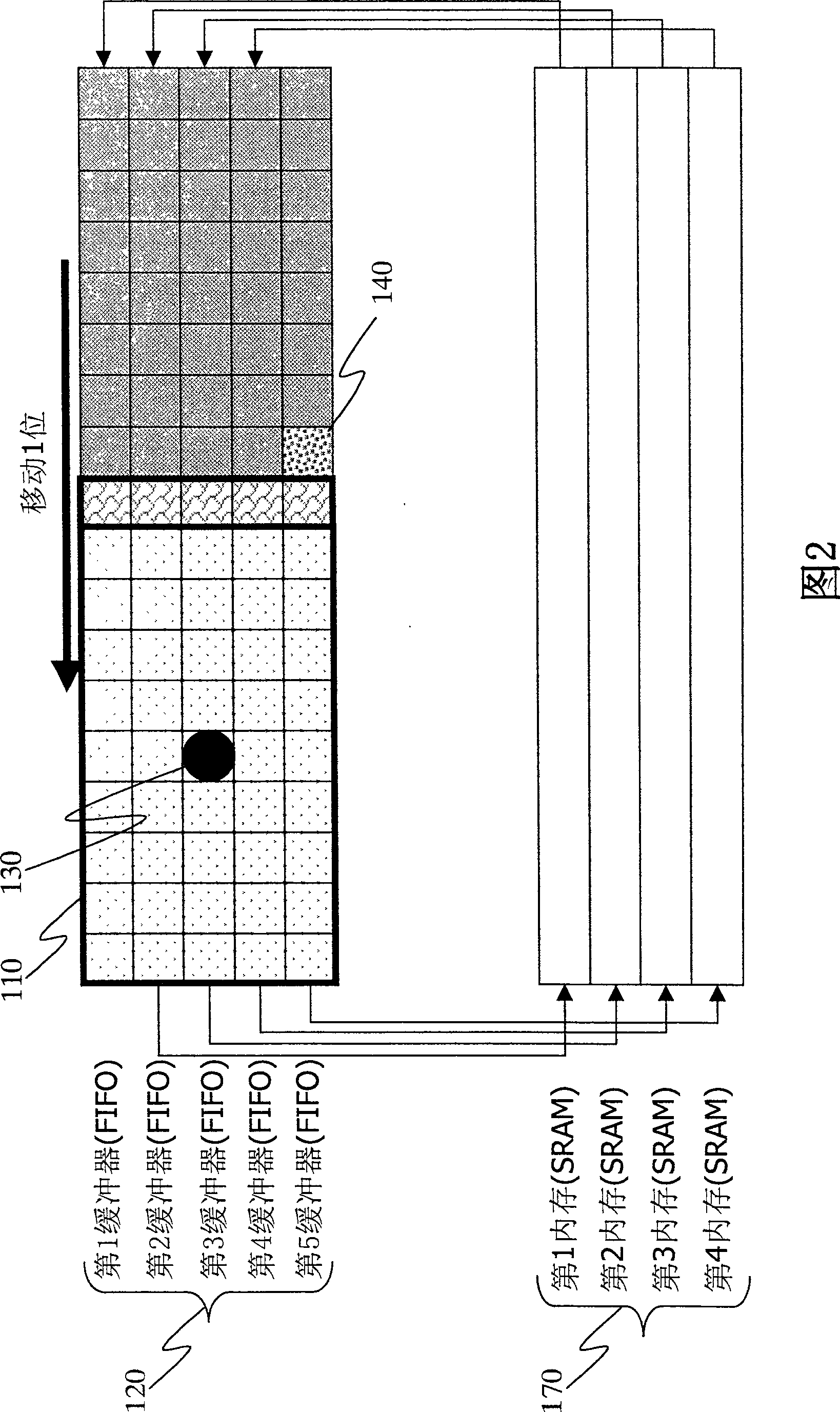

[0053] The features and embodiments of the present invention are described in detail below with reference to the accompanying drawings. The present invention provides a method for reducing memory consumption when performing edge enhancement on multi-output pixel devices. In the following detailed description, various specific details are described in order to provide a complete explanation. However, those skilled in the art may practice the present invention without these specific details, or substitute some components or methods to practice the present invention. The present invention does not describe known methods, procedures, components, and circuits in detail so as not to obscure the gist of the present invention.

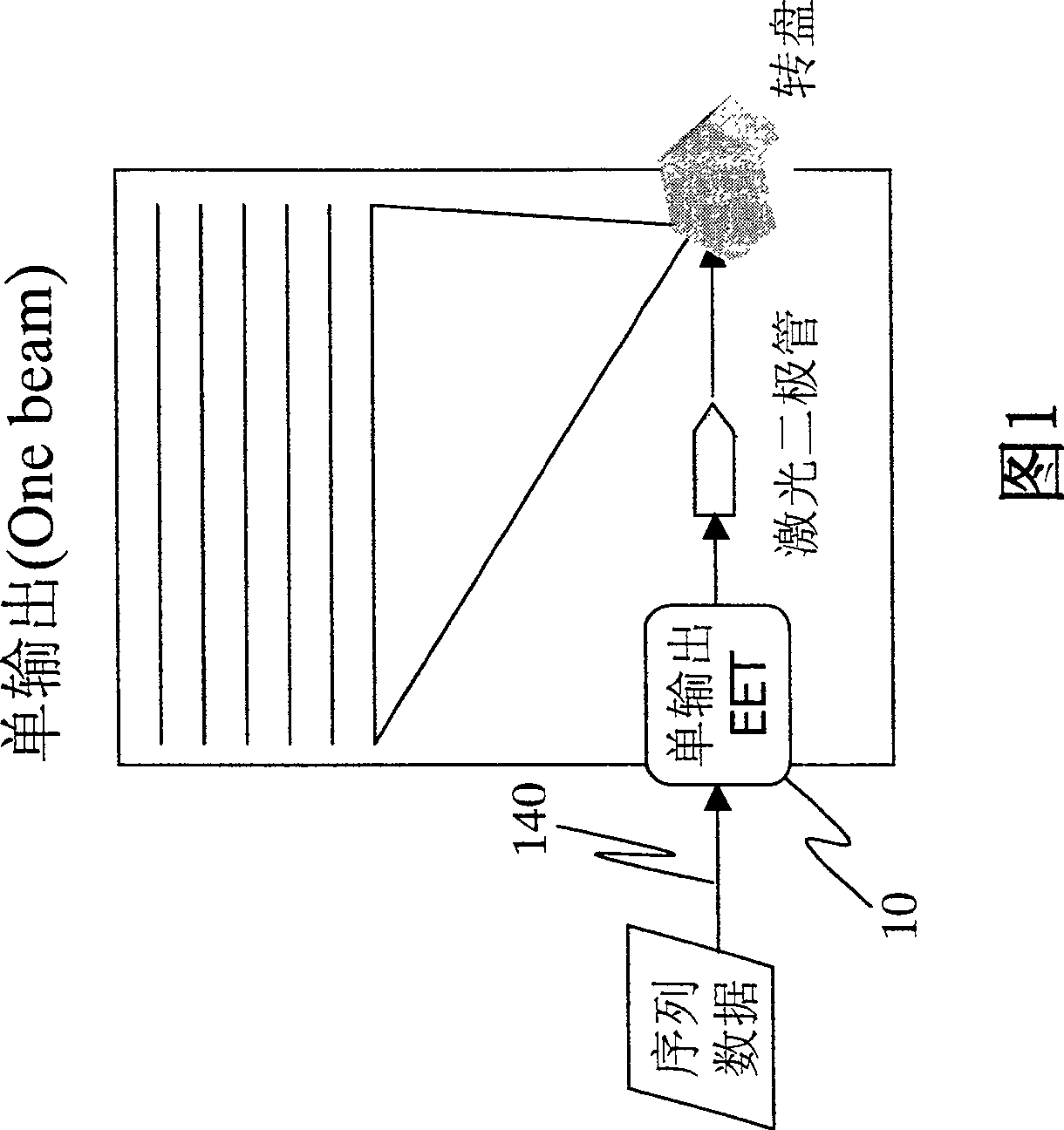

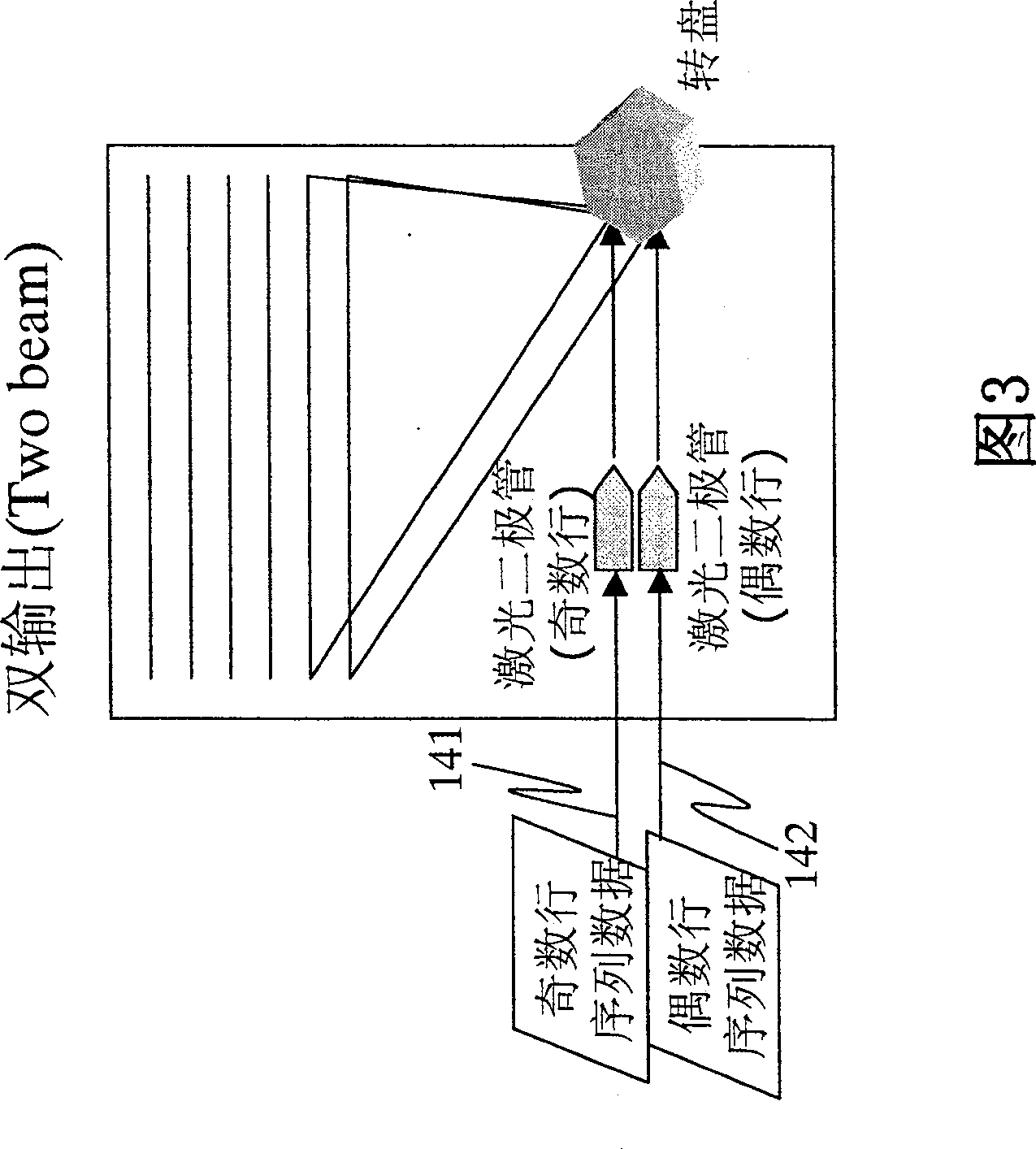

[0054] Although the present invention can be extended to the application of n output pixel devices, for ease of understanding, two output pixel devices are used as an example to illustrate, please refer to FIG. 4, which is the dual output edge enhancement tec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More