System and method for implementing memory mediation of supporting multi-bus multi-type memory device

A technology for implementing systems and memories, which is applied in the field of memory arbitration implementation systems, can solve problems such as clock cycles cannot be used to access memories, difficult verification, complex processing, etc., and achieve strong design reusability, good design flexibility and reusability , the effect of high bandwidth utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

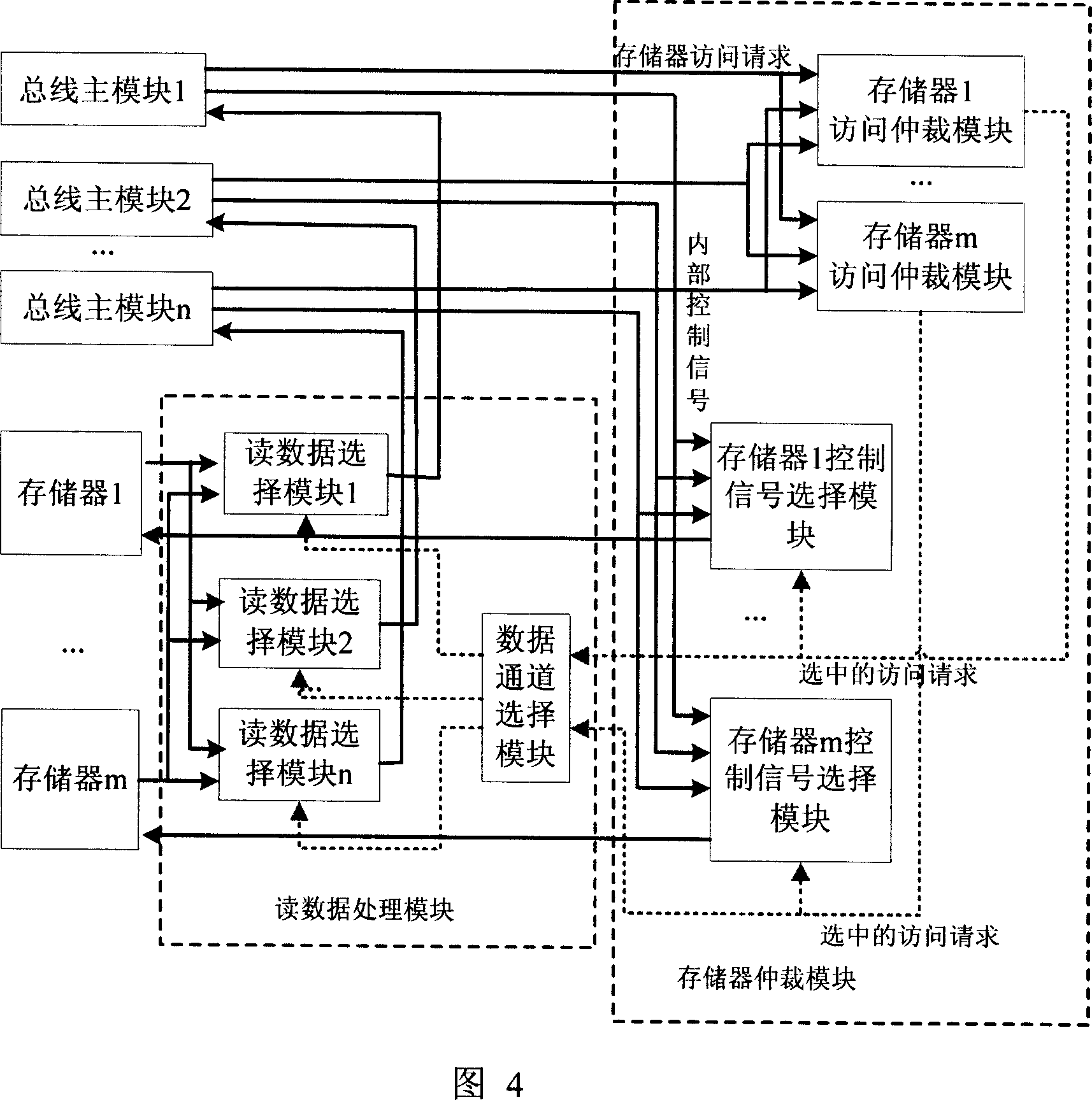

[0053] Below in conjunction with the embodiment provided in Figure 4, the memory arbitration implementation system supporting multi-bus and multi-type memories of the present invention is further described:

[0054] As shown in Figure 4, the structure of each memory arbitration module in the m memory arbitration modules in the system of this embodiment is the same, wherein each memory arbitration module may include: a memory access arbitration module, and a memory access arbitration module related to the memory access The arbitration module is correspondingly connected with a memory control signal selection module, and the memory control signal selection module is also connected with n bus master modules.

[0055] Wherein, each memory access arbitration module receives memory access requests from n bus master modules, and arbitrates the received memory access requests, and outputs the arbitration result; that is, the memory access arbitration module accesses the memory accordin...

Embodiment 2

[0062] As shown in Fig. 5, with respect to Fig. 4, the system of the present embodiment also includes: n bus interfaces connected one-to-one with n bus master modules, and each bus interface provides a bus path;

[0063] Correspondingly, any memory access arbitration module can receive memory access request signals sent from n bus master modules through their one-to-one corresponding bus interfaces; n read data selection modules in the read data processing module output the read data from the memory, output to the n bus master modules through the n bus interfaces corresponding thereto one-to-one.

[0064] The above-mentioned bus interface is mainly used to process various types of bus protocols, and convert the received memory access request into a signal output by a unified output interface (for example, the bus interface provides a 3-bit access request line, a 16-bit read-write address line, a 16-bit byte selection line, which is equivalent to providing a unified output inte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More