A compound bar, bar source self-separating VDMOS, 1GBT power unit and its making technology

A power device and manufacturing process technology, which is applied in the field of composite gate, gate-derived isolation VDMOS, IGBT power devices and their manufacturing process, can solve problems such as poor economy and practicability, affecting working life, and complex product costs, and achieve product The effect of easy quality assurance, simplified manufacturing process, and enhanced yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

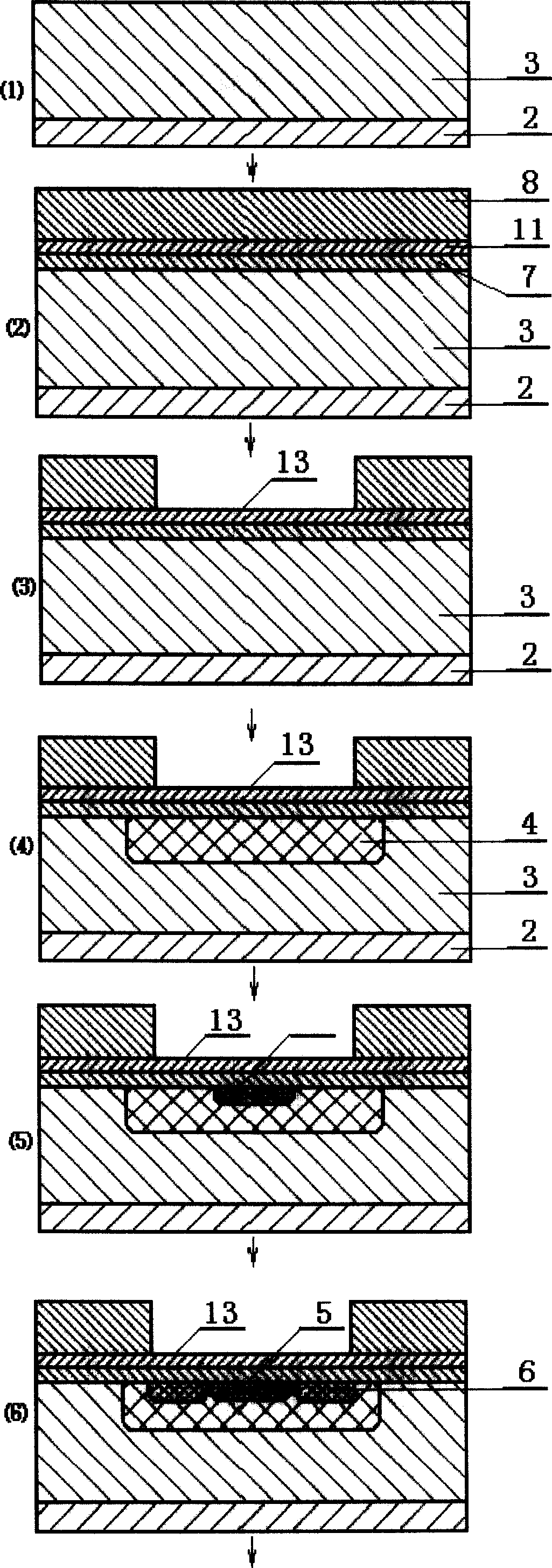

[0033] The present invention will be further described below in conjunction with the accompanying drawings and typical embodiments.

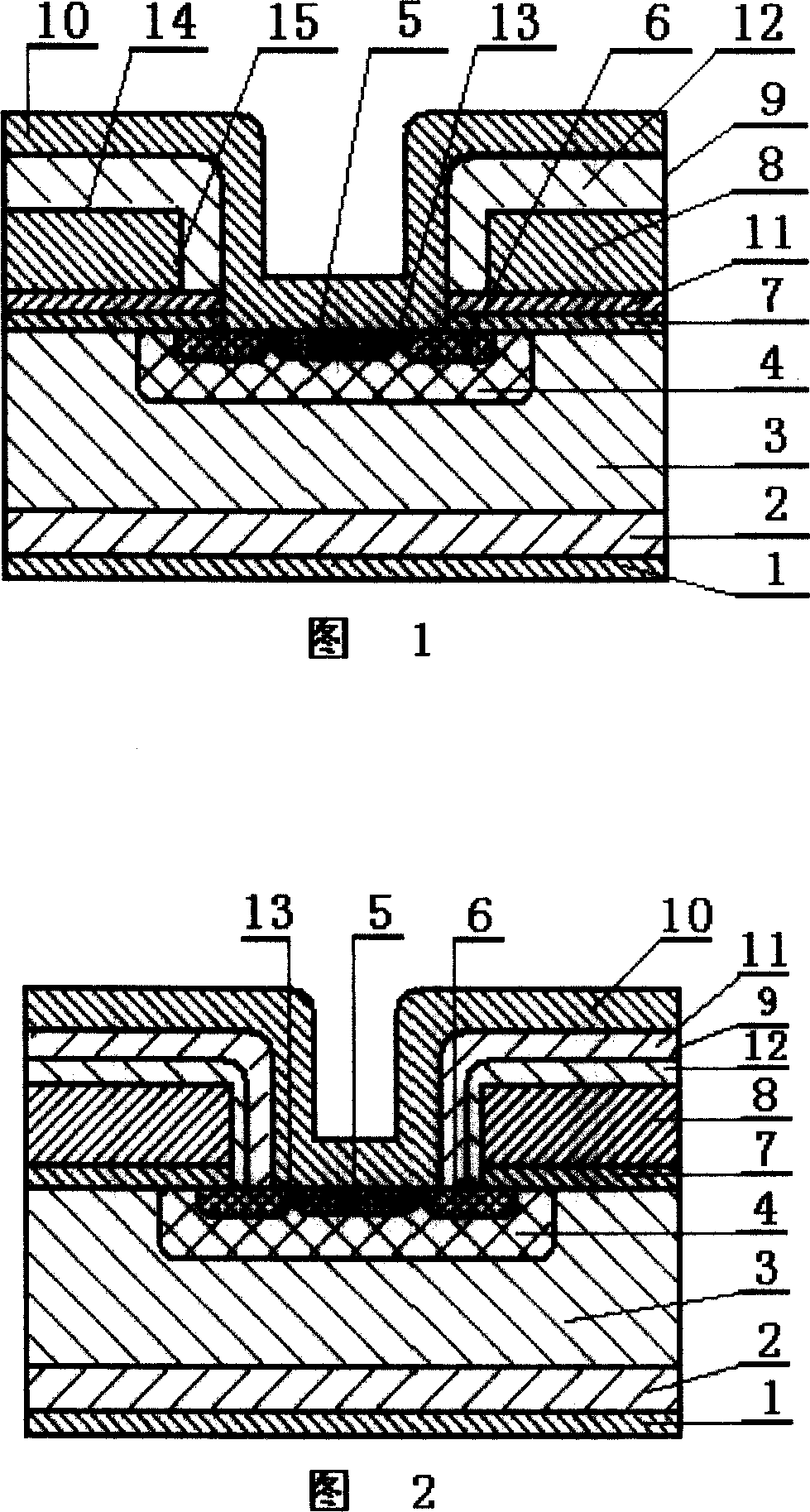

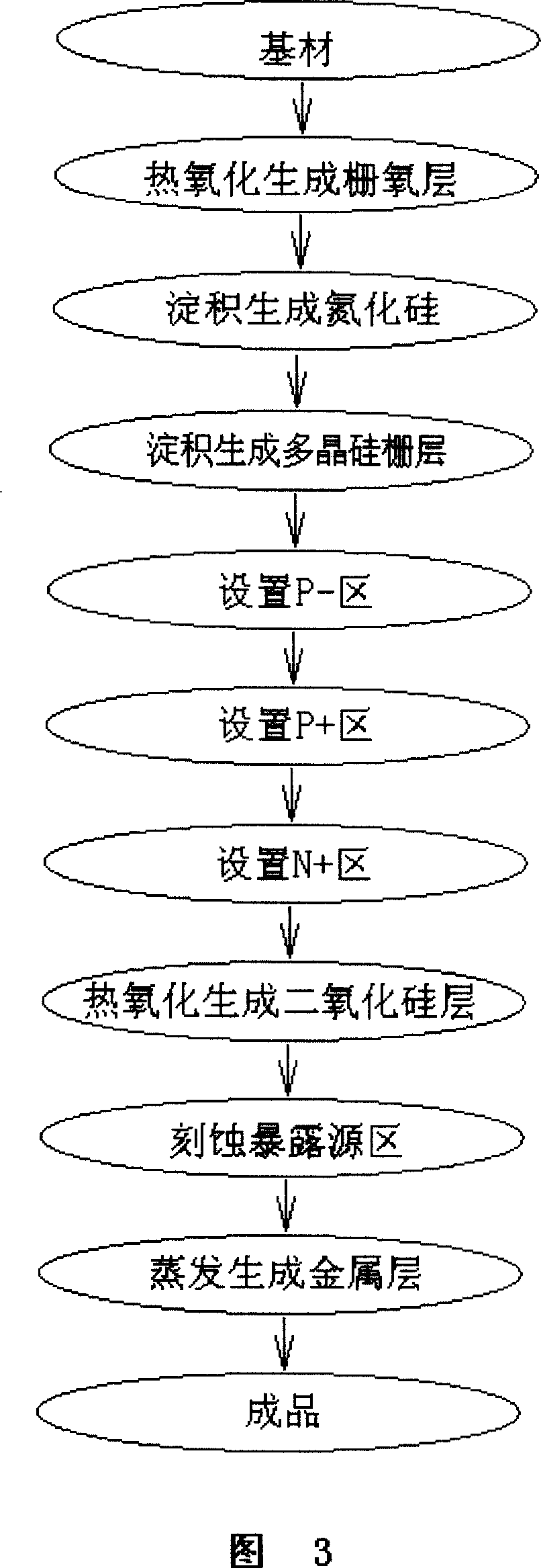

[0034] In Fig. 1 and Fig. 2, composite gate of the present invention, gate originates from isolation VDMOS, IGBT power device mainly is by metal bottom layer 1, N+ substrate layer (in IGBT is P+ substrate layer) 2, N- epitaxial layer 3, P -zone 4, P+ zone 5, N+ zone 6, thermally oxidized SiO 2It consists of a gate oxide layer 7, a polysilicon gate layer 8, a source gate isolation layer 9 and a metal surface layer 10. The metal surface layer 10 acts as the source, the metal bottom layer 1 acts as the drain, and the polysilicon gate layer 8 acts as the gate. The source region consists of the P-region 4 located in the deep layer, the P+ region 5 located in the middle of the surface layer, and the ring-shaped N+ region located on the periphery of the P+ region 5. 6 composition. It is characterized in that thermal oxide SiO is provided between the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More