Semiconductor device and a method of manufacturing the same

A technology for semiconductors and devices, applied in the field of semiconductor devices and their manufacturing, can solve problems such as junction leakage, difficulty in fully ensuring the width of sidewall spacers, etc., and achieve the effect of preventing problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] Hereinafter, embodiments of the present invention will be explained with reference to the drawings. In all the drawings for explaining the embodiments, in principle the same reference numerals and symbols are used for the same elements, and repeated descriptions thereof are omitted.

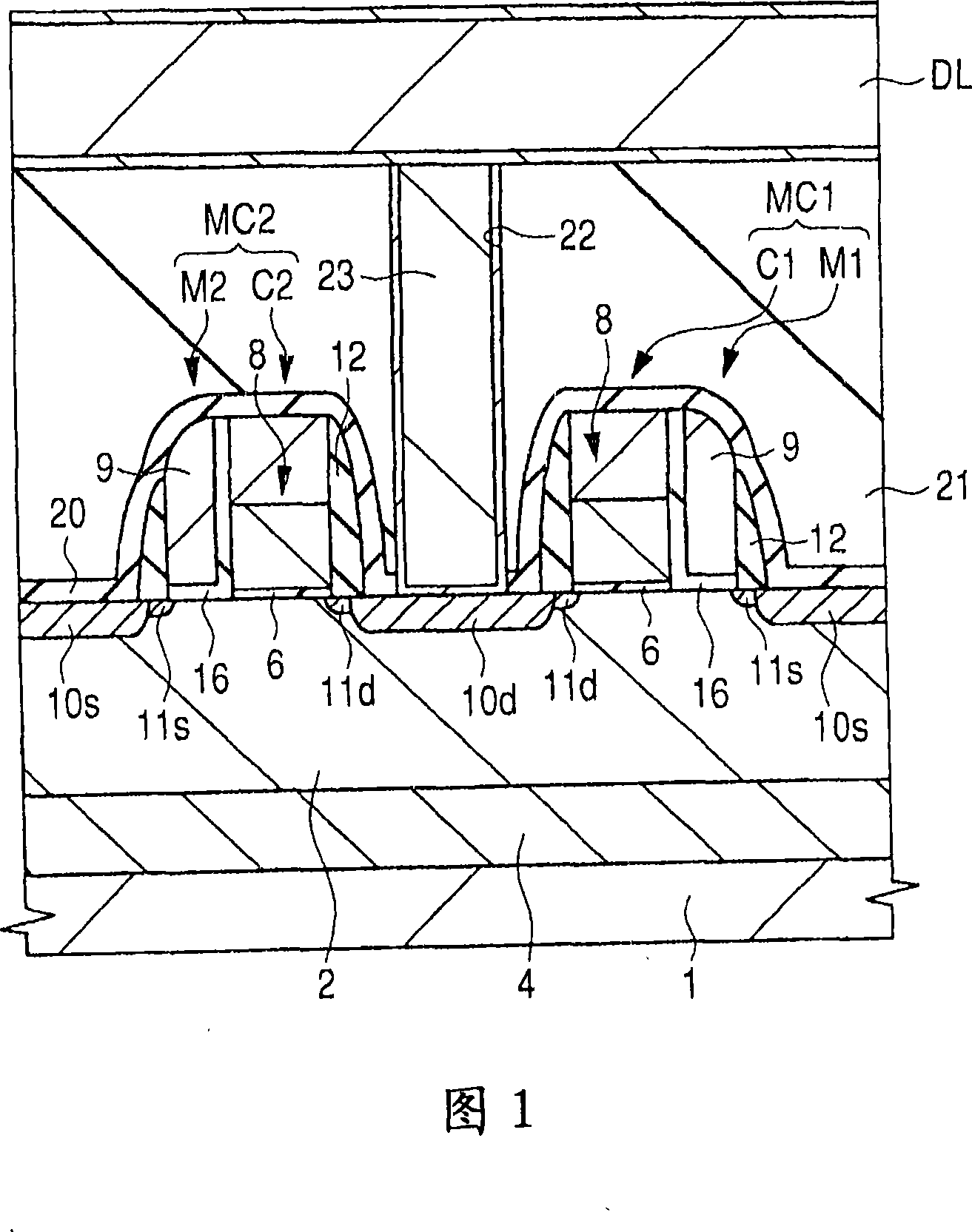

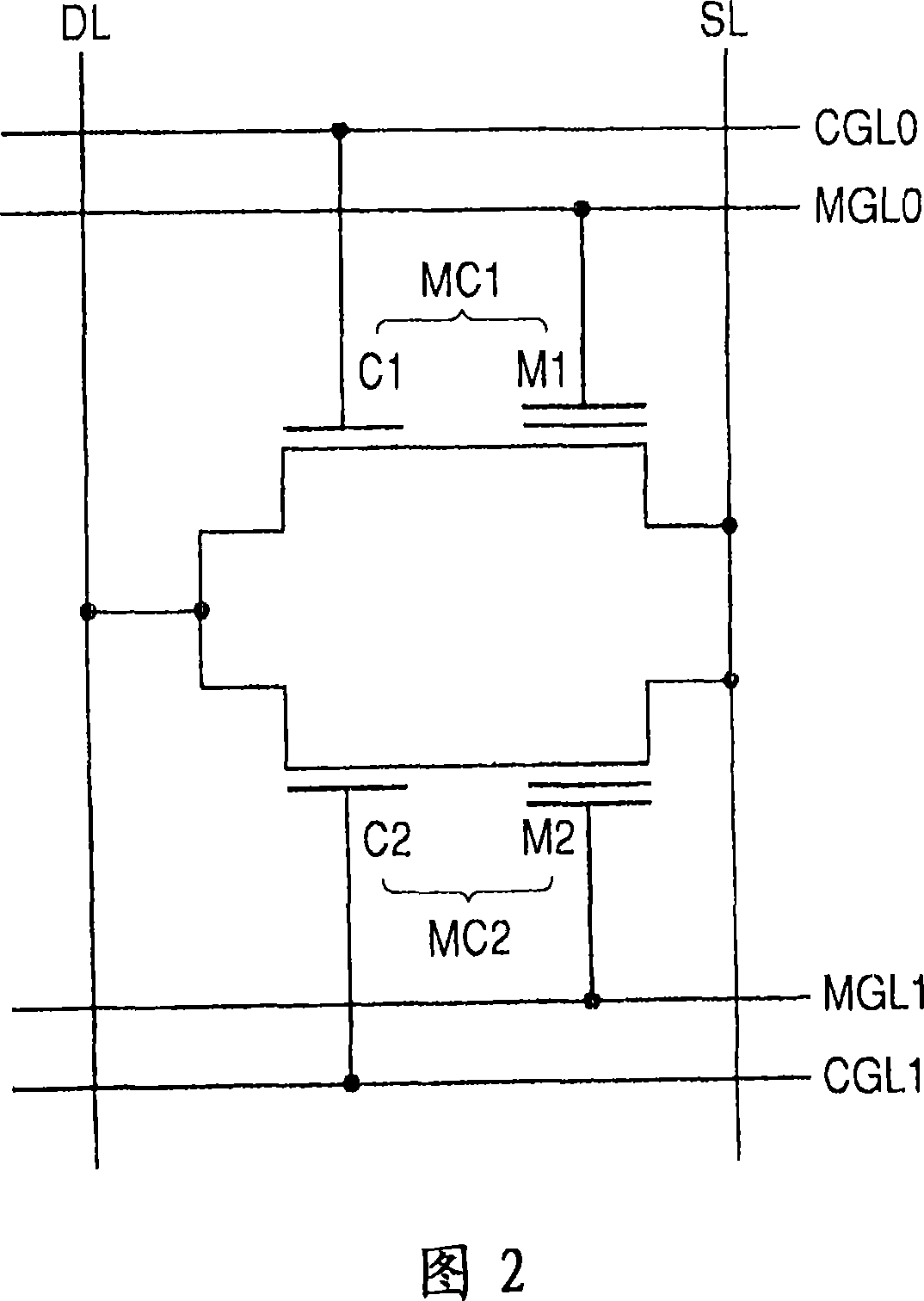

[0051] 1 is a cross-sectional view showing a relevant portion of a MONOS (Metal Oxide Nitride Oxide Semiconductor) type nonvolatile memory according to an embodiment, and FIG. 2 is a diagram of the MONOS type nonvolatile memory shown in FIG. 1. Equivalent circuit diagram. 1 and 2 show two memory cells (MC1, MC2) arranged adjacent to each other.

[0052] Memory cell MC1 as a MONOS type nonvolatile memory is formed at p-type well 2 in semiconductor substrate 1 (hereinafter, simply referred to as "substrate") made of a p-type single crystal silicon substrate or the like. The p-type well 2 to which a desired voltage is applied is electrically separated from the substrate 1 by an n-type embed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com