Construction method and seven-value circuit of T-type network threshold-expansion any value general gate circuit

A construction method and gate circuit technology, which can be applied in the direction of logic circuits with logic functions, etc., can solve the problems of increasing ions, difficulty in applying multi-value circuits, and increasing process complexity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

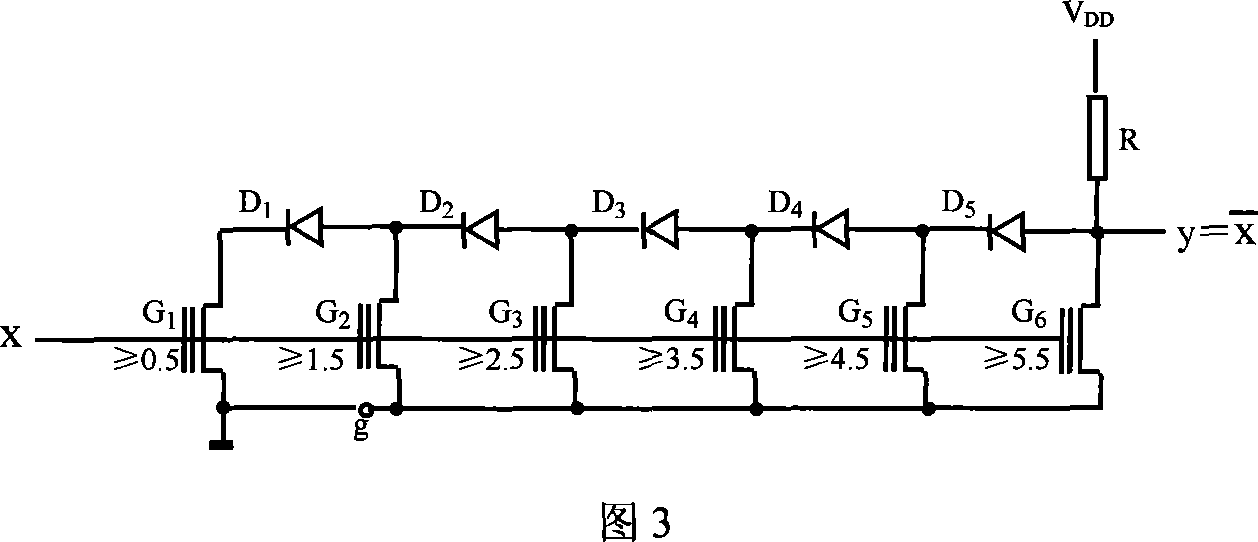

[0046] Embodiment 1: T-shaped network expanded threshold type seven-valued NOT gate circuit

[0047] In conjunction with FIG. 3, this embodiment uses 6 threshold-expanded NMOS transistors G i (i=1, 2, 3, 4, 5, 6), their gates are connected to input x through the threshold expansion circuit; tube G 1 The source is grounded, the other tubes G 2 ~G 6 The sources of all are connected to the lead wire g, and g has two connection methods: g grounding and g taking over G 1 The drain, the seven-value NOT gate selects g to ground; uses 5 diodes D i (i=1, 2, 3, 4, 5), diode D i The negative pole and positive pole of the gate are sequentially connected to the expanded threshold NMOS transistor G i The drain and expanded threshold NMOS transistor G i+1 Drain; threshold-expanded NMOS transistor G 6 The drain of the load is connected to the power supply V DD , and in the expanded-threshold NMOS tube G 6 The drain forms the seven-valued NOT gate output y. Expanded-threshold NMOS tr...

Embodiment 2

[0049] Embodiment 2: T-shaped network threshold expansion seven-valued right-shift gate circuit

[0050] Figure 4 and Figure 3 have the same structure, and the seven-valued right-sliding gate is G in Figure 4 1 ~G 6 The expanded threshold NMOS tube G i The normalized extended threshold value of i=1, 2, 3, 4, 5, 6 is sequentially taken as <4.5, <3.5, <2.5, <1.5, <0.5, ≥5.5.

[0051] Seven-valued right-sliding door requirements: when the input x is 6, 0, 1, 2, 3, 4, 5, the output z of the right-sliding door is 0, 1, 2, 3, 4, 5, 6 in sequence. Figure 4 Threshold Expanded NMOS Transistor G i The normalized extended thresholds of i=1, 2, 3, 4, 5, 6 are 6 Turn on, output z=0. ②When x=0, then x6 Cut off, G 5 and D 5 Conduction, output z=1; ③When x=1, then x5 , G 6 Cut off, G 4 and D 4 、D 5 Conduction, output z=2; ④When x=2, then x4 ~G 6 Cut off, G 3 and D 3 ~D 5 Conduction, output z=3; ⑤When x=3, then x3 ~G 6 Cut off, G 2 and D 2 ~D 5 Conduction, output z=4; ⑥When x...

Embodiment 3

[0052] Embodiment 3: T-shaped network expanded threshold type seven-valued follower circuit

[0053] Figure 6 and Figure 3 have the same structure, the seven-valued follower in Figure 6 G 1 ~G 6 The expanded threshold NMOS tube G i The normalized extended threshold of i=1, 2, 3, 4, 5, 6 is sequentially taken as <5.5, <4.5, <3.5, <2.5, <1.5, <0.5.

[0054] Seven-valued follower requirements: when the input x is 0, 1, 2, 3, 4, 5, 6, the output u is still 0, 1, 2, 3, 4, 5, 6 in turn. Figure 6 Threshold Expanded NMOS Transistor G i The normalized extended threshold of i=1, 2, 3, 4, 5, 6 is sequentially taken as 6 Conduction, output u=0; ②When x=1, then x6 Cut off, G 5 and D 5 Conduction, output u=1; ③When x=2, then x5 , G 6 Cut off, G 4 and D 4 、D 5 Conduction, output u=2; ④When x=3, then x4 ~G 6 Cut off, G 3 and D 3 ~D 5 Conduction, output u=3; ⑤When x=4, then x3 ~G 6 Cut off, G 2 and D 2 ~D 5 Conduction, output u=4; ⑥When x=5, then x2 ~G 6 Cut off, G 1 and D ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com