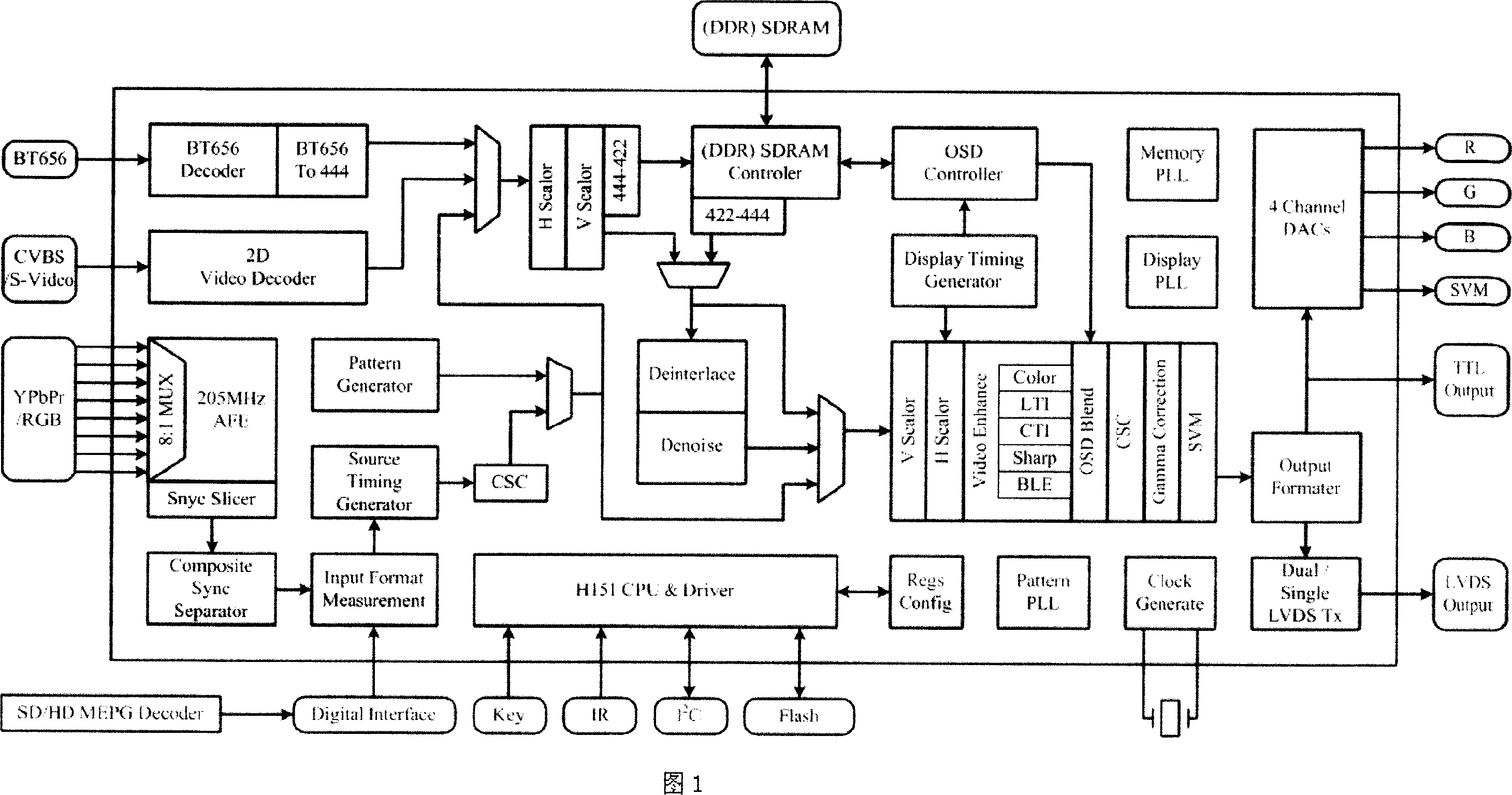

High-definition digital television SOC chip dual-mode structure

A digital TV, dual-mode technology, applied in the field of system-level SOC chip architecture design, can solve the problems of slow response speed, poor zoom effect, low filter order, etc., to increase investment, save design and production costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

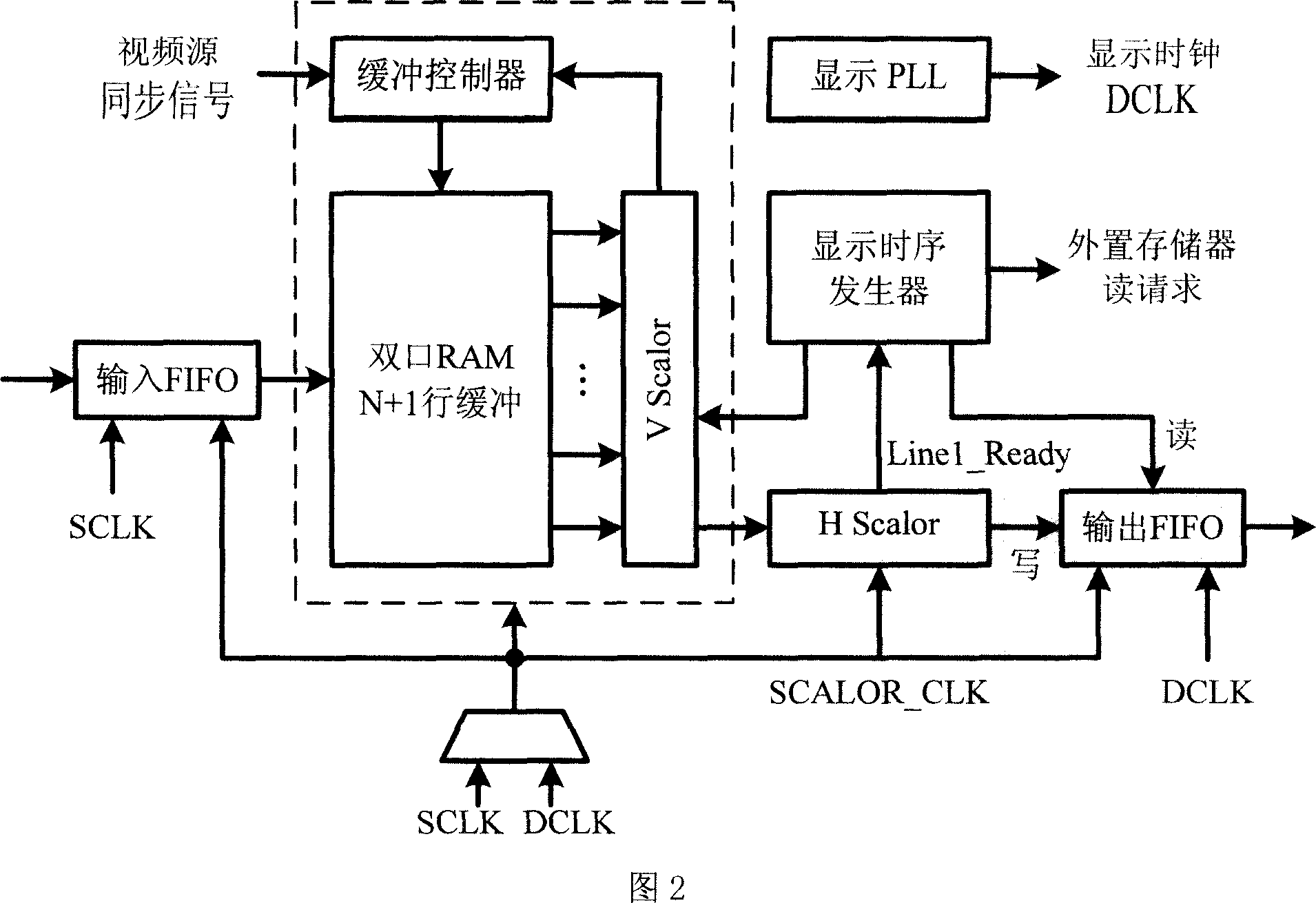

Method used

Image

Examples

Embodiment Construction

[0054] Taking the LCD TV application solution as an example, the display timing configuration parameters in the mode without external memory are shown in Table 1.

[0055] In the table, video source lists various video formats stipulated by international video standards and commonly used PC display formats. i means interlaced video, p means progressive video. 50 and 60 represent the frame rate of progressive video or the field rate of interlaced video. Among them, 1080i50 has two formats. The listed PC display format has a frame rate of 60Hz. The percentage shown in the video source column is the vertical effective ratio of the corresponding video format. The unit of pixel rate is MHz.

[0056] Table 1 LCD TV input and output scaling ratio table

[0057]

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More