Microprocessor structure based on sophisticated vocabulary computerarchitecture

A technology of computer structure and complex instruction set, applied in the architecture with a single central processing unit, general-purpose stored program computer, computing, etc., can solve the problem of low utilization rate of most instructions, low operation efficiency of instructions, and difficulty in meeting the needs of fast processing applications and other problems, to achieve the effect of rich instructions, good scalability, and faster instruction processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be described in detail below in conjunction with the accompanying drawings.

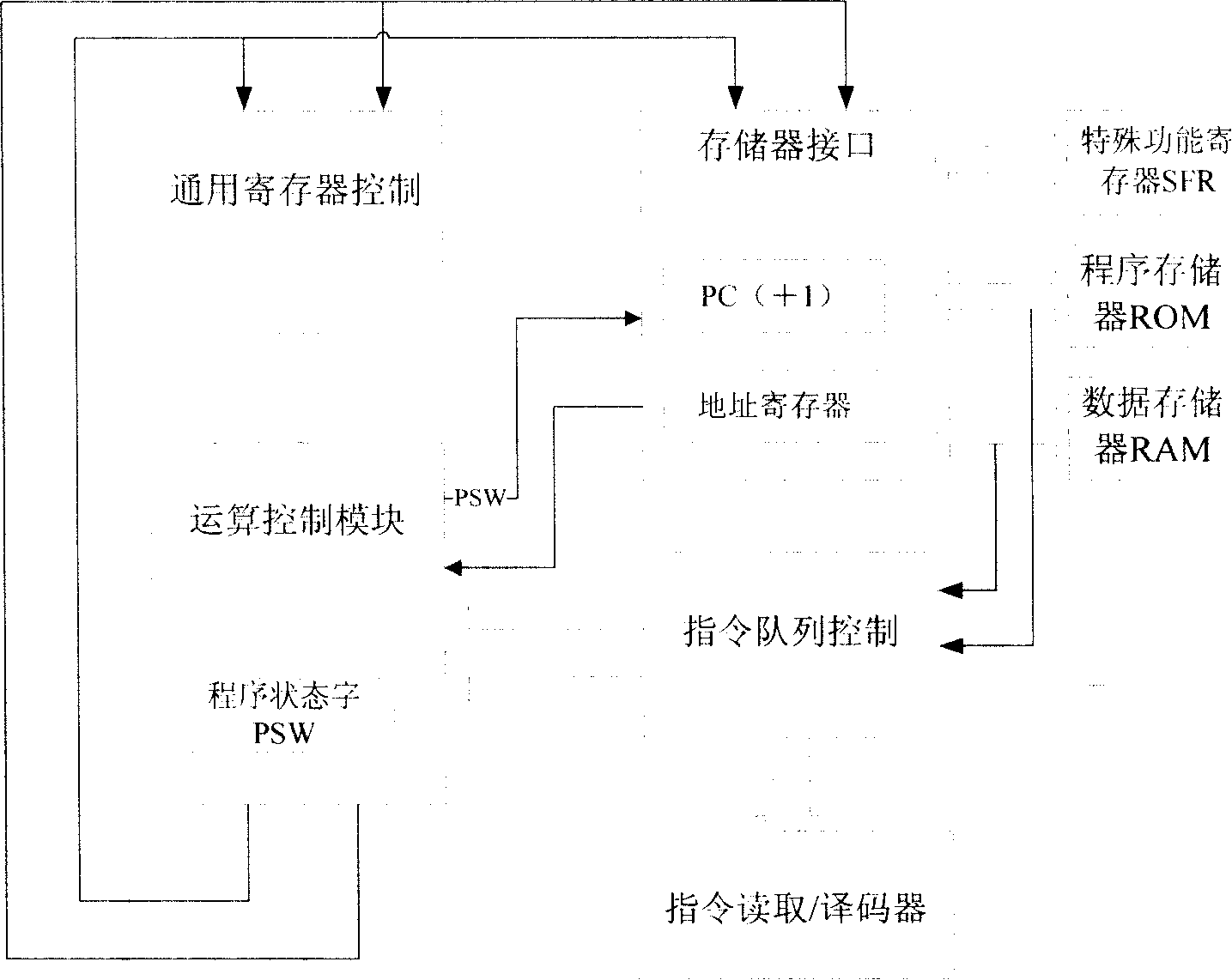

[0034] Such as figure 1 It is the internal structure of the microprocessor of the present invention. The external clock generator provides the basic clock, and the frequency division generates the clock signal required by the core. Program memory and data memory have separate data buses. The instruction reading and decoder has the functions of instruction decoding and controlling other modules of the microprocessor core. The operation control module includes an arithmetic logic unit, a shift control unit and a decimal adjustment unit. PSW is the program status word, which stores some flag bits of the program, including JF, ZF, CF, HF, SF, VF. JF is the jump flag, ZF is the zero flag, CF is the carry flag, HF is the half-carry flag, SF is the sign flag, and VF is the overflow flag.

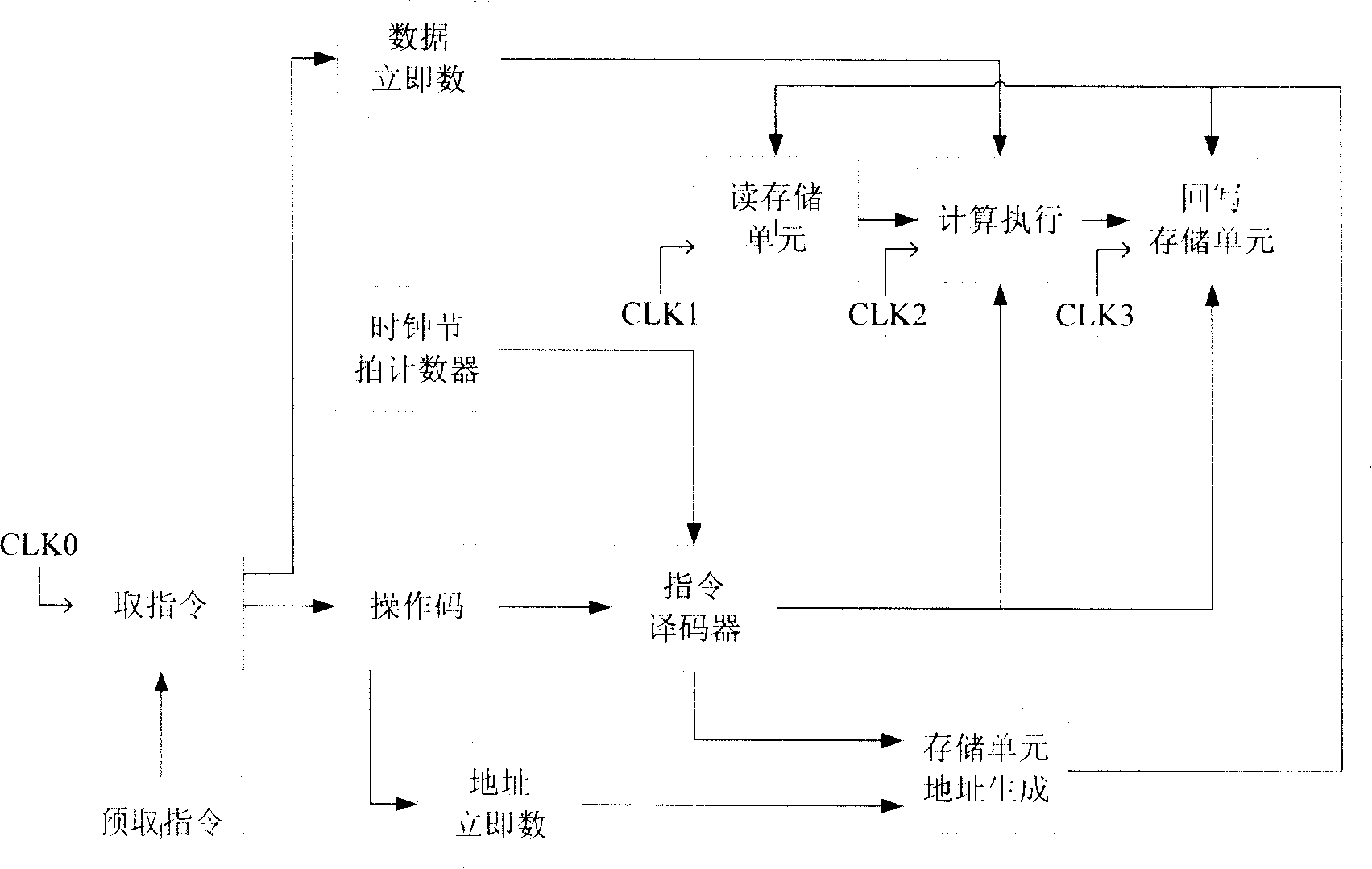

[0035]The pipeline instruction structure is a single-stage four-stage pipeline i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More