Low pressure difference voltage stabilizer

A low-dropout voltage regulator and voltage divider circuit technology, which is applied in the direction of instruments, electric variable adjustment, control/regulation systems, etc., can solve the problems of internal compensation not strong enough, not suitable for low current, large transconductance, etc., to reduce current Consumption level, strong stability, and the effect of improving output impedance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

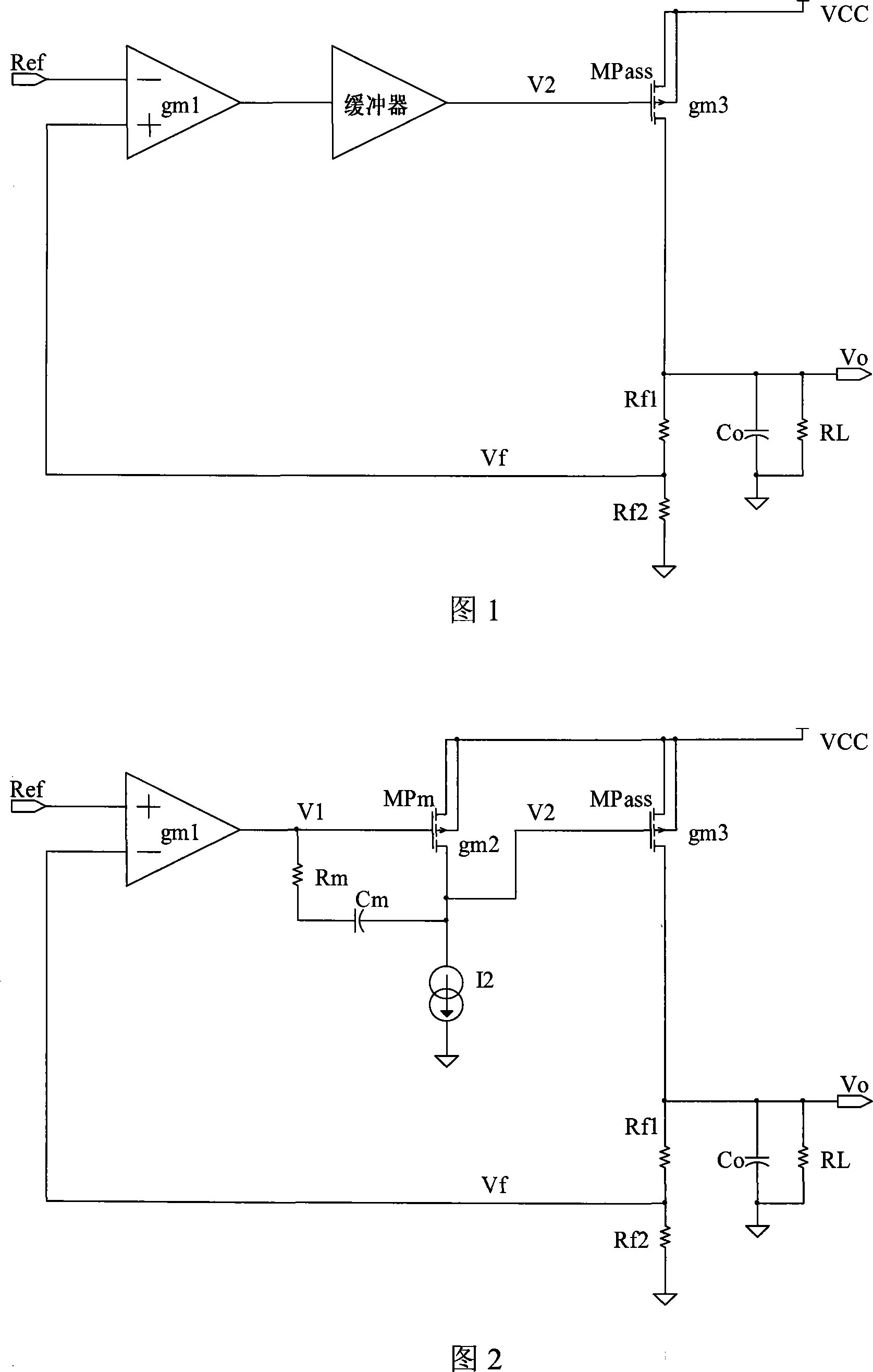

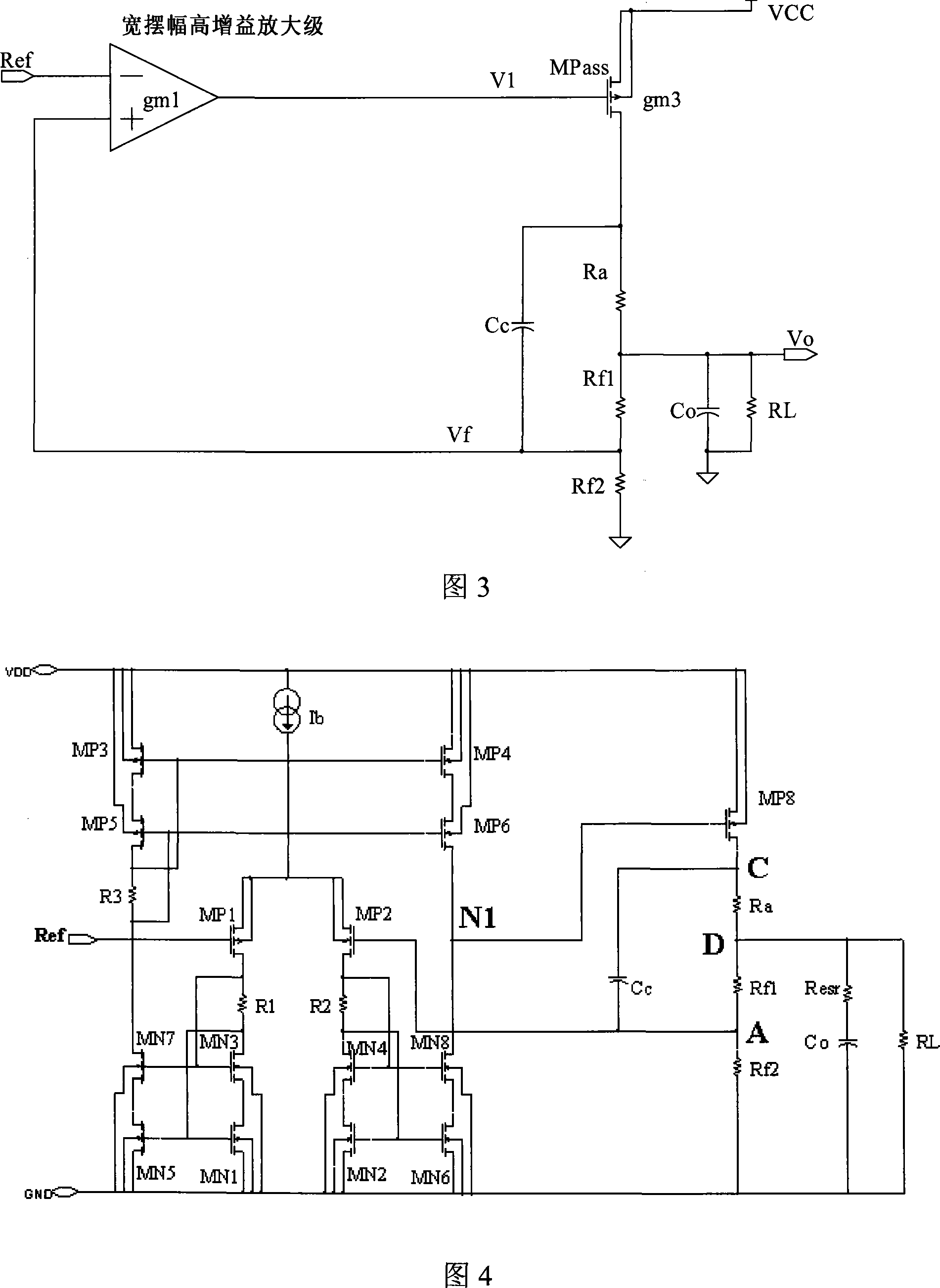

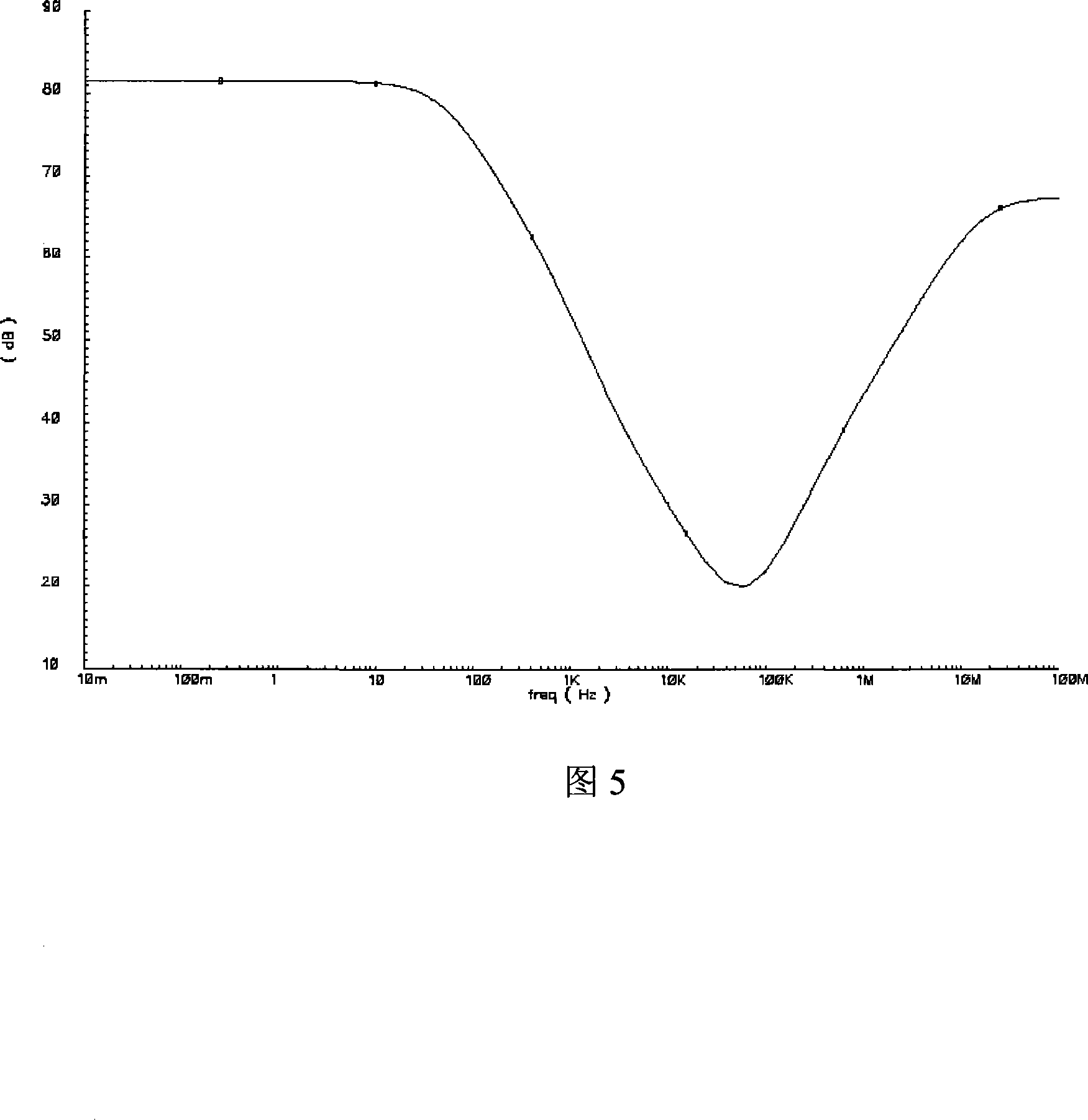

[0034] Like the prior art, the low dropout regulator of this embodiment also includes a differential amplifier circuit, an output amplifier circuit and a voltage divider circuit. The output amplifier circuit includes a PMOS transistor (also referred to as an output transistor) whose source is connected to the input power supply voltage Vdd, and an output capacitor Co connected between the voltage output point D (that is, the node from which the output voltage Vout is drawn) and ground, The resistor Resr in the figure is the equivalent series resistance of the output capacitor Co, R L Indicates the load. The two input terminals of the differential amplifier circuit are respectively connected to the reference voltage Ref and the voltage dividing point A of the voltage dividing circuit, and its output terminal N1 is connected to the gate of the PMOS transistor. The voltage dividing circuit is connected between the voltage output point and the ground. On this basis, in this embo...

no. 2 example

[0062] In the first embodiment, in order to realize the double zero pair compensation, the resistance R a The resistance value is very small, and metal resistors are generally used. The circuit structure adopted in this embodiment improves on this problem.

[0063] The structure of the low dropout voltage regulator of this embodiment is shown in FIG. 6 and FIG. 7 . The only difference from the circuit of the first embodiment is that a PMOS transistor MP7 is added to the output amplifier circuit. The source of MP7 is connected to the input voltage power supply Vdd, the drain is connected to the voltage output point D, and the gate is connected to the gate of MP8. In this implementation, the width-to-length ratio (W / L) of MP8 MP8 Far smaller than MP7's width-to-length ratio (W / L) MP7 , such as 1 / 10000 to 1 / 10. The current flowing through MP8 and Ra will be much smaller than the current flowing through MP7.

[0064] Suppose N=(W / L) MP7 / (W / L) MP8 , and then analyze the str...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More