Microcosm algorithm hardware platform realizing method based on FPGA

A technology of world and algorithm, applied in the field of hardware platform implementation of small world optimization algorithm, can solve the problems of complex design of hardware optimization platform and demanding function properties, and achieve the effect of overcoming the problem of deception, low development cost and stable structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

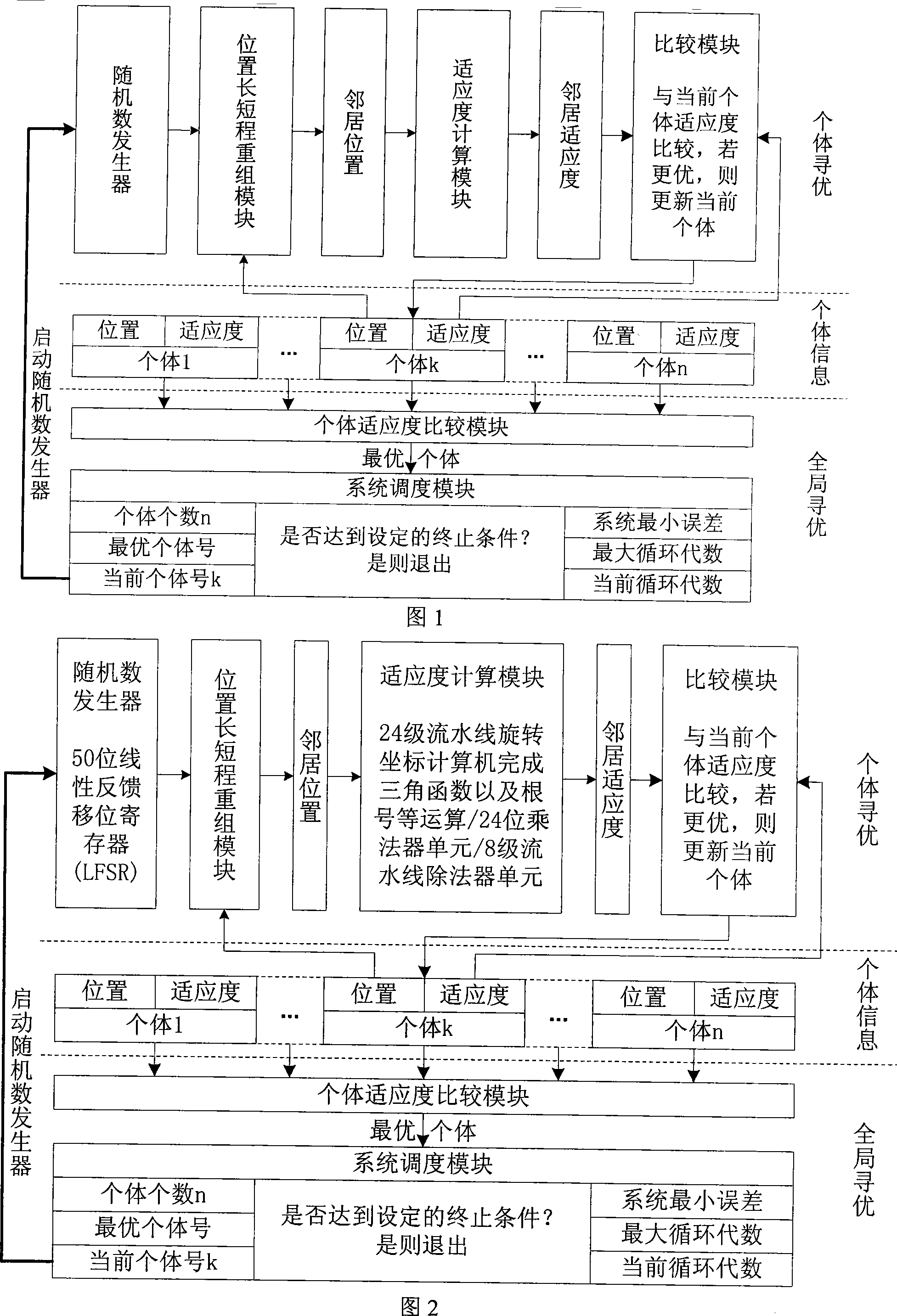

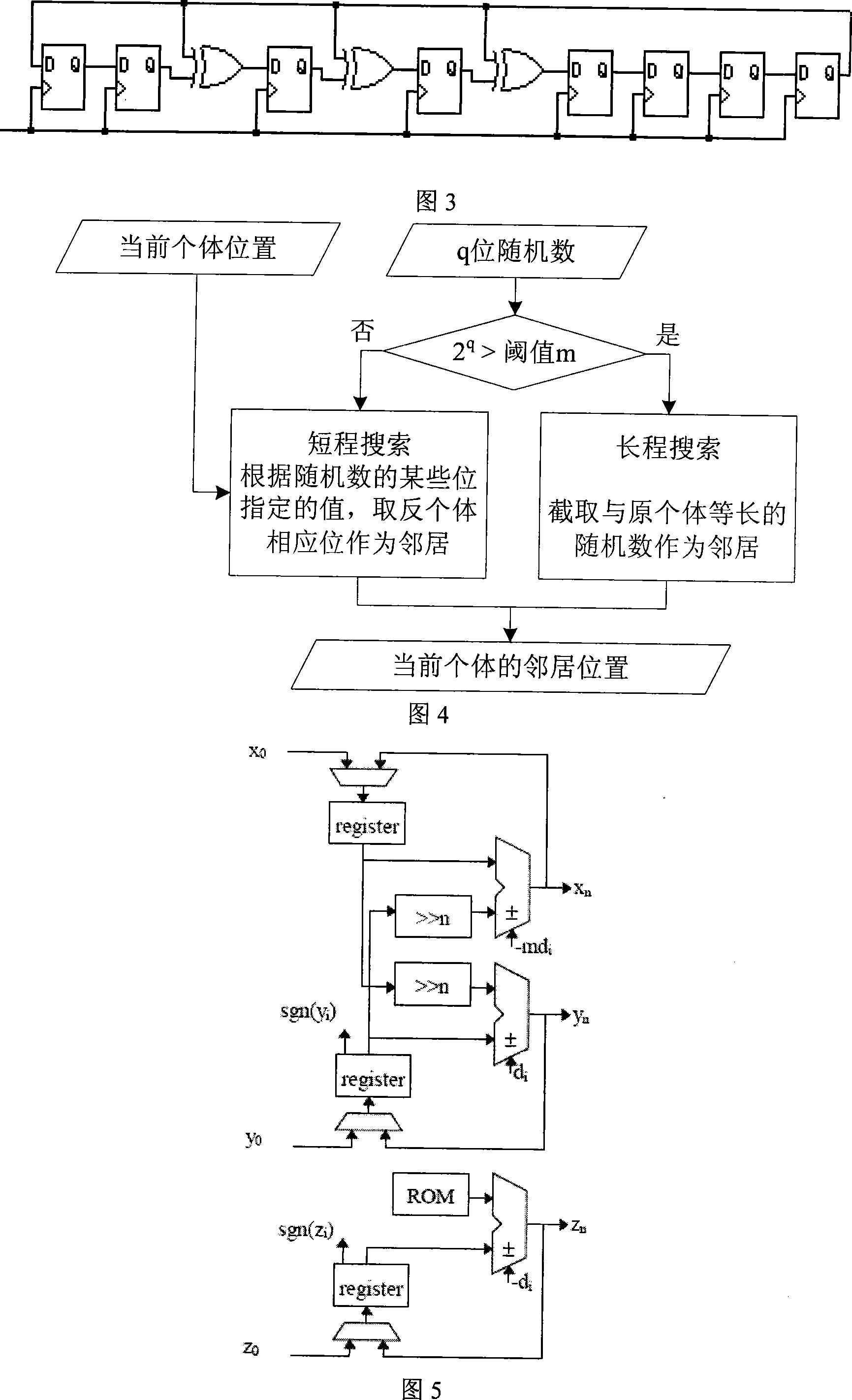

[0026] The present invention adopts the principle of small-world algorithm to realize optimized operation on the hardware platform constructed by FPGA (Field Programmable Gate Array). The specific scheme is as follows.

[0027] Because the small-world algorithm needs two steps of "individual optimization" and "global optimization", the individual optimization process is completed by three steps of "neighborhood search", "fitness calculation" and "optimum selection", and the global optimization process is completed again Globally select the best for each individual and perform overall scheduling. Therefore, as shown in Figure 1, the small-world algorithm implemented in FPGA needs to build the following two-level structure:

[0028] 1. The first layer completes the individual optimization process, which consists of a random number generator module, a position reorganization module, a fitness calculation module and a comparison module. The random number generator generates a ra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More