Manufacture method of semiconductor device

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of not being able to suppress the degradation of short-channel effect lifetime, increase process complexity and thermal budget cost, and improve device reliability. performance, reducing substrate leakage current and the effect of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

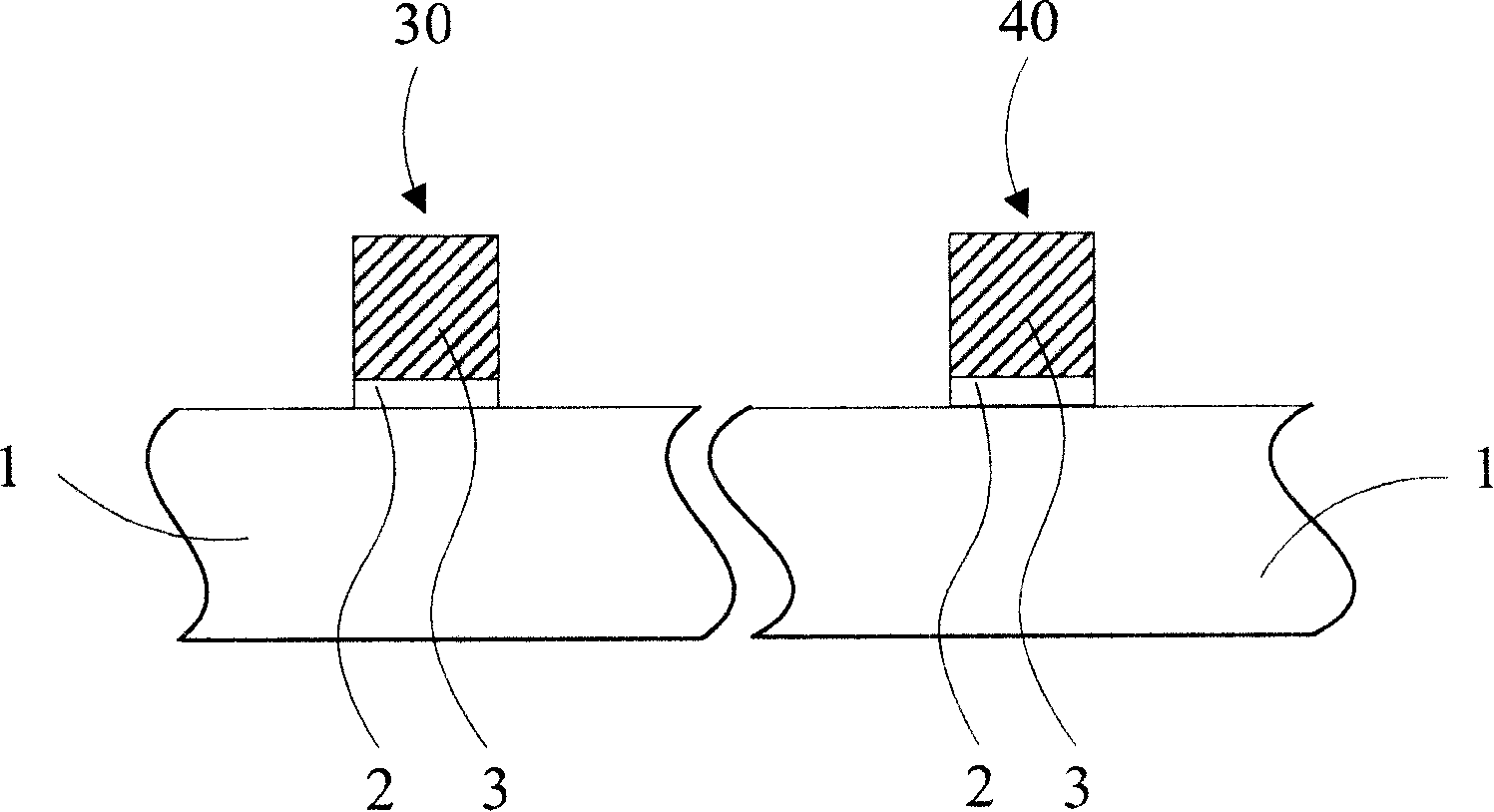

[0029] The present invention provides a method for manufacturing a semiconductor device, which includes the following steps: Picture 12 As shown, a semiconductor substrate is provided. The semiconductor substrate includes a core device area and an input / output device area. A gate dielectric layer and a gate dielectric layer are formed on the semiconductor substrate of the core device area and the input / output device area. The gate S200 on the layer; the gate is used as a mask, the first ion implantation S210 is performed in the semiconductor substrate in the core device area and the input / output device area; rapid thermal annealing is performed in the core device area and the input / output device area Low-doped source and drain regions S220 are formed in the semiconductor substrate on both sides of the gate dielectric layer; spacers S230 are formed in the gate dielectric layer of the core device region and the input / output device region and the sidewalls of the gate; The electrode...

Embodiment 2

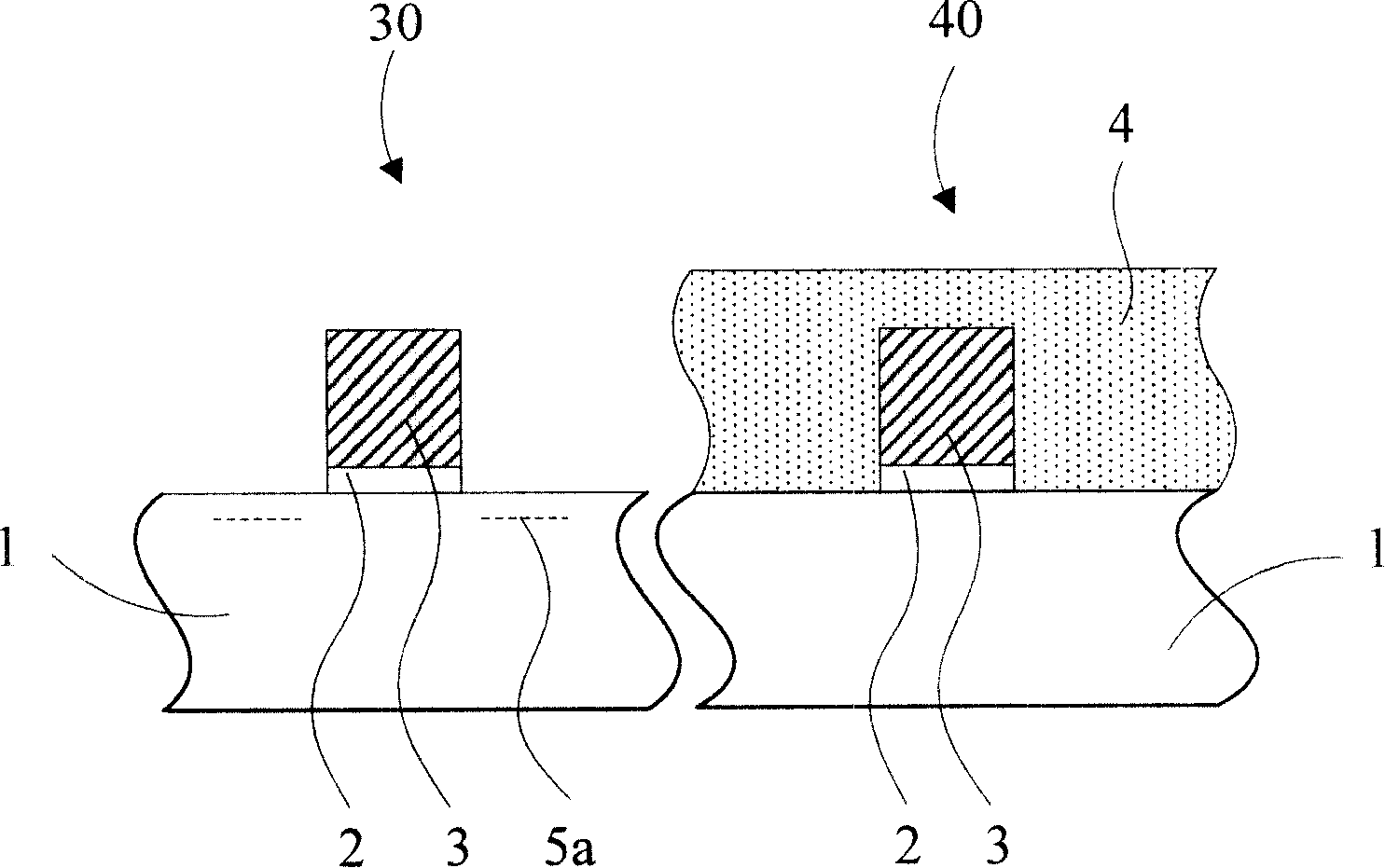

[0044] The present invention also provides a method for manufacturing a semiconductor device, which includes the following steps: Figure 13 As shown, a semiconductor substrate is provided. The semiconductor substrate includes a core device area and an input / output device area. A gate dielectric layer and a gate dielectric layer are formed on the semiconductor substrate of the core device area and the input / output device area. The gate S300 on the layer; using the gate as a mask, perform the first ion implantation S310 in the semiconductor substrate in the core device area and the input / output device area; using the gate as a mask, in the core device area and the input / output device Perform second ion implantation S320 into the semiconductor substrate in the region; perform rapid thermal annealing to form low-doped source and drain regions S330 in the semiconductor substrate on both sides of the gate dielectric layer in the core device region and the input / output device region; Th...

Embodiment 3

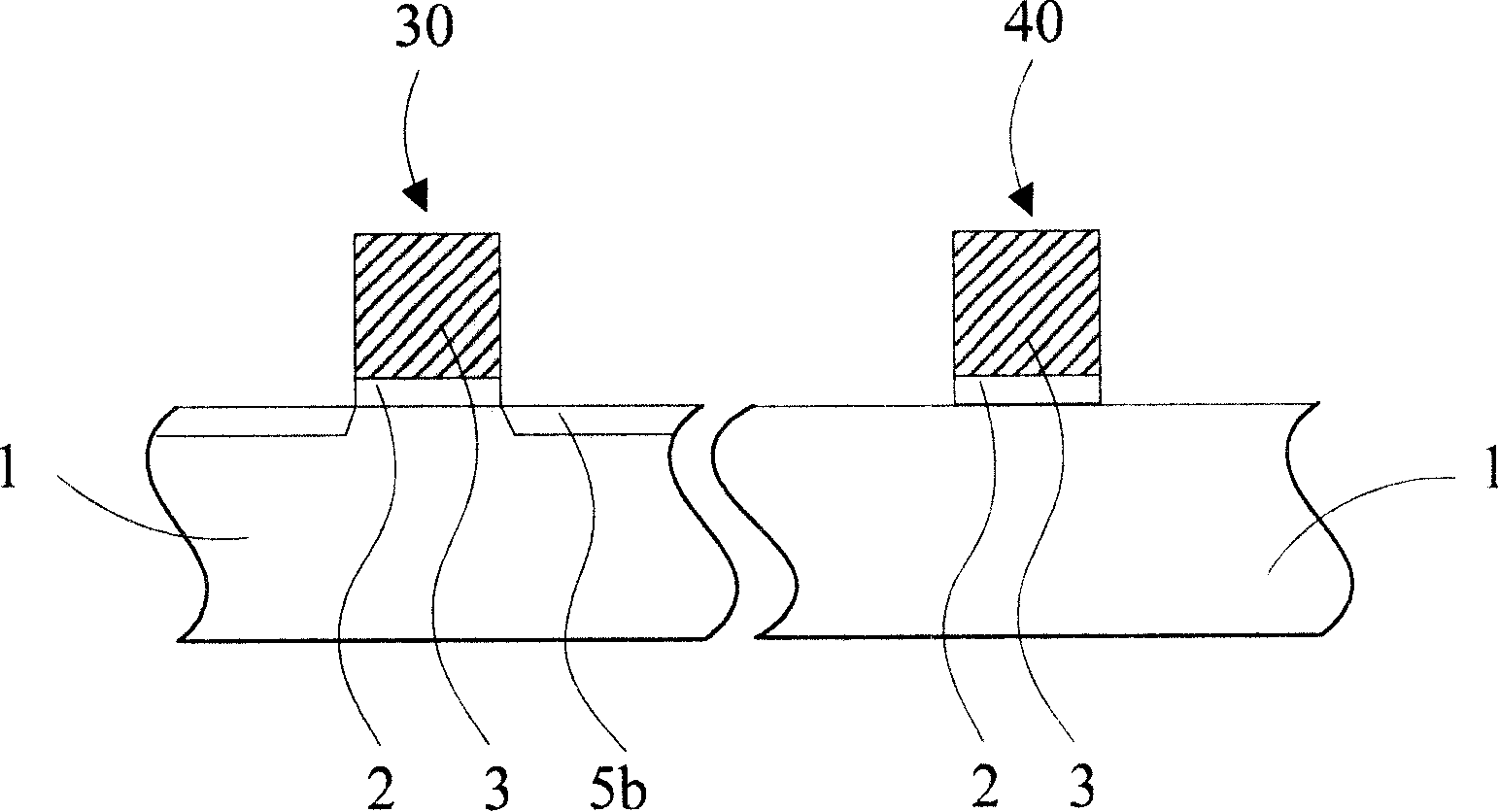

[0050] The present invention also provides a method for manufacturing a semiconductor device, which includes the following steps: Figure 14 As shown, a semiconductor substrate is provided. The semiconductor substrate includes a core device area and an input / output device area. A gate dielectric layer and a gate dielectric layer are formed on the semiconductor substrate of the core device area and the input / output device area. The gate S400 on the layer; using the gate as a mask, perform second ion implantation S410 in the semiconductor substrate in the core device area and the input / output device area; using the gate as a mask, in the core device area and the input / output device Perform first ion implantation S420 into the semiconductor substrate in the region; perform rapid thermal annealing to form low-doped source and drain regions S430 in the semiconductor substrate on both sides of the gate dielectric layer in the core device region and the input / output device region; The ga...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More